Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки изо- браясений.

Целью изобретения является повышение быстродействия устройства.

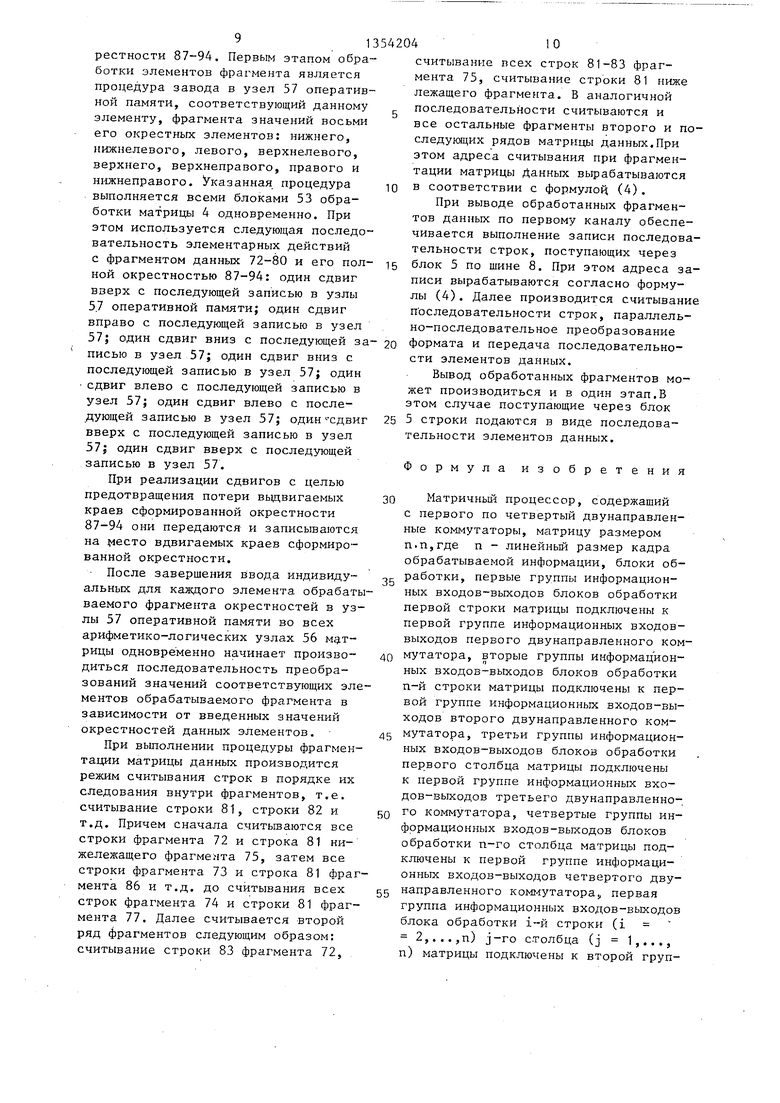

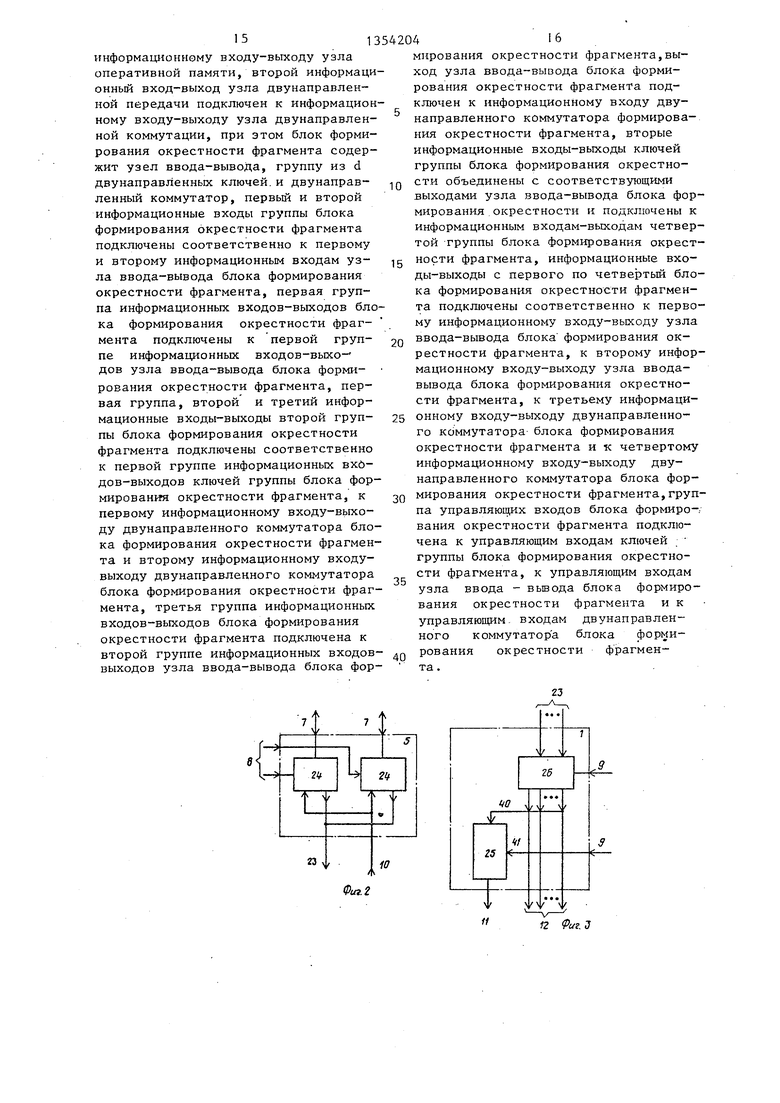

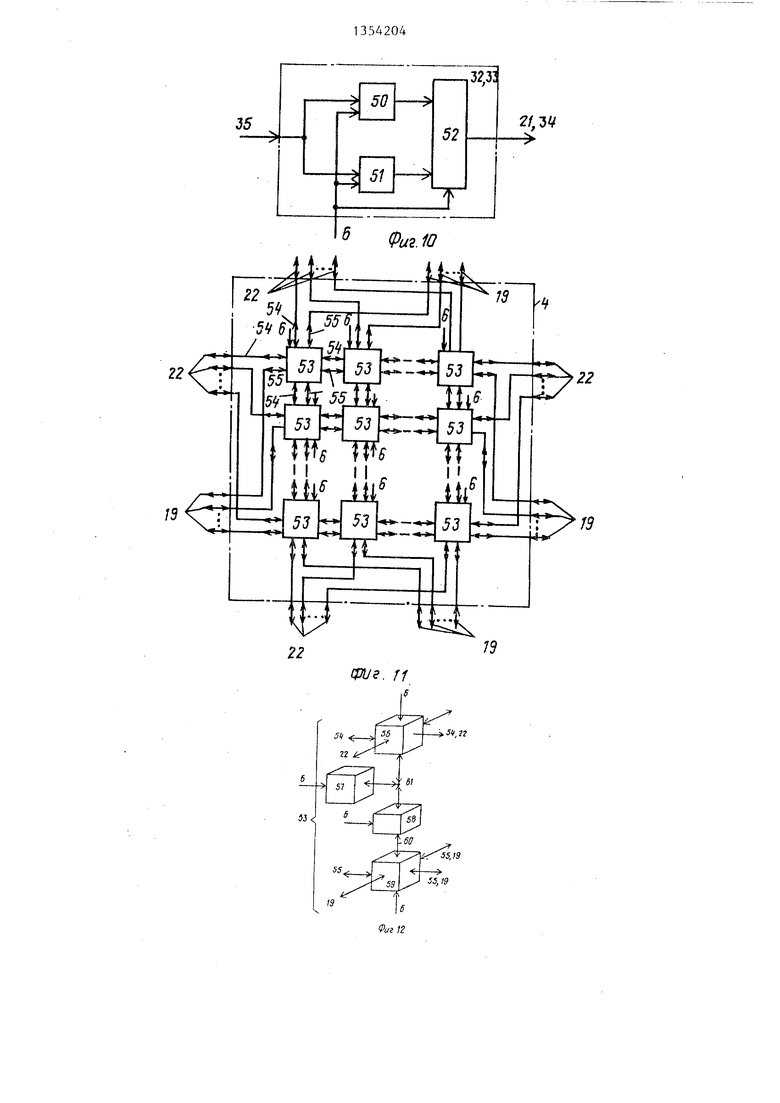

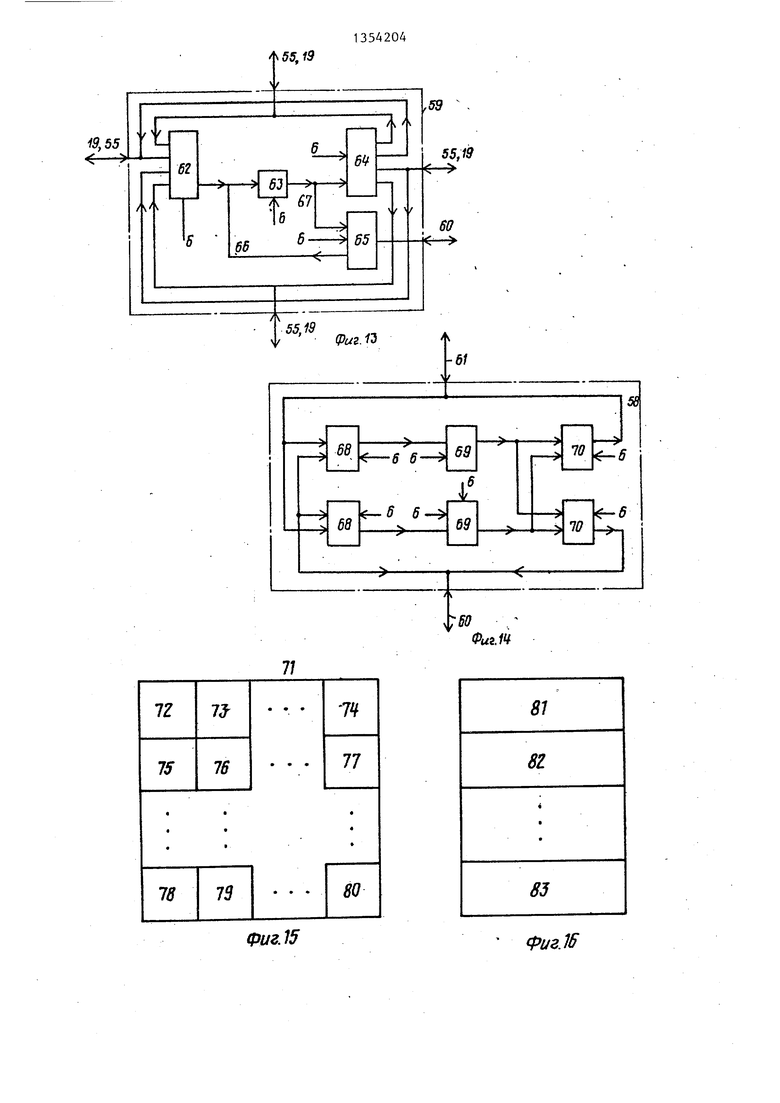

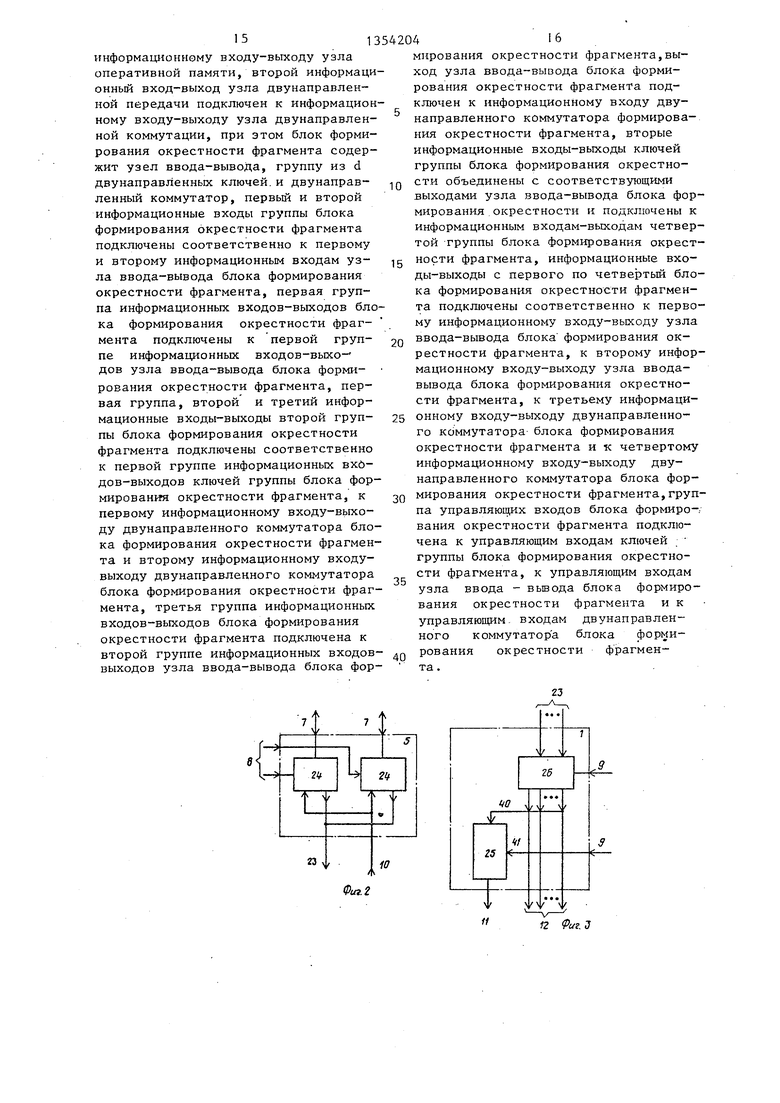

На фиг,1 приведена структурная схема матричного процессора; на фиг. пример построения пятого двунаправленного коммутатора; на фиг.З - структурная схема блока фрагментации матрицы данных; на фиг,4 - структурная схема блока формирования окрестности фрагмента; на фиг.5 - пример построения узла ввода-вывода блока формирования окрестности фрагмента; на фиг.6 - пример построения двунаправленного коммутатора блока формирования окрестности фрагмента; на .фиг.7 - пример построения элемента памяти узла ввода-вывода блока фор- ьшрования окрестности фрагмента; на фиг.8 - пример построения с первого по четвертый двунаправленных коммутаторов; на фиг.9 - пример пестро- . ений приемопередатчика двунаправленного коммутатора; на фиг.10 - пример построения элемента буферной памяти узла ввода-вывода блока формирования окрестности фрагмента; на фиг.11 - структурная схема матрицы блоков обработки матричного процессора; на фиг.12 - структура блока обработки; на фиг.13 - пример построения узла двунаправленной коммутации блока обработки; на фиг.14 - пример построения узла двунаправленной передачи данных блока обработки; на фиг,15 структура исходной матрицы данных; на фиг. 16 и 17 - структу15а фрагмента матрицы данных и ее отдельной строки; на фиг.18 - структура вводимого фрагмента матрицы данных.со сформированной полной окрестностью; на фиг.19 - структура обрабатываемого фрагмента и достоверной части результирующего фрагмента.

Матричньш процессор содержит блок

1фрагментации матрицы данных, блоки

2формирования окрестности фрагмента, с первого по четвертый двунаправленные коммутаторы 3, матрицы 4 блоПример представления структуры матрицы 71 данных форматом 9 Р элеков обработки, пятый двунаправленный коммутатор 5, вход 6 команды обработ-55 ментов данных содержит несколько фраг- ки матричного процессора, инфор маци- ментов 72-80 матрицы данных, каждый онные входы-выходы 7 матричного процессора, вход 8 режима матричного процессора, вход 9 команды ввода-вы.из которых имеет формат cf . Cf ментов данных. Фрагменты 72-80 нумеруются слева направо номером столб

5

0

вода матричного процессора, вход 10 двунаправленного коммутатора, шины 11 и 12 блока фрагментации матрицы данных, информационные входы-выходы 13-22 и выход 23.

Двунаправленный коммутатор 5 содержит два узла 24 приема-передачи. Блок 1 фрагментации матрицы данных содержит сдвигающий регистр 25 и сдвигатель 26. Блок 2 формирования окрестности фрагмента содержит узел 27 ввода-вывода, группу 28 буферных ключей и двунаправленный коммутатор 29. Узел 27 ввода-вывода содержит d элементов, где d - разрядность данных, элемент 30 памяти, ()-й элемент 31 памяти, d элементов 32 буферной памяти, (d+1)-й элемент 33 буферной памяти, выходы 34 и 35,входы-выходы 36.

Двунаправленный коммутатор 29 содержит входы-выходы 37 и 38, мультиплексор 39, триггер 40 и демульти

плексор 41.

Элементы 21 и 22 памяти содержат каждый мультиплексор 42, триггер 43, демультиплексор 44. Двунаправленный коммутатор 3 содержит узлы 45 приема-передачи, информационные входы- выходы 46, причем каждый узел 45 приема-передачи содержит мультиплексор 47, триггер 48 и демультиплексор 49. Элементы 32 и 33 буферной памяти содержат триггеры 50 и 51 и мультиплексор 52,

Матрица 4 блоков обработки содержит блоки 53 обработки, информационные входы-выходы 54 и 55, причем каж- дый блок 53 обработки обрабатывающей матрицы содержит арифметико-логический узел 56, узел 57 оперативной памяти, узел 58 двунаправленной передачи данных, узел 59 двунаправленной коммутации, входы-выходы 60 и 61,при этом узел 59 содержит мультиплексор .62, триггер 63, демультиплексор 64, элемент 65 приема-передачи, входы-выходы 66 н 67.

Узел 58 содержит два мультиплексора 68, два триггера 69 и два мультиплексора 70.

Пример представления структуры матрицы 71 данных форматом 9 Р эле

ментов данных содержит несколько фраг- ментов 72-80 матрицы данных, каждый

ментов данных содержит несколько фраг ментов 72-80 матрицы данных, каждый

.из которых имеет формат cf . Cf ментов данных. Фрагменты 72-80 нумеруются слева направо номером столбца 1 и номером ряда j сверху вниз, Так, первый ряд (j 1) фрагментов 72-74 имеет номера столбцов i от 1 для фрагмента 72 до Ф/Ср для фрагмента 124, второй ряд (j 2) фрагментов 125-127 имеет номера столбцов i также от 1 до ф/С и т.д. Всего в матрице 71 данных содержится Ф/Ч рядов фрагментов, т.е.. j 1,2,, . ., Ф/ц;.

Каждый фрагмент, хранящийся в узле 36 памяти блока 4 содержит cf строк 81-83.

В каждом J-M ряду фрагментов в

матрице 71 содержится (f (-jj-)

строк. Строки в матрице 71 нумеруются и адресуются целыми числами в порядке возрастания слева направо и сверху вниз. Таким образом, строки, образующие данный фрагмент, с номером i, j имеют следующие адреса:

для строки 81 фрагмента i, j

(i-1) + (j-1).P; строки 82 фрагмента i,

(1)

(2)

(3)

В общем виде для К-й сверху строки фрагмента, расположенного в J-M ряду и i-M столбце матрицы данных, имеем

о

(i-1) + (j-1) + (К-1)-Ч .(4)

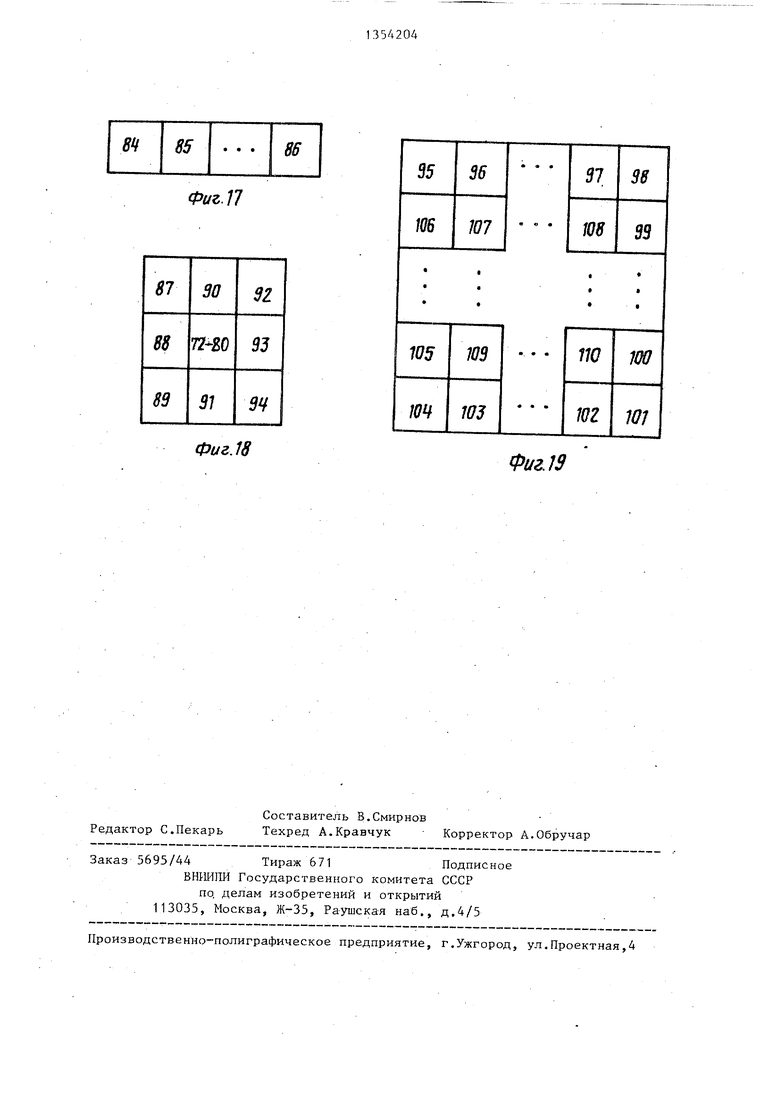

Каждая строка 81-83 содержит gi элементов 84-86 данных.

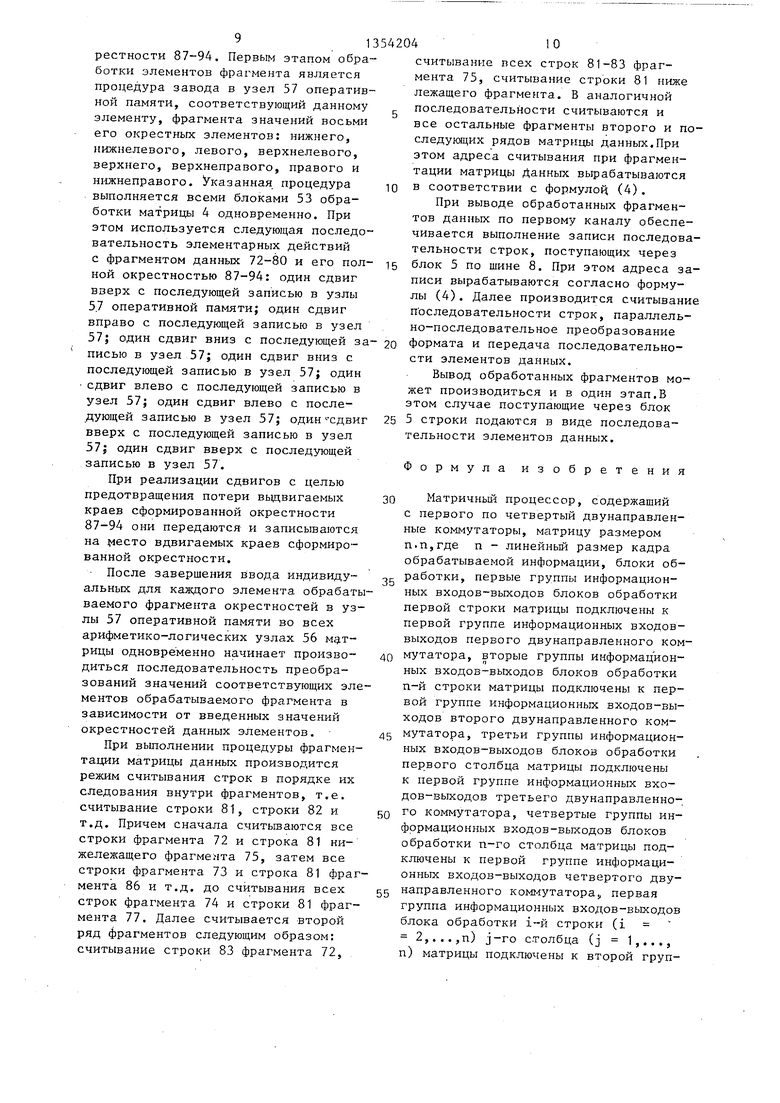

Структура вводимого фрагмента матрицы данных со сформированной полной окрестностью содежрит 72-87 - один из фрагментов матрицы 71 данных. Полная окрестность данного фрагмента содержит верхнелевую 87, левую 88, нижнелевую 89, верхнюю 90, нижнюю 91, верхнеправую 92, правую 93 и нижнеправую 94 окрестности.

В каждой из окрестностей 87, 89, . 92 и 94 содержится по одному элементу данных, а в каждой из окрестностей 88, 90, 91 и 93 - по Ц) элементов данных.

5

10

15

20

25

54204

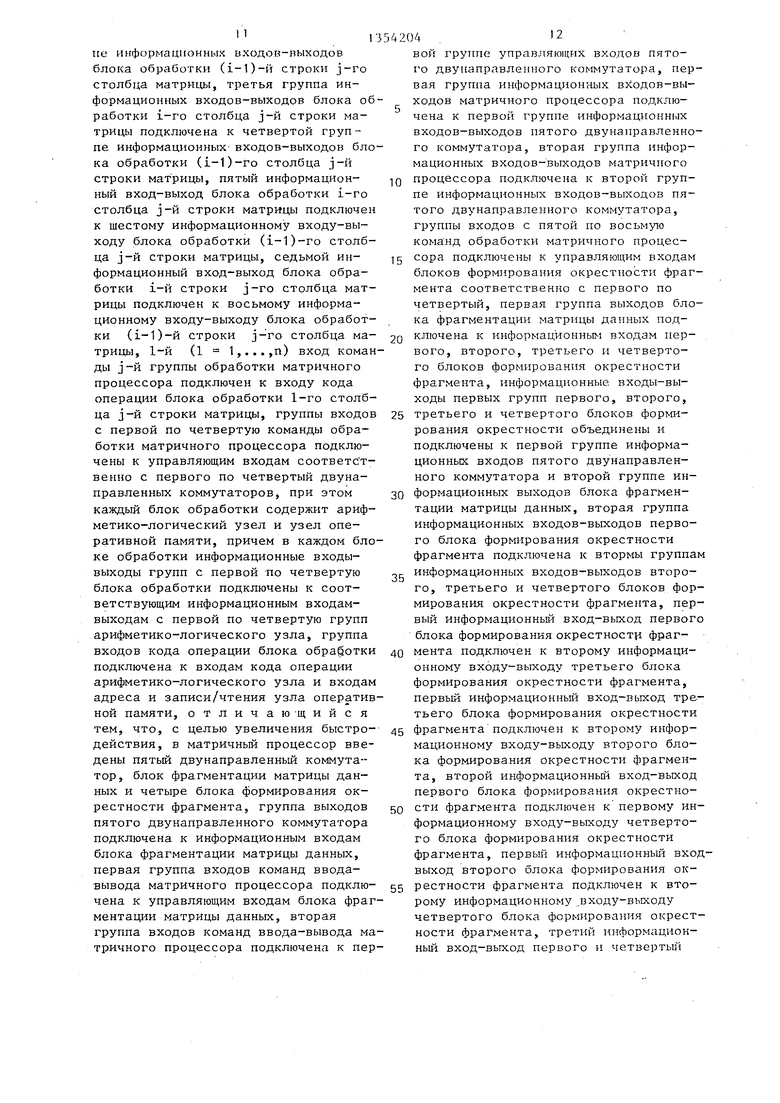

Для элементов 95-106 результат выполнения операции, связанной с анализом полной окрестности, будет недостоверным в связи с отсутствием для этих элементов полной информации об их окрестностных элементах данных. Таким образом, достоверная часть результирующего фрагмента ограничена приграничными элементами 107-110 данных и не включает граничные элементы 95-106 данных.

Матричньш процессор работает следующим образом.

По двум линиям (шины 11 и 15) в соответствующие блоки 2 передаются элементы данных, из которых в указанных блоках 2 производится формирование левой, верхнелевой, нижнелевой, правой, верхнеправой и нижнеправой окрестностей вводимого фрагмента данных.

Сформированные в процессе ввода строк фрагмента его нижняя, верхняя, левая и правая окрестности из соответствующих блоков 2 по шине 21 передаются в соответствующие блоки 3. На этом процесс ввода первого фрагмента совместно с вводом и формированием его полной окрестности завершен. Одновременно с этим можно приступить к процессу ввода в матрицу 4, а также в блоки 2 подготовленных к этому времени второго фрагмента совместно с его полной окрестностью.

Процесс обработки введенного фрагмента данных совместно с его полной окрестностью производится под управлением сигналов, поступающих по линиям шины 6, причем процесс обработки данного (i-ro) фрагмента данных может производиться одновременно с процессом вывода результата обработки предыдущего (i-1) фрагмента и с g процессом ввода последующего (1 + + 1-го) фрагмента совместно с формированием его полной окрестности.

В процессе обработки данного фрагмента граничные элементарные процессоры обрабатывающей матрицы получают полную достоверную информацию об окрестности за счет блоков 2. Ука занные блоки 2 обеспечивают своевременное формирование как верхней.

30

35

40

50

gg нижней, левой и правой окрестностей, поступающих в граничные блоки обработки матрицы 4 по шинам 22, так и верхнелевой, нижнелевой, вофхкепра- вой и нижнеправой окрестностей, поступающих в угловые блоки обработки обрабатывающей матрицы при соответствующих сдвиговых операциях по шинам 18 и 20 через блоки 3 и крайние линии шин 22.

При завершении обработки данного фрагмента с его полной окрестностью образуется результирующий фрагмент, формат достоверной части которого равен формату матрицы 4, т.е. формату исходного фрагмента. При этом после завершения процесса обработки данного фрагмента можно без задержки производить обработку введенного к этому времени следующего фрагмента совместно с его полной окрестностью.

Процесс вывода результирующего фрагмента данных из матрицы 4 производится, построчно по соответствующей шине 19 через один из блоков 2.

Работа блока 1 заключается в преобразовании последовательности поступающих строк 81-83 фрагментов 72 матрицы 71 данных в последовательность выставляемых на шины 11 и 12 строк фрагмента матрицы данных 72-80 в совокупности с полной окрестностью 87-94.

При поступлении очередной строки данных текущего i-ro фрагмента происходит сдвиг содержимого сдвигателя 26 и регистра 25, при котором на шину 1 2 выставляется соответствуюо ая строка предыдущего (i-1-го) фрагмента, на первую линию шины 11 выставляется элемент данных 86 соответствующей строки (i-2-го) фрагмента, представляющий собой верхнелевую, левую или нижнелевую окрестность (i-l)-ro фрагмента. Сдвиговый регистр 25 реализует задержку элементов данных 86 на два фрагмента, образуя тем самым верхнелевую 87, левую 88 и нижнелевую 89 окрестности. Сдвигатель 26 реализует задержку строк 81-83 на один фрагмент, образуя верхнюю 90 окрестность, фраг- ментные строки 81-83 и нгокшою окрестность 91.

Работа блоков 2 заключается в выполнении следующих функций: а) передача строк 81-83 вводимого по шинам 12 и 14 фрагмента выборочно на одну из четырех сторон матрищ. 4; Jфopмиpoвaниe полной окрестности 87 - 94 для вводимого фрагмента данных на основании информации об окрестности, поступающей по шинам 11, 15 и

12, 14; Ь) формирование, хранение и передача верхнелевой 87, } ижнеле- вой 89, верхнеправой 92 и нижнеправой 94 окрестностей соответствующим угловым блоком обработки матрицы 4 в процессе обработки введенного фрагмента данных; ) передача строк 81 - 83 выводимого фрагмента данных выборочно по одной из шин 19, т.е. с одной из четырех сторон обрабатьшающей матрицы 4; 9) передача строк данных с одной из сторон обрабатывающей матрицы 4 выборочно на любую другую

сторону матрицы 4; е ) совмещение во времени операции формирования полной окрестности 87-94 и строк 81-83 (i+1)-ro вводимого фрагмента, а также операции вывода (i-1)-ro обработанного фрагмента с операцией обработки i-ro текущего фрагмента данных.

Строки 81-83 вводимого фрагмента по шинам 12 и 14 поступают на входы- выходы узлов 27 четырех блоков 2,

один из которых передает строки фрагмента по шине 19 на определенную сторону матрицы 4.

В определенные моменты времени по шинам 12 и 14 на вторые входы-выходы узлов 27 поступают нижняя 91 и верхняя 90 окрестности вводимого фрагмента.

Поступающие одновременно с вводом верхней 90 и нижней 91 окрестностей

по шинам 11 и 15 верхнелевая 87, нижнелевая 89, верхнеправая 92 и нижнеправая 94 окрестности через элементы 31 соответствующих четырех узлов 42 ввода-вывода подаются по линиям 35

на соответствующие элементы 31 и

далее по линиям 34 - в соответствующие триггеры 40.

Поступающие по шинам 11 и 15 в процессе ввода строк 81-83 фрагмента

элементы левой 88 и правой 93 окрестностей через элементы 31- двух соответствующих узлов ввода-вывода подаются на входы-выходы 17 соответствующих блоков 2 до момента заполнения

всех элементов 30 соответственно элементами левой 88 и правой 83 окрестностей.

Таким образом, в процессе ввода строк 81-83 фрагмента в матрицу 4 в

блоках 2 формируется полная окрестность 87-94, необходимая и достаточная для того, без задержки нй- чать процесс обработки первого введенного фрагмента 72, до ввода остальных фрагментов 73-80 матрицы данных .

После завершения процесса формирования и перехода к режиму хранения и передачи полной окрестности вводимог фрагмента можно одновременно с началом процесса его обработки приступит к процессу ввода следующего фрагмента и формирования его окрестности.К моменту окончания процесса обработки данного фрагмента окрестность следующего фрагмента сформирована и может быть приведена в режим хранения и передачи, т.е. записана в блоки 3 и триггеры 40 без задержки на один так Такая возможность реализуется за ,счет наличия в элементах 32 памяти двух триггеров 50 и 51 и мультиплексора 52.

Сформированные в блоках 2 и переданные в соответ ствующие блоки 3 верхняя 90, нижняя 91, левая 88 и правая 93 окрестности поступают в матрицу 4 по четырем шинам 22.

Вывод обработанного фрагмента из матрицы 4 может производиться с любой из ее четырех сторон по соответствующей шине 19 через элементы 30 памяти.

Работа блоков 3 заключается в хранении и двунаправленной передаче данных по шинам 21 и 22, а также в двунаправленных сдвигах данных и их передаче по шинам 18 и 20. При этом Используются узлы 45 приема-передачи и линии 46 связи.

Передача содержимого одного из блоков 3 в другой реализуется по одной из шин 21, коммутатору 28 одного из блоков 2, параллельной шине 13, через коммутатор 28 другого блока 2 и по другой шине 21.

Работа матрицы 4 заключается в вводе подлежащего обработке, выводе обработанного и обработке введенного в нее фрагмента матрицы данных 72-80 с использованием информации об его полной окрестности 87-94. Под обработкой фрагмента данных понимается выполнение над каждым его элементом операции, связанной с анализом окрестности, состоящей из восьми смежных элементов.

Линии. 54 связи служат для связи блоков 53 обработки с соответствующими триггерами 48, а также для связи между собой в режиме обработки. Линии 55 связи служат для связи бло

0

5

0

ков обработки между собой и шиной 19 в режиме ввода-вывода фрагментов данных .

Поступающие по шине 19 строки вводимого фрагмента данных подаются по соответствующим линиям 55 связи на определенный крайний ряд узлов 59 буферной памяти. При этом поступление каждой очередной строки вводимого фрагмента сопровождается сдвигом всех предшествующих строк на один шаг. Таким образом, построчно вводится весь фрагмент, подлежащий обр.аботке. Узел 59 позволяет вводить и выводить элементы данных из триггера 63 по любому из четырех направлений за счет мультиплексора 62,имеющего выход с третьим состоянием, и демультиплексора 64. После ввода всего фрагмента в триггеры 59 производится параллельная передача всех элементов фрагмента из триггеров 63 по линиям 67, через приемопередатчики 5 65, линии 60 на вторые входы-вьпсоды буферных ячеек 58, через мультиплексоры 68 на триггеры 69, где фрагмент находится в режиме хранения до момента окончания обработки в арифметико-логических узлах 56 фрагмента, введенного ранее. После завершения обработки ранее введенного фрагмента его элементы данных передаются по линиям 61 и через мультиплексоры 68 записываются в триггеры 69. После этого без задержки введенный текущий фрагмент из триггеров 69 через мультиплексоры 70, шину 61 поступает в арифметико-логические устройства.56 и в узел 57 оперативной памяти, что позволяет приступить к непосредственной обработке этого фрагмента.

В то же время обработанный ранее фрагмент из триггеров 69 выводится 5 через мультиплексоры 70, линии 60, приемопередатчики 65, линии 66 в триггеры 63. Далее по соответствующим линиям 55 и шине 19 производится построчный вывод обработанного Q фрагмента из матрицы 4, после чего можно без задержки приступать к вводу в матрицу 4 очередного фрагмента данных.

Тем временем производится процесс g обработки введенного в арифметико- логические устройства 56 и узел 57 оперативной памяти текущего фрагмента данных из числа 71-80 с использо- ванием сформированной полной его ок0

5

0

рестности 87-94, Первым этапом обработки элементов фрагмента является процедура завода в узел 57 оперативной памяти, соответствующий данному элементу, фрагмента значений восьми его окрестных элементов: нижнего, иижнелевого, левого, верхнелевого, верхнего, верхнеправого, правого и нижнеправого. Указанная процедура выполняется всеми блоками 53 обработки матрицы 4 одновременно. При этом используется следующая последовательность элементарных действий с фрагментом данных 72-80 и его полной окрестностью 87-94: один сдвиг вверх с последующей записью в узлы 57 оперативной памяти; один сдвиг вправо с последующей записью в узел 57; один сдвиг вниз с последующей записью в узел 57; один сдвиг вниз с последующей записью в узел 57; один сдвиг влево с последующей записью в узел 57; один сдвиг влево с последующей записью в узел 57; один сдвиг вверх с последующей записью в узел 57; один сдвиг вверх с последующей записью в узел 57.

При реализации сдвигов с целью предотвращения потери выдвигаемых краев сформированной окрестности 87-94 они передаются и записываются на lecTo вдвигаемых краев сформированной окрестности. После завершения ввода индивидуальных для каждого элемента обрабатываемого фрагмента окрестностей в узы 57 оперативной памяти во всех арифметико-логических узлах. 56 мд.т- ицы одновременно начинает производиться последовательность преобразований значений соответствующих элементов обрабатываемого фрагмента в зависимости от введенных значений окрестностей данных элементов.

При вьтолнении процедуры фрагментации матрицы данных производится режим считывания строк в порядке их следования внутри фрагментов, т.е. считывание строки 81, строки 82 и т.д. Причем сначала считываются все строки фрагмента 72 и строка 81 ниележащего фрагмента 75, затем все строки фрагмента 73 и строка 81 фрагента 86 и т.д. до считывания всех строк фрагмента 74 и строки 81 фрагента 77. Далее считывается второй яд фрагментов следующим образом: считывание строки 83 фрагмента 72,

считывание всех строк 81-83 фрагмента 75, считывание строки 81 ниже лежащего фрагмента. В аналогичной последовательности считываются и

все остальные фрагменты второго и последующих рядов матрицы данных.При этом адреса считывания при фрагментации матрицы Данных вырабатываются

в соответствии с формулой (4).

При выводе обработанных фрагментов данных по первому каналу обеспечивается выполнение записи последовательности строк, поступающих через

блок 5 по шине 8. При этом адреса записи вырабатываются согласно формулы (4). Далее производится считывание последовательности строк, параллельно-последовательное преобразование

формата и передача последовательности элементов данных.

Вывод обработанных фрагментов может производиться и в один этап,В этом случае поступающие через блок

5 строки подаются в виде последовательности элементов данных.

Формула изобретения

Матричный процессор, содержащий с первого по четвертый двунаправленные коммутаторы, матрицу размером п.п,где п - линейный размер кадра обрабатываемой информации, блоки обработки, первые группы информационных входов-выходов блоков обработки первой строки матрицы подключены к первой группе информационных входов- выходов первого двунаправленного коммутатора, вторые группы информационных входов-выходов блоков обработки п-й строки матрицы подключены к первой группе информационных входов-выходов второго двунаправленного коммутатора, третьи группы информационных входов-выходов блоков обработки первого столбца матрицы подключены к первой группе информационных входов-выходов третьего двунаправленного коммутатора, четвертые группы информационных входов-выходов блоков обработки п-го столбца матрицы подключены к первой группе информационных входов-выходов четвертого двунаправленного коммутатора,, первая группа информационных входов-выходов блока обработки i-й строки (i 2,.,.,п) j-ro столбца (j 1,..., п) матрицы подключены к второй груп

. 1

пе информационных входог: -пыходов блока обработки (1-1)-н строки j-ro столбца матрицы, третья группа информационных входов-выходов блока обработки i-ro столбца j-й строки матрицы подключена к четвертой группе информационных- входов-выходов блока обработки (L-l)-ro столбца j-й строки матрицы, пятый информационный вход-выход блока обработки i-ro столбца j-й строки матрицы подключен к шестому информационному входу-выходу блока обработки (i-1)-ro столбца j-й строки матрицы, седьмой информационный вход-выход блока обработки i-fi строки j-ro столбца матрицы подключен к восьмому информационному входу-выходу блока обработки (1-1)-й строки j-ro столбца матрицы, 1-й (1 1,... ,п) вход команды j-и группы обработки матричного процессора подключен к входу кода операции блока обработки 1-го столбца J-и строки матрицы, группы входов с первой по четвертую команды обработки матричного процессора подключены к управляющим входам соответс т- венно с первого по четвертый двунаправленных коммутаторов, при этом каждый блок обработки содержит арифметико-логический узел и узел оперативной памяти, причем в каждом блоке обработки информационные входы- выходы групп с первой по четвертую блока обработки подключены к соответствующим информационным входам- выходам с первой по четвертую групп арифметико-логического узла, группа входов кода операции блока обработки подключена к входам кода операции арифметико-логического узла и входам адреса и записи/чтения узла оперативной памяти, отличаю-щийся тем, что, с целью увеличения быстродействия, в матричньм процессор введены пятый двунаправленный коммутатор, блок фрагментации матрицы данных и четыре блока формирования окрестности фрагмента, группа выходов пятого двунаправленного коммутатора подключена к информационным входам блока фрагментации матрицы данных, первая группа входов команд ввода- вывода матричного процессора подключена к управляющим входам блока фрагментации матрицы данных, вторая группа входов команд ввода-вывода матричного процессора подключена к пер4204 .12

вой группе управляющих входов пятого двунаправленного коммутатора, первая группа информационных входов-выходов матричного процессора подклю- р)

чена к первой группе информационных входов-выходов пятого двунаправленного коммутатора, вторая группа информационных входов-выходов матричного

0 процессора подключена к второй группе информационных входов-выходов пятого двунаправленного коммутатора, группы входов с пятой по восьмую команд обработки матричного процес15 сора подключены к управляющим входам блоков формирования окрестности фрагмента соответственно с первого по четвертый, первая группа выходов блока фрагментации матрицы данных подQ ключена к информационным входам первого, второго, третьего и четвертого блоков формирования окрестности фрагмента, информационные входы-выходы первых групп первого, второго,

25 третьего и четвертого блоков форм-i- рования окрестности объединены и подключены к первой группе информационных входов пятого двунаправленного коммутатора и второй группе ин30 формационных выходов блока фрагментации матрицы данных, вторая группа информационных входов-выходов первого блока формирования окрестности фрагмента подключена к втормы группам информационных входов-выходов второго, третьего и четвертого блоков формирования окрестности фрагмента, первый информационньй вход-выход первого блока формирования окрестности фраг0 мента подключен к второму информационному входу-выходу третьего блока формирования окрестности фрагмента, первый информационньй вход-выход третьего блока формирования окрестности

5 фрагмента подключен к второму информационному входу-выходу второго блока формирования окрестности фрагмента, второй информационньй вход-выход первого блока формирования окрестно0 сти фрагмента подключен к первому информационному входу-выходу четвертого блока формирования окрестности фрагмента, первый информационньй вход- выход второго блока формирования ок5 рестности фрагмента подключен к второму информационному входу-выходу четвертого блока формирования окрестности фрагмента, третий информационньй вход-выход первого и четвертьй

35

информационный вход-выход четвертого .блоков формирования окрестности фрагмента подключены соответственно к первому и второму информационным входам-выходам первого двунаправленного коммутатора, четвертый информационный вход-выход третьего и третий информациоиньй вход-выход второго блоков формирования окрестности фраг мента подключены соответственно к первому и второму информационным входам-выходам второго двунаправленного коммутатора, третий информационный вход-выход третьего и четвертый ин- формационньш вход-выход первого блоков формирования окрестности фрагмен та подключены соответственно к второму и первому информационным входам выходам третьего двунаправленного коммутатора, третий информационный вход-выход чевертого и четвертый и.н- формационный вход-выход второго блоков формирования окрестности фрагмента подключены соответственно к пе вому и второму информационным входам выходам четвертого двунаправленного коммутатора, j-й информационный вход вьгход третьей группы первого блока формирования окрестности фрагмента подключен к пятому информацоинному входу-выходу блока обработки первого столбца j-й строки матрицы, 1-й информационный вход-выход третьей группы второго блока формирования окрестности фрагмента подключен к шестому информационному входу-выходу блока обработки п-го столбца 1-й строки матрицы, j-и информационный вход-выход третьей группы четвертого блока формирования окрестности фрагмента подключен к седьмому информационному входу-выходу блока обработки первой строки j-ro столбца матрицы, 1-й информационный вход-выход тре- тьей группы третьего блока формирования окрестности фрагмента подключен к восьмому информационному входу выходу блока обработки 1-го столбца п-й строки матрицы, четвертая группа информационных ,входов-выходов первого блока формирования окрестности фрагмента подключена к второй группе информационных входов-выходов третьего двунаправленного коммутатора, четвертая группа информационных входов-выходов второго блока формирования окрестности фрагмента подключена к второй группе информационных вхо

5 0 5 о Q 5 g

5

дов-выходов четвертого двунаправленного коммутатора, четвертая группа информационных входов-выходов третьего блока формирования окрестности фрагмента подключена к второй группе информационных входов-выходов второго двунаправленного коммутатора, четвертая группа Информационных входов- выходов четвертого блока формирования окрестности фрагмента подключена к второй группе информационных входов- выходов первого двунаправленного коммутатора, при этом блок фрагментации матрицы данных содержит сдвигающий регистр и сдвигатель, информационные входы блока фрагментации матрицы данных с первого по d-й, где d - разрядность данных, подключены к информационным входам с первого по d-й сдвигателя,.при этом первый информационный вход сдвигателя соединен с первым выходом первой группы блока фрагме тации матрицы данных, первая и вторая группы управляющих входов блока фрагментации матрицы данных подключены соответственно к входам управления сдвигающего регистра и сдвигателя, информационный выход сдвигающего регистра подключен к второму выходу первой группы блока фрагментации матрицы данных, информационные выходы с первого по (d-1)-й сдвигателя подключены к вы- ходам с первого по (ё-1)-й второй группы блока фрагментации матрицы данных, d-й информационньй выход сдвигателя подключен к информационному входу сдвигающего регистра и к d-му выходу второй группы блока фрагментации матрицы данных,при этом в блок обработки дополнительно введены узел двунаправленной коммутации и узел двунаправленной передачи данных, причем в каждом блоке обработки управляющие входы блока обработки подключены к управляющим эхо- дам узла двунаправленной коммутации и узла двунаправленной передачи дан-, ных, информационные входы-выходы пятый, шестой, седьмой и восьмой блока обработки подключены соответственно к информационным входам-выходам первому, второму, третьему и четвертому узла двунаправленной коммутации, информационный вход-выход арифметико-логического узла подключен к первому информационному входу-выходу узла двунаправленной передачи и к

информационному входу-выходу узла оперативной памяти, второй информационный вход-выход узла двунаправленной передачи подключен к информационному входу-выходу узла двунаправленной коммутации, при этом блок формирования окрестности фрагмента содержит узел ввода-выБоДа, группу из d двунаправленных ключей, и двунаправленный коммутатор, первый и второй информационные входы группы блока формирования окрестности фрагмента подключены соответственно к первому и второму информационным входам узла ввода-вывода блока формирования окрестности фрагмента, первая группа информационных входов-выходов блока формирования окрестности фрагмента подключены к первой группе информационных входов-выхо- дов узла ввода-вывода блока форми- рования окрестности фрагмента, первая группа, второй и третий информационные входы-выходы второй группы блока формирования окрестности фрагмента подключены соответственно к первой группе информационных вхй- дов-выходов ключей группы блока формирования окрестности фрагмента, к первому информационному входу-выходу двунаправленного коммутатора блока формирования окрестности фрагмента и второму информационному входу- выходу двунаправленного коммутатора блока формирования окрестности фрагмента, третья группа информационных входов-выходов блока формирования окрестности фрагмента подключена к второй группе информационных входов- выходов узла ввода-вывода блока фор

5

0

5

0

5

0

мпрования окрестности фрагмента,выход узла ввода-вывода блока формирования окрестности фрагмента подключен к информационному входу двунаправленного коммутатора формирования окрестности фрагмента, вторые информационные входы-выходы ключей группы блока формирования окрестности объединены с соответству5ощими выходами узла ввода-вывода блока формирования окрестности и подключены к информационным входам-выходам четвертой группы блока формирования окрестности фрагмента, информационные входы-выходы с первого по четвертый блока формирования окрестности фрагмента подключены соответственно к первому информационному входу-выходу узла ввода-вывода блока формирования окрестности фрагмента, к второму информационному входу-выходу узла ввода- вывода блока формирования окрестности фрагмента, к третьему информационному входу-выходу двунаправленного коммутатора- блока формирования окрестности фрагмента и к четвертому информационному входу-выходу двунаправленного коммутатора блока формирования окрестности фрагмента,группа управляюир1х входов блока формиро-/ вания окрестности фрагмента подключена к управляющим входам ключей группы блока формирования окрестности фрагмента, к управляющим входам узла ввода - вывода блока формирования окрестности фрагмента и к управляющим, входам двунаправленного коммутатора блока формирования окрестности фрагмента..

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный процессор | 1987 |

|

SU1534466A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Ассоциативный матричный процессор | 1990 |

|

SU1795467A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| МНОГОПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2012 |

|

RU2502126C1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

Изобретение относится к области вычислительной техники и может быть использовано для цифровой обработки изображений. Цель изобретения - повьшение быстродействия устройства. Поставленная цель достигается тем, что матричный процессор содержит блок 1 фрагментации матрицы данных, блок 2 формирования окрестности фрагмента, коммутатор 3, матрицу 4 блоков обработки, двунаправленный коммутатор 5. Повышение быстродействия матричного процессора обеспечивается за счет совмещения операций обработки фрагментов изображения при размерах изображения, больиих линейных размеров матрицы блоков обработки. 19 ил. 9

фи&.

20

Л /

3V

фие. 5

39

У

/V

38

f

Фиг. 5

21

Л9

4i

щ

Л l 6

1tt,15

п

го

V

19,П

35

А 1/ М/

2222

. /N

Ъ5,/5

to. 7

vZ2

-

l2f ф2/

5

5

.J

fe

ф2/

Й/г.5

Фи2. Ю

Фие. л

«, п

Фиг.15

fpt/e.l5

Фиг. П

Фиг.18

Редактор С.Пекарь

Составитель В.Смирнов

Техред А.Кравчук Корректор А.Обручар

Заказ 5695/44 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по, делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг. 19

Авторы

Даты

1987-11-23—Публикация

1985-11-26—Подача