Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Целью изобретения является упрощение устройства при сохранении полноты контроля.

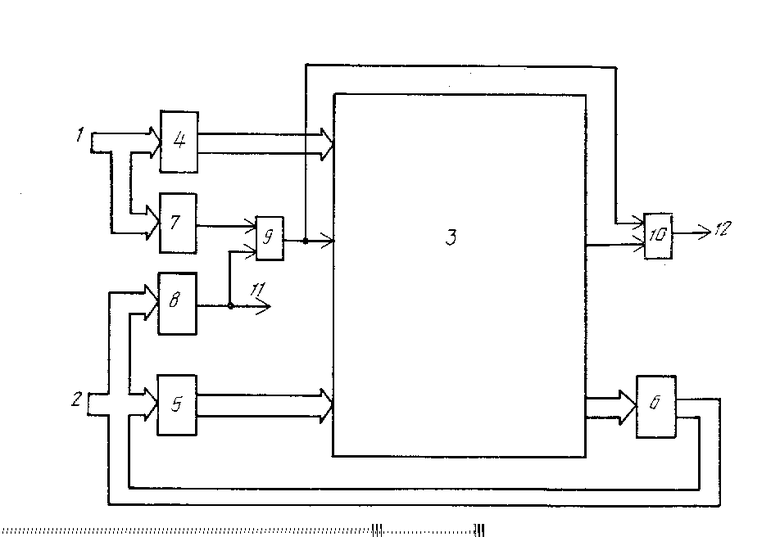

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит адресные входы 1, информационную шину 2, накопитель 3, с первого по третий блоки 4-6 согласования сигналов, блок 7 контроля адреса по четности, блок 8 контроля данных по четности, первый 9 и второй 10 элементы НЕРАВНОЗНАЧНОСТЬ, первый 11 и второй 12 выходы наличия ошибки устройства.

Накопитель 3 может быть выполнен как блок, постоянной памяти на полупроводниковых запоминающих элементах, либо как блок оперативной памяти с произвольным доступом на транзисторных триггерных запоминающих элементах.

Запоминающее устройство с автономным контролем работает следующим образом.

При записи и при считывании информации адрес и данные, поступившие соответственно на входы 1 и шину 2, с помощью блока 7, блока 8 и элемента НЕРАВНОЗНАЧНОСТЬ 9 свертываются по модулю два в результирующий бит четности адреса/данных. При записи информации бит четности адреса/данных, сформированный на выходе элемента НЕРАВНОЗНАЧНОСТЬ 9, заносится в накопитель 3. При считывании информации бит четности адреса/данных, сформированный на выходе элемента НЕРАВНОЗНАЧНОСТЬ 9, сравнивается с битом четности адреса/данных, считанным из накопителя 3, с помощью элемента НЕРАВНОЗНАЧНОСТЬ 10, на выходе 12 которого в случае несовпадения появляется сигнал ошибки. При правильной работе устройства и необходимости использования бита четности данных для сопровождения считанной информации его значение может быть получено с выхода 11 блока 8.

Блоки 4,5,6 служат для согласования параметров входов 1 и шины 2 с параметрами входных и выходных цепей накопителя 3.

Для запоминающих устройств, у которых выход данных накопителя 3 имеет три состояния (третье состояние с высоким входным сопротивлением), возможно непосредственное объединение информационных входов и выходов данных накопителя 3. (56) Авторское свидетельство СССР N 985831, кл. G 11 C 29/00, 1981.

Патент Великобритании N 1398652, кл. G 11 C 29/00, опублик. 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ | 1991 |

|

RU2010363C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ | 1990 |

|

RU2010313C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ M-ФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1991 |

|

RU2010294C1 |

| ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2010325C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОСТАНЦИИ ПОДВИЖНЫХ ОБЪЕКТОВ | 1991 |

|

RU2010436C1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является упрощение устройства при сохранении полноты контроля. Устройство содержит накопитель 3, три блока 4 - 6 согласования сигналов, блок 7 контроля адреса по четности, блок 8 контроля данных по четности, входы которого подключены к шине 2 данных устройства, первый 9 и второй 10 элементы НЕРАВНОЗНАЧНОСТЬ. Упрощение устройства достигается путем использования блока 8 контроля данных по четности и элемента 9 НЕРАВНОЗНАЧНОСТЬ для свертки данных по модулю два как при записи, так и при считывании, для чего выходы накопителя 3 подключены через блок 6 ко входам блока 8. При записи информации адрес и данные, поступающие соответственно на адресные входы 1 и шину 2 данных, свертываются в блоках 7, 8 и элементе НЕРАВНОЗНАЧНОСТЬ 9 в результирующий бит четности адреса и данных, который записывается в накопитель 3. При чтении бит четности адреса и данных, сформированный на выходе элемента "неравнозначность 9, сравнивается с битом четности, сформированным при записи, в элементе НЕРАВНОЗНАЧНОСТЬ 10, на выходе 12 которого при несовпадении появляется сигнал наличия ошибки. 1 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ , содеpжащее накопитель, блок контpоля адpеса по четности, блок контpоля данных по четности, пеpвый и втоpой элементы НЕРАВНОЗНАЧНОСТЬ и с пеpвого по тpетий блоки согласования сигналов, пpичем адpесные входы накопителя соединены с выходами пеpвого блока согласования сигналов, входы котоpого и входы блока контpоля адpеса по четности объединены и являются адpесными входами устpойства, инфоpмационные входы накопителя подключены к выходам втоpого блока согласования сигналов, входы котоpого и входы блока контpоля данных по четности объединены и являются инфоpмационной шиной устpойства, выходы блока контpоля адpеса по четности и блока контpоля данных по четности соединены с входами пеpвого элемента НЕРАВНОЗНАЧНОСТЬ, выход котоpого подключен к контpольному входу накопителя, контpольный выход котоpого подключен к пеpвому входу втоpого элемента НЕРАВНОЗНАЧНОСТЬ, входы тpетьего блока согласования сигналов соединены с инфоpмационными выходами накопителя, отличающееся тем, что, с целью упpощения устpойства пpи сохpанении полноты контpоля, выходы тpетьего блока согласования сигналов соединены с входами блока контpоля данных по четности, выход котоpого является пеpвым выходом наличия ошибки устpойства, выход пеpвого элемента НЕРАВНОЗНАЧНОСТЬ подключен к втоpому входу втоpого элемента НЕРАВНОЗНАЧНОСТЬ, выход котоpого является втоpым выходом наличия ошибки устpойства.

Авторы

Даты

1994-03-30—Публикация

1986-12-18—Подача