Изобретение относится к вычислительной технике, в частности к модульным конвейерным процессорам, и может быть использовано для обработки данных физико-математических экспериментов, для научных расчетов, требующих высокой производительности и большого объема памяти.

Известен конвейерный процессор, содержащий коммутатор записи, выход которого соединен с входом памяти, выход которой соединен с входом коммутатора чтения, коммутатор адресов и управления памятью, выходы которого соединены с входом памяти и коммутатора чтения, блок управления, подключенный к входу арифметико-логического устройства [1].

Однако это устройство не отличается высокой надежностью и высокой производительностью.

По технической сущности наиболее близким к предлагаемому является конвейерный процессор, содержащий коммутатор записи, выход которого соединен с входом памяти, выход которой соединен с входом коммутатора чтения, коммутатор адресов и управления памятью, выходы которого соединены с входом памяти и коммутатора чтения, блок управления выполнением операций, выход которого соединен с входом арифметико-логического устройства [2].

Однако и такое устройство не отличается высокой производительностью из-за невозможности параллельного совмещения операций над скалярными и векторными числами, а также достаточной надежностью функционирования.

Целью изобретения является повышение надежности и производительности.

Для этого в конвейерный процессор, содержащий коммутатор записи, выход которого соединен с входом памяти, выход которой соединен с входом коммутатора чтения, коммутатор адресов и управления памятью, выходы которого соединены с входом памяти и коммутатора чтения, блок управления выполнением операций, выход которого соединен с входом арифметико-логического устройства, введены первый и второй блоки управления потоками команд, коммутатор результатов, адаптер системного канала, коммутатор операндов, причем выходы первого блока управления потоком команд соединены с входами блока управления выполнением операций, коммутатора адресов и управления памятью, коммутатора записи и коммутатора результатов, выходы которого соединены с входами коммутатора операндов, первого блока управления потоком команд, коммутатора записи и второго блока управления потоком команд, выходы которого соединены со входами коммутатора результатов, коммутатора адресов и управления памятью, коммутатора записи и блока управления выполнением операций, выходы которого соединены с входами коммутатора адресов и управления памятью, коммутатора операндов, коммутатора результатов и адаптера системного канала, выходы которого соединены с входами коммутатора адресов и управления памятью и коммутатора записи, выходы коммутатора чтения соединены с входами адаптера системного канала, первого и второго блоков управления потоками команд и коммутатора операндов, выходы которого соединены с входами арифметико-логического устройства, выход которого соединен с входом коммутатора результатов, а информационные вход и выход адаптера системного канала являются входными и выходными информационными шинами соответственно.

Сущность изобретения заключается в том, что введение первого и второго блоков управления потоками команд, коммутатора результатов, коммутатора операндов и адаптера системного канала позволило с максимальным темпом, согласованным с темпом подачи кодов операций, загружать операциями конвейерные арифметические устройства.

Сравнение предлагаемого технического решения с прототипом позволило установить соответствие его критерию "новизна".

При изучении других известных технических решений в данной области техники признаки, отличающие изобретение от прототипа, не были выявлены и потому они обеспечивают данному техническому решению соответствие критерию "изобретательский уровень".

Макетные испытания показали возможность промышленного его применения.

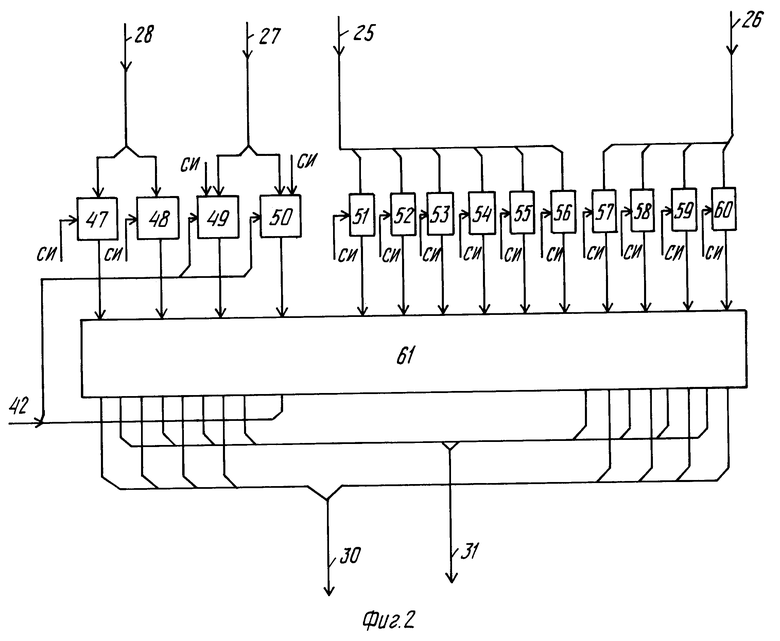

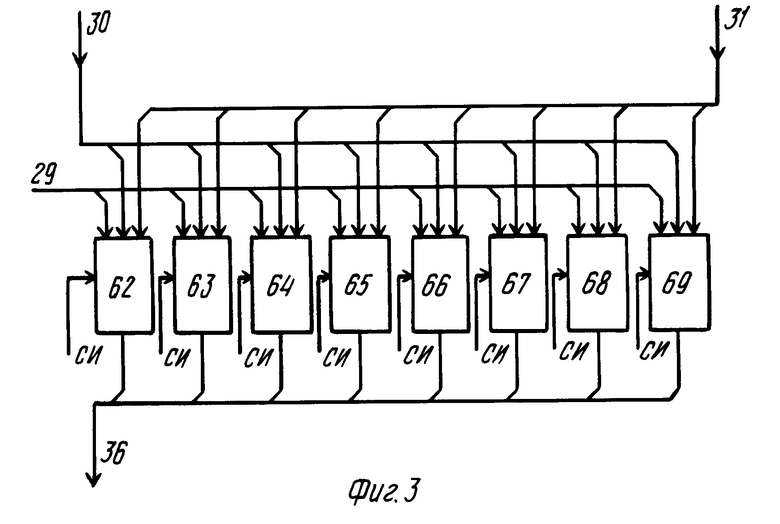

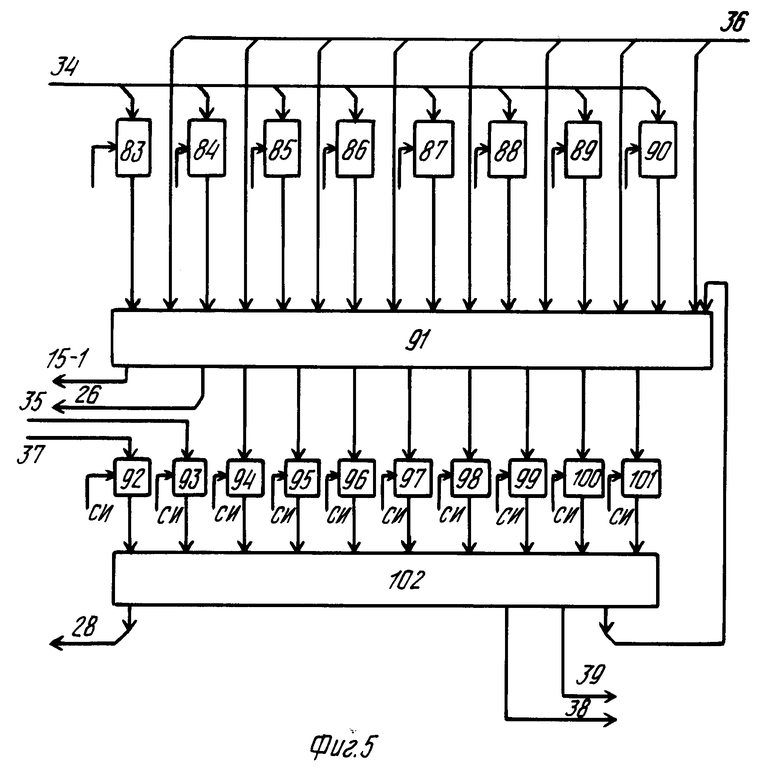

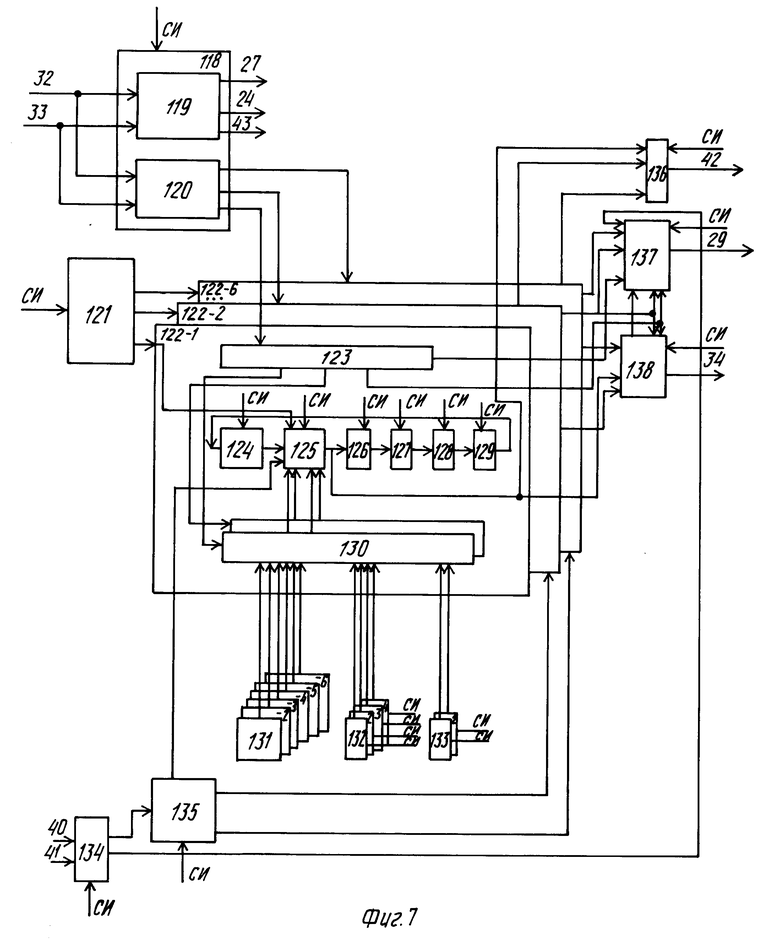

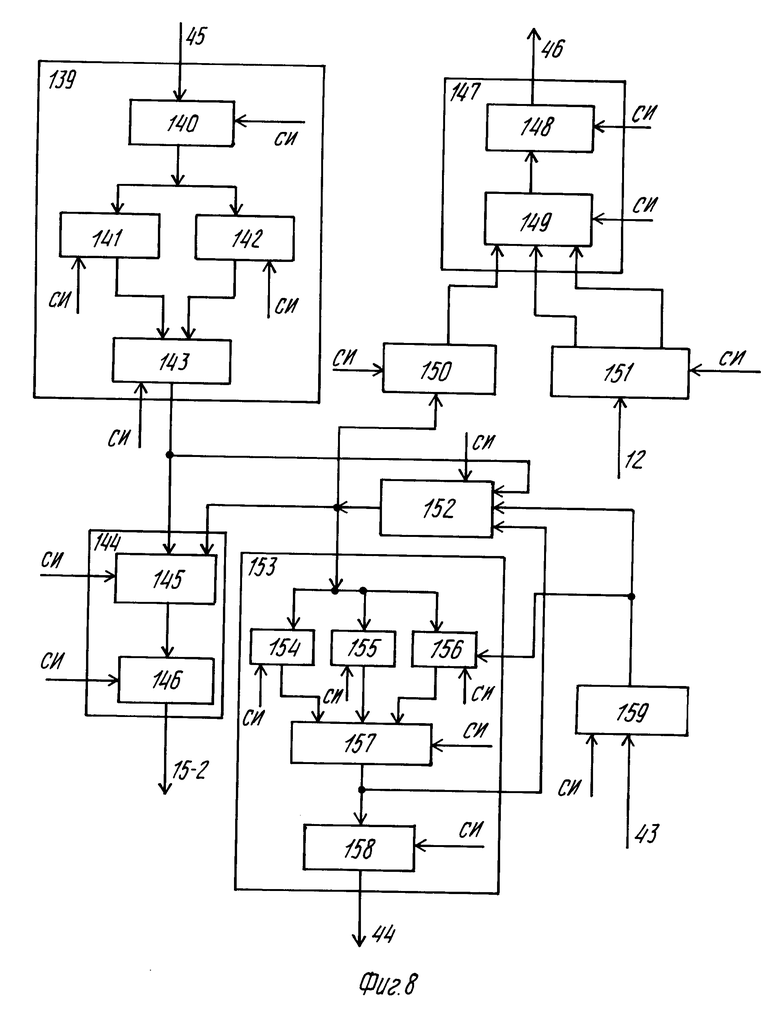

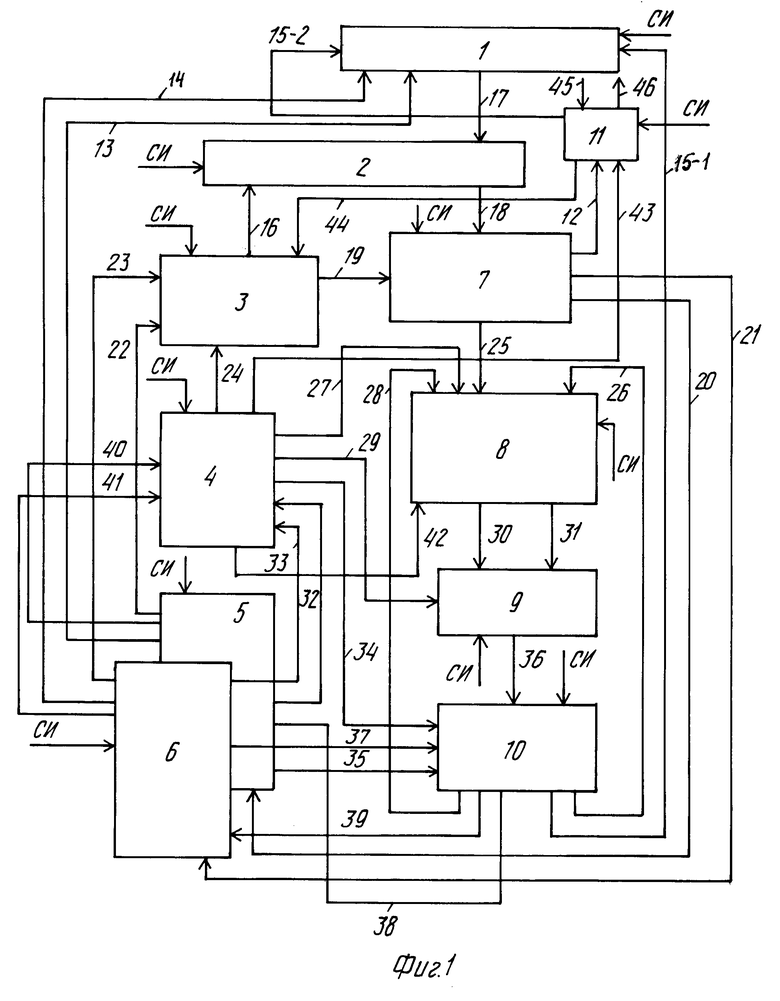

На фиг. 1 представлена блок-схема конвейерного процессора; на фиг.2 - схема коммутатора операндов; на фиг.3 - схема арифметико-логического устройства; на фиг.4 - формирователь потока команд; на фиг.5 - коммутатор результатов; на фиг. 6 - схема коммутатора адресов и управления памятью; на фиг. 7 - схема формирователя управляющих сигналов; на фиг.8 - схема блока обмена.

Конвейерный процессор содержит первый коммутатор 1 записи, память 2, второй коммутатор 3 адресов и управления памятью, формирователь 4 управляющих сигналов, два формирователя 5 и 6 потоков команд, третий коммутатор 7 чтения, четвертый коммутатор 8 операндов, арифметико-логический блок 9, пятый коммутатор 10 результатов, блок 11 обмена, подключенную к информационному выходу коммутатора 7 шину 12 данных блока 11 обмена кодовые шины 13 и 14, подключенные к первым информационным выходам первого и второго формирователей 5 и 6, шину 15-1 записи векторного результата, подключенную к первому информационному выходу коммутатора 10, кодовую шину 15-2 записи, подключенную к первому информационному входу блока 11, адресную шину 16, подключенную к адресному выходу коммутатора 3, шину 17 записи в память 2, подключенную к информационному выходу коммутатора 1, шину 18 данных из памяти 2, подключенную к ее информационному выходу, шину 19 управления, подключенную к управляющему выходу коммутатора 3, шины 20 и 21 данных для формирователей 5 и 6 управления, подключенные к первому и второму командным входам коммутатора 7, адресные шины 22 и 23 из формирователей 5 и 6, подключенные к их адресным выходам, шину 24 загрузки векторных ресурсов коммутатора 3, подключенную к первому управляющему выходу формирователя 4, шину 25 данных коммутатора 7, подключенную к его второму информационному выходу, шину 26 промежуточных результатов, подключенную ко второму информационному выходу коммутатора 10, шину 27 загрузки в коммутатор 8, подключенную к первому информационному выходу формирователя 4, шину 28 данных в коммутатор 8, подключенную к третьему информационному выходу коммутатора 10, шину 29 кода и признаков операций в функциональные модули, подключенную ко второму управляющему выходу формирователя 4, шины 30 и 31 первого и второго операндов в функциональные модули, подключенные к первому и второму информационным выходам коммутатора 8, шины 32 и 33 векторных команд из формирователей 5 и 6, подключенные к их первым управляющим выходам, адресную шину 34 коммутации результатов функциональных модулей, подключенную к адресному выходу формирователя 4, шину 35 первого скалярного операнда из первого формирователя 5 обмена, подключенную к его второму информационному выходу, шину 36 результатов функциональных модулей, подключенную к выходу блока 9, шину 37 второго скалярного операнда из второго формирователя 6 обмена, подключенную к его второму информационному выходу, шины 38 и 39 записи в формирователи 5 и 6, подключенные к четвертому и пятому информационным выходам коммутатора 10, шины 40 и 41 скалярных команд из формирователей 5 и 6, подключенные к их вторым управляющим выходам, шину 42 управления коммутатором 8, подключенную к третьему управляющему выходу формирователя 4, управляющую шину 43 загрузки блока 11 обмена, подключенную к четвертому управляющему выходу формирователя 4, адресную шину 44, подключенную к адресному выходу блока 11, входную и выходную информационные шины 45 и 46 обмена с каналом.

В коммутатор 8 операндов (фиг.2) входят регистры 47 и 48 скалярных операндов, регистры 49 и 50 векторных первой и второй констант, регистры 51-56 считывания, регистры 57-60 промежуточных векторных результатов, блок 61 коммутации причем к первому информационному входу 28 коммутатора 8 подключены входы регистров 47 и 48, к второму информационному входу 27 - входы регистров 49 и 50, к третьему информационному входу 25 - входы регистров 51-56, к четвертому информационному входу 26 - входы регистров 57-60, выходы всех регистров 47-60 подключены к входам блока 61, управляющий вход которого соединен с шиной 42 управления, а его выходы подключены к шинам 30 и 31 первого и второго операндов в зависимости от обрабатываемой информации.

В арифметико-логическое устройство 9 (фиг.3) входят 8 функциональных модулей 62-69 (4 скалярных и 4 векторных), управляющие входы которых подключены к шине 29 кода и признаков операций, а информационные входы в зависимости от поступающих операндов (скалярной или векторной информации) подключены к шинам 30 и 31 первого и второго операндов, выход каждого модуля соединен с шиной 36 результатов функциональных модулей.

Формирователи 5 и 6 потоков команд (фиг.4), в каждый из которых входят блок 70 буферных регистров записи, блок 71 формирования адреса, D-регистры 72, индексные регистры 73, блок 74 адресной арифметики, блок 75 регистров векторных слогов, блок 76 регистров векторных адресов, блок 77 регистров команд, блок 78 регистров предварительной выборки команд, блок 79 дешифрации команды, блок 80 регистров арифметических команд, блок 81 регистров обменных команд, блок 82 регистров скалярных операндов, причем к командному входу 20 формирователя 5 подключены управляющие входы D-регистров 72, индексных регистров 73, блока 78 регистров и блока 82 регистров, информационный вход которого подключен к информационному входу блока 61 управления, первый выход блока 74 соединен с информационными входами D-регистров 72 и индексных регистров 73, выходы которых подключены к первому и второму информационным входам блока 74, причем выход индексных регистров 73 соединен с входом блока 81, второй и третий информационные выходы блока 74 подключены к входам блоков 70 и 71, выход блока 70 соединен с вторым управляющим выходом 13 формирователя 5, а выход блока 71 подключен к адресному выходу 22 формирователя 5, четвертый и пятый информационные выходы блока 74 подключены, соответственно, к входам блоков 75 и 76, выходы которых соединены с первым управляющим выходом формирователя 5, выход блока 78 подключен к входам блоков 77 и 79, второй вход которого соединен с выходом блока 77, выход блока 79 подключен к входу блока 80, выход которого и выход блока 81 соединены с вторым информационным выходом 35 формирователя 5, информационный вход блока 82 соединен с информационным входом 38 формирователя 5, выход блока 82 соединен с первым информационным выходом 40 формирователя 5.

В коммутатор 10 результатов (фиг.5) входят блоки 83-90 регистров адресов результатов каждого функционального модуля, блок 91 коммутации результатов функциональных модулей, регистры 92 и 93 скалярных операндов из первого и второго блоков управления, сумматоры 94-101 скалярных величин, коммутатор 102 результатов скалярных сумматоров, причем вход каждого блока 83-90 регистров подключен к адресному входу 34 коммутатора 10, управляющие входы блока 91 соединены с выходами блоков 83-90 регистров, а информационные входы блока 91 коммутации подключены к второму информационному входу 36 коммутатора 10, первый информационный выход блока 91 соединен с первым информационным выходом 15-1 коммутатора 10, второй информационный выход блока 91 подключен к второму информационному выходу 26 коммутатора 10, остальные 8 выходов блока 91 соединены со входами каждого из сумматоров 94-101, выходы которых и выходы регистров 92 и 93 подключены к входам коммутатора 102, первый, второй и третий информационные выходы которого соединены соответственно с третьим, четвертым и пятым информационными выходами 28, 38 и 39 коммутатора 10, четвертый информационный выход коммутатора 102 подключен к входу блока 91 коммутации, входы регистров 92 и 93 соединены соответственно с первым и третьим информационными входами 35 и 37 коммутатора 10.

В коммутатор 3 адресов и управления памятью (фиг.6) входят коммутатор 103 адресов записи, коммутатор 104 адресов считывания векторных величин, блок 105 управления коммутаторами памяти, два идентичных блока 106-1 и 106-2 выработки адресов векторной записи, в каждый из которых входят счетчик 107 длины адресов записи, блок 108 управления выработки векторных адресов записи, генератор 109 адресов векторной записи, регистр 110 начального адреса записи, регистр 111 шага записи, шесть идентичных блоков 112-1 - 112-6 выработки адресов векторного считывания, в каждый из которых входят блок 113 управления выработки векторных адресов считывания, генератор 114 адресов векторного считывания, счетчик 115 длины адресов векторного считывания, регистр 116 начального адреса считывания, регистр 117 шага считывания.

В формирователь 4 управляющих сигналов (фиг.7) входят блок 118 загрузки, состоящий из блока 119 загрузки генераторов адресов векторных и блока 120 загрузки фрагментов, блок 121 активизации фрагментов, шесть идентичных блоков 122-1 - 122-6 управляющих фрагментов, блок 123 регистров управляющей информации, блок 124 анализа занятости функционального модуля, блок 125 пуска функционального модуля, сдвигатели 126-129, два коммутатора 130-1 и 130-2 управления, шесть счетчиков 131-1 - 131-6 готовности на считывание, четыре счетчика 132-1 - 132-4 промежуточных результатов, два счетчика 133-1 и 133-2 готовности на запись, регистр 134 скалярной команды, блок 135 приоритетного управления, блок 136 управления коммутатором операндов, блок 137 выдачи кода операций и признаков в функциональный модуль, блок 138 выработки адреса результата.

В блок 11 обмена входит блок 139 приемного сопряжения, содержащий приемный регистр 140, два блока 141 и 142 регистров, мультиплексор 143, блок 144 записи данных, содержащий мультиплексор 145, регистр 146, блок 147 выходного сопряжения, содержащий регистр-передатчик 148, мультиплексор 149, блок 150 выдачи служебной информации, блок 151 считывания данных, блок 152 управляющих слов, блок 153 генерации адресов памяти, содержащий сумматоры 154-156, мультиплексор 157, регистр 158, блок 159 регистров инструкции.

Синхронизация работы устройства - однофазная. Однако в зависимости от элементной базы, типов используемых триггеров и схемотехники может быть использована и другая система синхронизации, в частности многофазная.

Конвейерный процессор работает следующим образом.

После начальной иницианизации формирователи 5 и 6 потоков команд выполняют подкачку программного кода из памяти 2. С этой целью они выдают запросы по адресным шинам 22 и 23 через коммутатор 3 адресов и управления памятью. Программный код из памяти 2 через коммутатор 7 чтения по шинам 20 и 21 данных для формирователей 5 и 6 потоков команд поступает в блок 78 буферных регистров предварительной выборки команд каждого из формирователей 5 и 6 потоков команд, из которого команда поступает на блок 79 дешифрации команды и параллельно записывается в ассоциативный блок 77 командных слов.

Формирователи 5 и 6 потоков команд выдают скалярные команды в формирователь 4 управляющих сигналов выполнением операций по шинам 40 и 41 скалярных команд и скалярные операнды из регистров 82 скалярных в коммутатор 10 результатов по шинам 35 и 37 скалярных операндов из формирователей 5 и 6 потоков команд.

Пересылка содержимого скалярных регистров 101 из коммутатора 10 результатов в регистры 82 скалярные формирователей 5 и 6 осуществляется по шинам 38 и 39 записи скалярных операндов.

Формирователи 5 и 6 потоков команд выдают векторные задания в формирователь 4 управляющих сигналов выполнением операций по шинам 32 и 33 векторных команд.

Запись содержимого регистров 82 скалярных, индексных регистров 73, D-регистров 72 формирователей 5 и 6 в память 2 осуществляется по кодовым шинам 13 и 14 записи.

Формирователи 5 и 6 работают на общей памяти 2 и управляют самостоятельными независимыми потоками команд с возможностью аппаратно-программной синхронизации их друг с другом. Количество таких блоков принципиально может быть увеличено, что позволит повысить производительность скалярных вычислений.

Формирователь 4 управляет выполнением векторных и скалярных команд. При выполнении векторных команд формирователь 4 загружает по шине 24 загрузки векторные ресурсы коммутатора 3 адресов и управления памятью генераторы 114 и 109 адресов векторных считывания и записи, счетчики 115 и 107 длины векторных выражений.

Формирователь 4 управляет подключением векторных операндов в коммутаторе 8 операндов для арифметико-логического устройства 9 по шине 42 управления.

Формирователь 4 загружает регистры 49, 50 векторных констант коммутатора 8 операндов по шине 27 загрузки и передает код операции векторных и скалярных команд в функциональные модули арифметико-логического устройства 9 по шине 29 кода и признаков операций и адреса результатов в коммутатор 10 результатов по адресной шине 34 коммутации результата.

Коммутатор 3 адресов и управления памятью осуществляет коммутацию адресов двенадцати запросчиков в память 2 по адресной шине 16 в соответствии со схемой приоритета и занятостью модулей памяти 2.

В коммутаторе 8 операндов блоки 51-56 регистров считывания загружаются из памяти 2 через коммутатор 7 чтения по шине 25 данных, а блоки 57-60 регистров промежуточных векторных результатов загружаются по шине 26, скалярные регистры 47, 48 для первого и второго операндов загружаются по шине 28 данных.

Коммутатор 8 операндов осуществляет коммутацию векторных и скалярных операндов в функциональные модули арифметико-логического устройства 9 и передает первый операнд по шине 30, а второй операнд - по шине 31.

Арифметико-логическое устройство 9 получает команду из формирователя 4, операнды - из коммутатора 8 операндов и передает результаты вычислений в коммутатор 10 результатов по шине 36, который коммутирует промежуточные векторные результаты в блоки регистров промежуточных результатов коммутатора 8 операндов по шине 26, а окончательные результаты векторных вычислений - в коммутатор 1 записи по шине 15-1 для записи в память 2.

Блок 11 получает управляющую информацию-инструкцию из формирователя 4 по управляющей шине 43.

В блоке 11 информация через блок 159 регистров инструкций направляется в блок 152 управляющих слов и инициирует обмен по системному каналу по информационным шинам 45 и 46 связи с абонентом, например, с внешней памятью (на фигурах не показано).

Если инструкция типа "выдача", то через блок 150 выдачи служебной информации и блок 147 выходного сопряжения, выдается сообщение-заявка в системный канал и ожидается ответ-квитанция, который принимается в блоке 139 приемного сопряжения и направляется в блок 152 управляющих слов, который загружает адресной информацией один из сумматоров 154-156 блока 153 генерации адресов и выдает в коммутатор 3 адресов и управления памятью поток последовательных адресов памяти. Полученные из памяти 2 данные по шине 12 поступают в блок 151 считывания данных блока 11 и выдаются в системный канал через блок 147 выходного сопряжения на информационную шину 46.

При выполнении инструкции "принять" блок 11 системного канала работает аналогично, но в ответ на заявку, по информационной шине 45 поступает не квитанция, а поток последовательных данных, накапливаемых в блоках 141, 142 регистров блока 139 приемного сопряжения и передаваемых через блок 144 записи данных на кодовую шину 15-2 для запоминания в памяти 2 через коммутатор 1 записи.

Таким образом, выполнение арифметико-логического устройства 9 в виде восьми функциональных модулей, способных выполнять векторные и скалярные операции, позволяет с высокой надежностью максимально использовать оборудование. Введение коммутаторов 8 и 10 операндов и результатов обеспечивает связанность слогов в векторном выражении без записи промежуточных результатов в память. Введение формирователей 5 и 6 управления потоками команд и блока 11 системного канала при предложенной организации связей позволяет с максимальным темпом загружать операциями конвейерные арифметические устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1991 |

|

SU1804645A3 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

Изобретение относится к вычислительной технике и может быть использовано для построения мощных вычислительных систем. Процессор содержит первый коммутатор 1, память 2, второй коммутатор 3, формирователь 4 управляющих сигналов, формирователи 5 и 6 потоков, третий коммутатор 7, четвертый коммутатор 8, арифметико-логический блок 9, пятый коммутатор 10, блок 11 обмена. Изобретение позволяет повысить производительность системы и отдельного процессора за счет совмещения действий с векторами и скалярами. 8 ил.

КОНВЕЙЕРНЫЙ ПРОЦЕССОР, содержащий первый и второй коммутаторы, выходы которых соединены с входами памяти, выход которой соединен с входом третьего коммутатора, формирователь управляющих сигналов, выход которого соединен с входом арифметико-логического блока, отличающийся тем, что в него введены первый и второй формирователи потоков команд, четвертый и пятый коммутаторы и блок обмена, причем выходы четвертого коммутатора соединены с входами арифметико-логического блока, выход которого соединен с входом пятого коммутатора, выходы которого соединены с входами первого и четвертого коммутаторов и первого и второго формирователей потоков команд, выходы которых соединены с входами первого, второго и пятого коммутаторов и формирователя управляющих сигналов, выходы которого соединены с входами второго, четвертого и пятого коммутаторов и блока обмена, выходы которого соединены с входами первого коммутатора и второго коммутатора, выход которого соединен с входом третьего коммутатора, выходы которого соединены с входами блока обмена, четвертого коммутатора и первого и второго формирователей потоков команд.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 4694035, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1995-03-27—Публикация

1992-01-27—Подача