Изобретение относится к радиотехнике.

Целью является повышение помехоустойчивости.

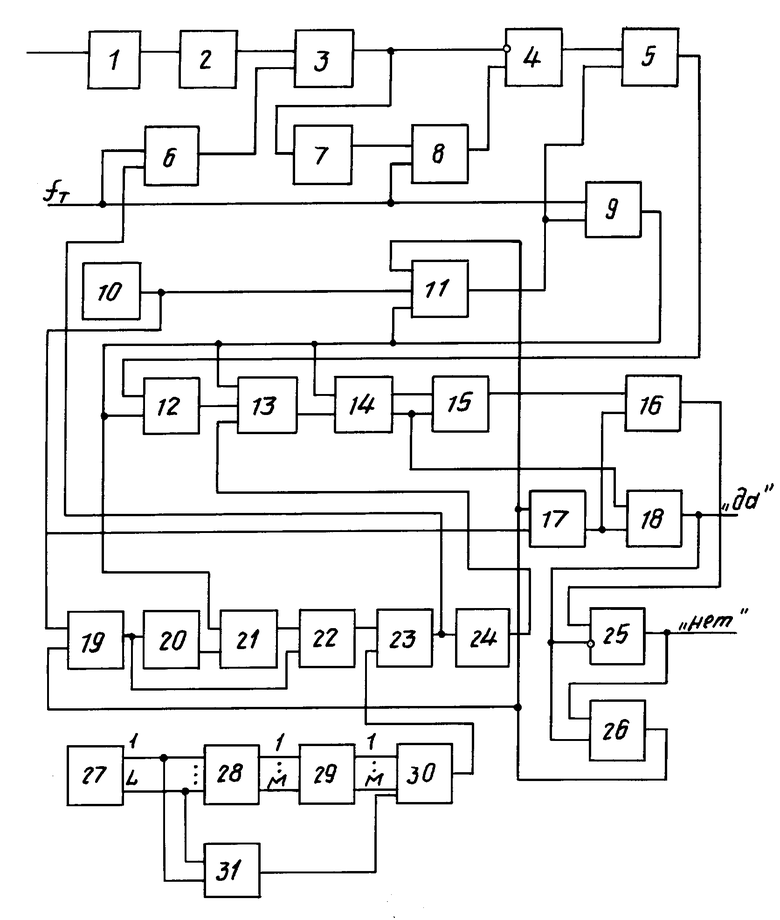

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит фильтр 1, компаратор 2, первый элемент И 3, третий элемент И 4, первый счетчик 5, блок деления частот 6, первый элемент задержки 7, второй элемент И 8, второй счетчик 9, блок 10 начальной установки, первый элемент ИЛИ 11, блок 12 элементов И, вычитающий блок 13, блок 14 сравнения, второй элемент ИЛИ 15, третий счетчик 16, третий элемент ИЛИ 17, четвертый счетчик 18, четвертый элемент ИЛИ 19, второй элемент задержки 20, пятый элемент ИЛИ 21, распределитель 22, блок 23 элементов И-ИЛИ, третий элемент задержки 24, четвертый элемент И 25, шестой элемент ИЛИ 26, блок ключей 27, постоянное запоминающее устройство (ПЗУ) 28, блок 29 элементов ИЛИ, регистр 30, седьмой элемент ИЛИ 31.

Устройство работает следующим образом.

Нажатием одной из L кнопок управления (L - число сигналов, используемых в системе связи) выбирается сигнал, используемый в системе связи в данный момент. Кнопки жестко связаны с входами выбора адреса ЕР соответствующих зон ПЗУ 28. В каждой зоне ПЗУ 28 записана в двоичном коде структура кодовой последовательности одного из сигналов. После нажатия одной из L кнопок открывается соответствующий ключ и информация одной из зон ПЗУ 28 передается в регистр 30. Одновременно сигнал от ключа через элемент ИЛИ 31 поступает на тактовый вход регистра 30. Так как регистр является параллельным на D-триггерах, то при поступлении сигнала на его тактовый вход происходит одновременная запись во все ячейки регистра кода чисел, хранящегося в определенной зоне ПЗУ 28. Таким образом данное устройство настроилось на работу с определенным сигналом. Допустим, что устройство работает с трехчастотным сигналом (М=3). При нажатии одной из L кнопок из ПЗУ 28 в регистр 30 записалась кодовая структура сигнала 3,1,2. Устройство настроилось на работу с сигналом, имеющим частотную структуру 3,1,2.

С момента обнаружения сигнала в приемном устройстве включается источник тактовой частоты, который вырабатывает импульсы с частотой 2М (М - наивысшая частота в структуре сигнала). Устройство синхронизации синфазирует работу источника тактовой частоты с моментом поступления сигнала. При включении на клемме А появляется сигнал, который через дифференциальный элемент и элементы ИЛИ 11, 17, 19 приводит все счетчики и распределитель 22 уровней в исходное состояние, а именно импульс начальной установки подается на входы S, R счетчиков 5, 9 через элемент ИЛИ 11, на входы S, R счетчиков 16, 18 через элемент ИЛИ 17 и на вход распределителя 22 через элемент ИЛИ 19. Это означает что при поступлении импульсов на счетные входы счетчиков последние будут подсчитывать их количество в порядке поступления, например 1,2... и т.д. Никакого другого разрешения для работы счетчиков не нужно. То же самое и для распределителя 22 уровней. При поступлении первого импульса на тактовый вход С распределитель уровней 22 распределяет его в первый канал (первый выход), второго - во второй канал (второй выход) и т.д. Никакого другого разрешения для работы распределителя 22 не нужно. Причем сигнал на конкретном выходе распределителя 22 действует постоянно до тех пор, пока не поступит очередной импульс на его вход.

Одновременно сигнал с выхода элемента ИЛИ 19 через элемент задержки 20 и элемент ИЛИ 21 поступает на тактовый вход распределителя 22. Время задержки в элементе 20 составляет t3 = To/2. Этот первый тактовый импульс поступает на первый выход распределителя уровней 22, который подключен к вторым входам элементов И блока 23, первые входы которых соединены с первой ячейкой регистра 30. Таким образом информация из первой ячейки регистра 30 через блок 23 элементов И-ИЛИ поступает на второй вход блока деления частоты 6, в частности на вход дешифратора блока 6, сигнал на выходе которого будет на одном из М выходов в зависимости от двоичной комбинации, поступившей из ячейки регистра 30. Следовательно, на второй вход элемента И 3 будут поступать импульсы с частотой в два раза меньше тактовой. Кроме того, информация из первой ячейки регистра 30 через блок элементов И-ИЛИ 23 и элемент задержки 24 (время задержки tз = Т/2) поступает на вход В вычитающего блока 13.

Входной сигнал, прошедший широкополосный аналоговый фильтр 1, поступает на компаратор 2. Сигнал на выходе компаратора будет в том случае, если поступающий на его вход сигнал превысил какой-то заранее установленный уровень. Допустим этот уровень равен нулю. Тогда в моменты времени, соответствующие положительным полуволнам поступающих сигналов, на выходе компаратора 2 будем иметь сигнал, который, совпадая в определенные моменты времени с импульсами, поступающими на второй вход элемента И 3, будет поступать на инверсный вход элемента И 4 и на вход элемента задержки 7. Так как на второй вход элемента И 3 будут поступать импульсы прореженной тактовой частоты, то на выход элемента И 3 будут поступать сигналы, соответствующие только положительным полуволнам полезного сигнала. Время задержки элемента 7 равно одному тексту. После элемента задержки 7 сигнал через элемент И 8 поступает на второй вход элемента И 4. На выходе элемента И 4 сигнал будет при наличии сигнала от элемента И 8 и отсутствии сигнала на инверсном входе. Таким образом на вход счетчика 5 будут поступать импульсы, фиксирующие переход от положительной полуволны каждой частоты к отрицательной. Одновременно счетчик 9 подсчитывает количество тактовых импульсов. При подсчете количества импульсов равном 2М счетчик 9 выдает сигнал на считывание через элемент И 12 в двоичном коде числа, подсчитанного за это время счетчиком 5 количества импульсов (что соответствует номиналу частоты в структуре сигнала). Данное число в двоичном коде поступает на вход А вычитающего блока 13. Одновременно сигнал со счетчика 9 поступает на вход вычитающего блока 13 и вход блока сравнения 14. Кроме того, этот же сигнал через элемент ИЛИ 11 приводит в исходное состояние счетчики 5 и 9. Разность чисел А и В поступает на блок 14 сравнения с нулем. Если число, поступившее на вход блока 14, равно нулю (произошло совпадение номиналов принятой частоты и записанной в ячейке регистра 30), то при наличии сигнала на входе данного устройства появляется сигнал на выходе, который регистрируется счетчиками 16 и 18. Если же разность не равна нулю, то факт сравнения регистрируется только счетчиком 16. Сравнение происходит не постоянно, а только по управляющему сигналу от счетчика 9.

Таким образом при подсчете счетчиком 9 2М тактовых импульсов на выходах блока 14 появляются импульсы, которые и подсчитываются счетчиками 16 и 18. Кроме того, сигнал с выхода счетчика 9 через элемент ИЛИ 21 поступает на тактовый вход распределителя уровней 22, который распределяет его на второй выход. Этот выход подключен к вторым входам элементов И блока 23, первые входы которых соединены с второй ячейкой регистра. Таким образом информация из второй ячейки регистра через блок элементов И-ИЛИ 23 поступает на второй вход блока деления частоты 6, на вход дешифратора. Следовательно, на второй вход элемента И 3 будут поступать импульсы с частотой в 6 раз меньше тактовой, и в течение длительности частоты f1 на второй вход элемента И 3 поступит всего 1 импульс, который и будет зафиксирован счетчиком 5. Кроме того, информация из второй ячейки регистра 30 через блок 23 элементов И-ИЛИ и блок задержки 24 поступает на вычитающий блок. Задержка необходима для того, чтобы в вычитающем блоке успело произойти вычитание кодов предыдущей частоты в структуре сигнала как подсчитанного счетчиком 5, так и считанного из ячейки регистра 30. Дальнейшая обработка осуществляется по тому же алгоритму. Для третьей частоты в структуре сигнала на второй вход элемента И 3 будут поступать импульсы с частотой в три раза меньше тактовой. Всего за время действия третьей частоты на второй вход элемента И 3 поступят два импульса.

Счетчик 16 подсчитывает общее количество частот в структуре сигнала и при подсчете М частот выдает сигнал на элемент И 25. В том случае, когда структура принимаемого сигнала и копия этого сигнала, хранящаяся в регистре 30, совпадают, счетчик 18 зарегистрирует М нулевых разностей, при этом на выходе этого счетчика появляется сигнал, который свидетельствует о том, что принимаемый ДЧ сигнал различен. В противном случае счетчик 18 не сработает, что приведет к появлению сигнала на выходе элемента И 25, который свидетельствует, что принят ДЧ сигнал, не согласованный с данным устройством. При этом сигналом через элемент ИЛИ 26 обеспечивается приведение устройства в исходное состояние (обнуляются счетчики 5, 9, 16, 18, приводится в исходное состояние распределитель уровней 22, т.е. обеспечивается распределение очередного импульса на первый выход).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| Устройство для передачи многочастотных сигналов | 1983 |

|

SU1107328A1 |

| Устройство для передачи многочастотных сигналов | 1987 |

|

SU1406817A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Устройство для приема многочастотных сигналов | 1987 |

|

SU1540031A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1354437A1 |

| Устройство для формирования сигналов частотно-фазовой манипуляции | 1984 |

|

SU1252968A1 |

| Устройство для считывания координат точек объектов | 1989 |

|

SU1693618A1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

Использование: радиотехника. Сущность изобретения: устройство содержит фильтр 1, компаратор 2, регистр 30, элемент задержки 7, четыре счетчика 5, 9, 16, 18, два элемента И 3, 8, два элемента ИЛИ 11, 15, блок сравнения 14, распределитель 22, вычитающий блок 13. С целью повышения помехоустойчивости в устройство введены блок элементов И, пять элементов ИЛИ 17, 19, 21, 26, 31, два элемента И 4, 25, блок 23 элементов И-ИЛИ, блок ключей 27, блок 29 элементов ИЛИ, блок 10 начальной установки, блок 6 деления частот, два элемента задержки 20, 24. 1 ил.

УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ, содержащее фильтр, выход которого соединен с входом компаратора, регистр, первый элемент задержки, первый, второй, третий, четвертый счетчики, первый и второй элементы И, первый и второй элементы ИЛИ, блок сравнения, распределитель, вычитающий блок, отличающееся тем, что введены блок элементов И, третий - седьмой элементы ИЛИ, третий и четвертый элементы И, блок элементов И - ИЛИ, блок ключей, блок элементов ИЛИ, блок начальной установки, блок деления частоты, второй и третий элементы задержки, причем выход компаратора соединен с первым входом первого элемента И, выход которого соединен с инверсным входом третьего элемента И и через первый элемент задержки - с первым входом второго элемента И, выход которого соединен с прямым входом третьего элемента И, выход которого соединен со счетным входом первого счетчика, выход которого соединен с первым входом блока элементов И, второй вход которого, первый вход пятого элемента ИЛИ, первые входы вычитающего блока, блока сравнения, первого элемента ИЛИ соединены с выходом второго счетчика, счетный вход которого, второй вход второго элемента И и первый вход блока деления частоты объединены и являются тактовым входом устройства, входы начальной установки первого и второго счетчиков соединены с выходом первого элемента ИЛИ, выход блока начальной установки соединен с первыми входами третьего и четвертого элементов ИЛИ и вторым входом первого элемента ИЛИ, третий вход которого, второй вход третьего элемента ИЛИ и второй вход четвертого элемента ИЛИ соединены с выходом шестого элемента ИЛИ, первый вход которого и инверсный вход четвертого элемента И соединены с выходом четвертого счетчика, который является первым выходом устройства, вторым выходом которого является выход четвертого элемента И, соединенный с вторым входом шестого элемента ИЛИ, выход блока элементов И соединен с вторым входом вычитающего блока, выход которого соединен с вторым входом блока сравнения, первый и второй выходы которого соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен со счетным входом третьего счетчика, вход начальной установки которого и счетный вход четвертого счетчика соединены с выходом третьего элемента ИЛИ, второй выход блока сравнения соединен с входом начальной установки четвертого счетчика, выход третьего счетчика соединен с прямым входом четвертого элемента И, выход четвертого элемента ИЛИ через второй элемент задержки соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с первым входом распределителя, второй вход которого соединен с выходом четвертого элемента ИЛИ, выход распределителя соединен с первым входом блока элементов И - ИЛИ, выход которого соединен с вторым входом блока деления частоты и через третий элемент задержки - с третьим входом вычитающего блока, выход блока деления частоты соединен с вторым входом первого элемента И, выходы блока ключей соединены с входами блока постоянной памяти и шестого элемента ИЛИ, выход которого соединен с тактовым входом регистра, выход которого подключен к второму входу блока элементов И - ИЛИ, выходы блока постоянной памяти через блок элементов ИЛИ соединены с информационными входами регистра.

| Устройство декодирования тональных сигналов | 1988 |

|

SU1570034A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-03-20—Публикация

1992-01-16—Подача