Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УВМ).

Цель изобретения - расширение функциональных возможностей устройства за счет возможности контроля работы УВМ при наличии прерываний и уменьшение времени выполнения программ управляющей вычислительной машины за счет устранения необходимости введения дополнительных команд безусловных переходов.

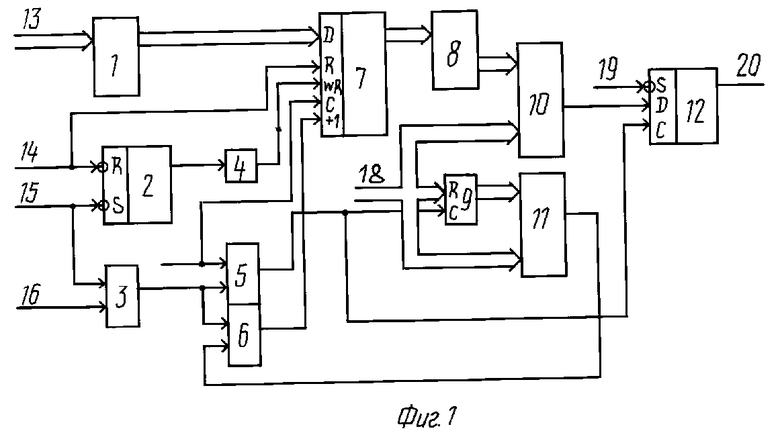

На фиг. 1 показана структурная схема предлагаемого устройства.

Устройство содержит первый блок 1 памяти, триггер 2 очистки, элемент И 3, одновибратор 4, элементы И 5 и 6, счетчик 7, блок 8 памяти, регистр 9, схему 10 и 11 сравнения, триггер 12 ошибки, шину 13 адреса УВМ, линии процессора УВМ: линию 14 очистки, линию 15 обращения к ПЗУ программ, линию 16 подтверждения прерывания, линию 17 синхронизации, линию 18 управления передачей адресов и данных 18, линию 19 начальной установки и линию 20 сигнала сбоя.

На фиг. 2 представлен пример части программы. В программе все такты выполнения команд, в которых происходит изменение сигналов на линиях управления передачей адресов и данных 18, пронумерованы. Начальные номера 0. . . N1 соответствуют временной диаграмме перехода к обработке прерывания (т. е. занесения точки возврата в стек и считывания векторов прерывания). Остальные номера, начиная с N + 1, присвоены тактам выполнения команд, в которых происходит изменение сигналов самой рабочей программы УВМ и программ обработки прерываний. В пределах линейных участков номера наращиваются последовательно.

Устройство предназначено для контроля управляющих вычислительных машин, построенных на базе современных процессоров, имеющих конвейер команд (например, микропроцессоры 1810ВМ86, INTEL 18086).

В данных процессорах используется опережающая выборка команд и формируется очередь команд. При передаче управления в другое место программы конвейер команд очищается, после чего начинает заполняться новыми командами программы. Сигнал очистки конвейера (для микропроцессора 1810ВМ86, например, это сигнал y = QS1 + QS0 = QS1 ˙QS0 активный уровень ("0") которого появляется при QS1 = 0, QS0 = 1), идентифицирует переход к началу нового линейного участка программы и подается на соответствующий вход устройства.

Контроль работы УВМ осуществляется проверкой последовательности следования сигналов управления передачи адресов и данных (Ввод, Вывод, СИП, Байт, и т. д. ), в том числе сигналов выборки модулей УВМ (Запрос ОЗУ, Запрос устройств ввода-вывода и т. д. ) при выполнении команд. Используется то, что поведение УВМ при выполнении команд программы, а также при переходе к обработке прерываний строго детерминировано в том смысле, что при отсутствии сбоев на линиях управления передачи адресов и данных 18 сформирована строго определенная временная диаграмма, которую можно вычислить еще до начала прогона самой программы.

Таким образом, обеспечивается контроль правильности порядка обращения процессора проверяемой УВМ к остальным ее модулям (ОЗУ), устройствам ввода-вывода и т. д. ) в процессе выполнения команд, контроль правильности порядка включения в работу подпpограмм обслуживания прерываний как от внутренних, так и от внешних устройств.

Вторая контрольная функция удачно дополняет первую, обеспечивая контроль управляющих сигналов при переходе к программе обработки прерывания.

Расположение в общей временной диаграмме УВМ процесса считывания команд при наличии прерываний в контролируемой УВМ является недетерминированным. Связано это с недетерминированным характером прерываний, необходимостью повторного считывания команд, которые уже были считаны до момента прерывания. Поэтому правильность считывания команд проверяется не непосредственно (при считывании команд за счет активного уровня ("0") на линии запроса ПЗУ программы 15 блокированы элементы И 5 и 6 и все устройство), а по правильности временной диаграммы их выполнения.

При переходе к обработке прерывания контролируется общая для внешних и внутренних прерываний часть временной диаграммы. При считывании вектора прерывания по сигналу ("0") подтверждения прерывания на линии 16 (что имеет место при обработке только внешнего прерывания) происходит блокировка элементов И 5 и 6 и всего устройства.

Блок 1 памяти прошит так, что по адресам команд программы УВМ записаны номера первого такта выполнения данной команды.

Блок 8 памяти прошит так, что номеру такта временной диаграммы (выполняющего для него роль адреса) ставится в соответствие правильные значения сигналов на линиях 18 в данном такте.

Запись информации в регистры 9, триггеры 2 и 12, а также наращивание счетчика 7 происходит по фронту 0/1 на их синхровходам, причем наращивание счетчика 7 происходит только при наличии сигнала логической "1" на его входе разрешения счета.

Одновибратор 4 формирует положительный импульс на своем выходе при появлении фронта 0/1 на входе. Длительность импульса на выходе одновибратора 4 в пределах 1. . . 2T, где T - период синхроимпульсов на линии 17. Это обеспечивает надежную параллельную запись счетчика 7.

Активный ("0") уровень сигнала "Запрос ПЗУ программы" на линии 15 вырабатывается процессором УВМ (например с помощью входящего в его состав селектора адреса) при его обращении к зоне адресов, где хранится программа, выполняемая УВМ, и сохраняется до конца цикла считывания команды. Векторы прерывания хранятся по адресам, не входящим в указанную область адресов, при их извлечении активный уровень данного сигнала не формируется.

Активный ("0") уровень сигнала на линии 16 подтверждение прерывания вырабатывается при переходе на обработку внешнего прерывания (INTA).

Сигнал сбоя устройства на линии 20 может подаваться на вход сброса (перенапуска) или немаскируемого прерывания процессора УВМ.

При равенстве сигналов на первой и второй группах входов схем 10 и 11 сравнения - на их выходе сигнал логического "1", при неравенстве - логической "0".

Регистр 9 и вторая схема 11 сравнения обеспечивают управление счетчиком 7. Если значения сигналов на контролируемых линиях 18 к моменту прихода фронта 0/1 синхроимпульса совпадают с их значениями, записанными в регистр 9 во время фронта 0/1 предыдущего синхроимпульса, то в этот момент на выходе схемы 11 сравнения и на выходе элемента И 6 - логический "0", что препятствует наращиванию счетчика по фронту 0/1. В регистре 9 сохраняется старое значение. Если значения сигналов на проверяемых линиях 18 за время такта изменяется, то к моменту прихода фронта 0/1 значения сигналов на входах схемы 11 сравнения не совпадают, на ее выходе появляется логическая "1", что обеспечивает при отсутствии блокировки элементов И 5 и 6 наращивание счетчика 7 по фронту 0/1. В регистр 9 по этому же фронту записывается новое значение сигналов на контролируемых линиях 18. Подобное управление счетчиком уменьшает развертку временной диаграммы и тем самым объем блока 8 памяти. Значения сигналов рассматриваются только во время фронтов 0/1 синхроимпульсов, в блоке 8 памяти отсутствует повторение тактов с неизменным значением сигналов на контролируемых линиях 18.

Устройство работает следующим образом.

При включении питания процессор УВМ формирует активный уровень сигнала ("0") начальной установки на линии 19, который устанавливает в пассивное состояние триггер 12. При включении питания также, как и при переходе на новый линейный участок программы происходит очистка конвейера команд процессора УВМ, сопровождающаяся появлением активного ("0") уровня сигнала на линии 14 очистки, приводящего к сбросу триггера 2.

Процессор УВМ обращается к ПЗУ программ УВМ за первой командой нового линейного участка программы, выдавая его адрес. Обращение сопровождается появлением активного ("0") уровня сигнала на линии запрос ПЗУ программ 15, по которому происходит установка триггера 2 очистки. По появляющемуся на выходе триггера 2 очистки фронту 0/1 на выходе одновибратора 4 формируется импульс разрешения записи для счетчика 7. В счетчик 7 по фронту синхроимпульса 0/1 на линии 17 производится запись информации о номере такта управляющего сигнала, поступающего с выхода первого блока 1 памяти.

По мере поступления синхроимпульсов на линии 17 при наличии логической "1" на выходе элемента И 6 происходит наращивание счетчика 7. На выходах блока 8 памяти формируется прогнозируемая временная диаграмма управляющих сигналов, которая поступает на первую группу входов схемы 10 сравнения, на вторую группу входов которой поступают реальные сигналы с контролируемых линий 18.

При отсутствии сбоев к приходу фронта 0/1 очередного синхроимпульса значения сигналов на обоих группах входов схемы 10 сравнения совпадают, на ее выходе "1", триггер ошибки 12 остается в установленном состоянии, активный уровень ("0") сигнала сбоя на линию 20 не выдается.

При сбое из-за возникающего несоответствия между сигналами на входах схемы 10 сравнения в моменты прихода фронта 0/1 синхросигнала на линии 17 на выходе схемы 10 сравнения - "0", а, следовательно, и на выходе триггера 12 ошибки появляется активный уровень ("0"), который подается на линию сбоя устройства 20. По нему процессор УВМ вырабатывает сигнал начальной установки, который устанавливает триггер 12 ошибки в пассивное состояние ("1"). Процессор УВМ переходит к программе обработки прерывания.

Контроль правильности включения в работу подпрограмм обслуживания прерывания происходит следующим образом.

Переход к обработке прерывания сопровождается появлением активного ("0") уровня сигнала на линии 14 очистки, что приводит к сбросу триггера 2 очистки и счетчика 7. По мере поступления синхроимпульсов на линии 17 при наличии логической "1" на выходе элемента И 6 происходит наращивание от 0 счетчика 7 и формирование ожидаемой временной диаграммы, аналогично первому режиму работы происходит ее сравнение с реальной. При отсутствии сбоев при считывании первой команды программы обработки прерывания, сопровождающейся сигналом запроса ПЗУ программы на линии 15, происходит установка триггера 2 очистки и переходит к первому режиму работы устройства. (56) Авторское свидетельство СССР N 1159024, кл. G 06 F 11/30, 1985.

Авторское свидетельство СССР N 1815645, кл. G 06 F 11/28, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля управляющей вычислительной машины | 1990 |

|

SU1815645A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Микропрограммный процессор с контролем | 1986 |

|

SU1372328A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УВМ). Цель изобретения - расширение функциональных возможностей за счет возможности контроля работы УВМ при наличии прерываний и уменьшение времени выполнения программы УВМ за счет устранения необходимости введения дополнительных команд безусловного перехода. Устройство для контроля УВМ содержит блоки памяти, триггеры очистки и ошибки, схемы сравнения, элементы И, одновибратор, счетчик, регистр. 2 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащее первый и второй блоки памяти, счетчик, регистр, триггер очистки, триггер ошибки, первую и вторую схемы сравнения, причем выходы счетчика соединены с группой адресных входов первого блока памяти, группа выходов которого соединена с первой группой входов первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, инверсный вход установки которого является входом начальной установки устройства, выход триггера ошибки является выходом сбоя устройства, первая группа входов второй схемы сравнения, вторая группа входов первой схемы сравнения, группа информационных входов регистра подключены к группе входов контролируемых сигналов устройства, вторая группа входов второй схемы сравнения соединена с выходами регистра, синхровход счетчика подключен к входу синхронизации устройства, инверсный вход установки триггера очистки является входом запроса ПЗУ программ устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности контроля работы УВМ при наличии прерываний и уменьшения времени выполнения программ УВМ за счет устранения необходимости введения дополнительных команд безусловного перехода, в устройство введены одновибратор и три элемента И, причем группа адресных входов второго блока памяти является группой адресных входов устройства, группа выходов второго блока памяти соединена с группой информационных входов счетчика, вход сброса которого является входом очистки устройства и соединен с инверсным входом сброса триггера очистки, выход которого соединен с входом одновибратора, выход которого соединен с входом параллельной записи счетчика, синхровходы триггера ошибки и регистра соединены с выходом первого элемента И, первый вход которого соединен с входом синхронизации устройства, второй вход первого элемента И и первый вход второго элемента И соединены с выходом третьего элемента И, первый вход которого является входом подтверждения прерывания устройства, а второй вход соединен с входом запроса ПЗУ программ устройства, второй вход второго элемента И соединен с выходом второй схемы сравнения, выход второго элемента И соединен с входом разрешения счета счетчика.

Авторы

Даты

1994-04-15—Публикация

1991-03-14—Подача