оо

IsD

ОО

to

ас

113

ИпоПретение относится к вычисли тельной технике, в частности к процессорам с контролем.

Целв изобретения повышение до стоверности контроля микропрограммного процессора.

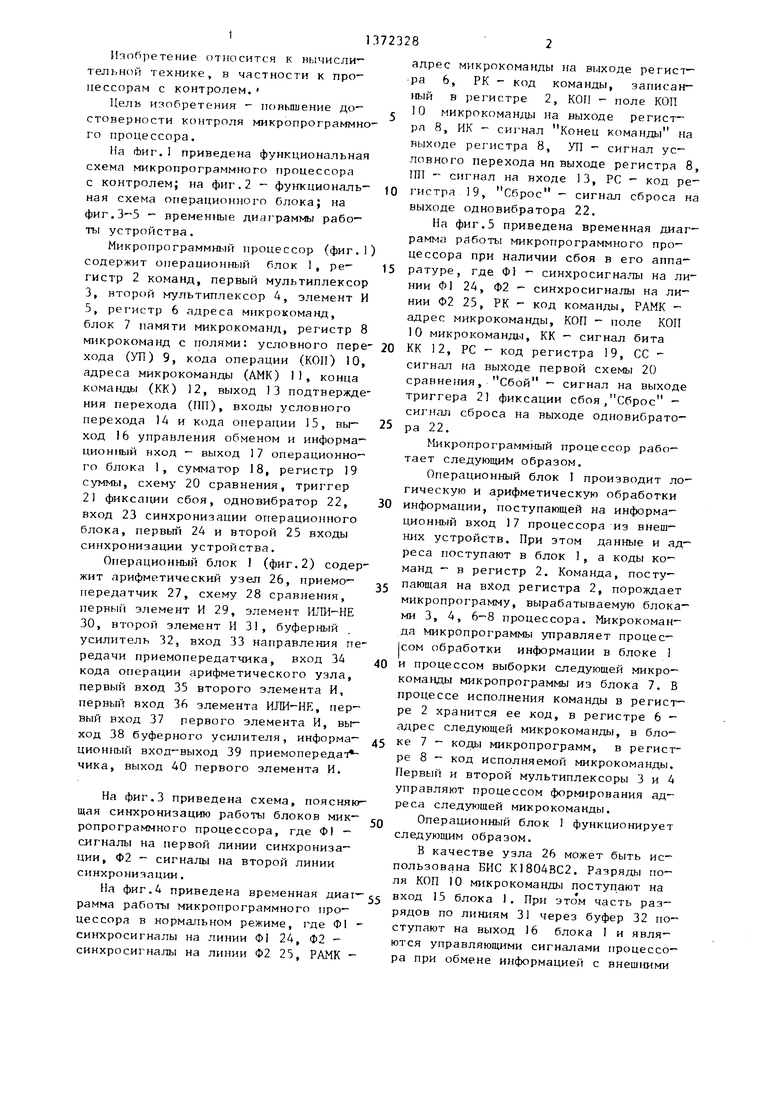

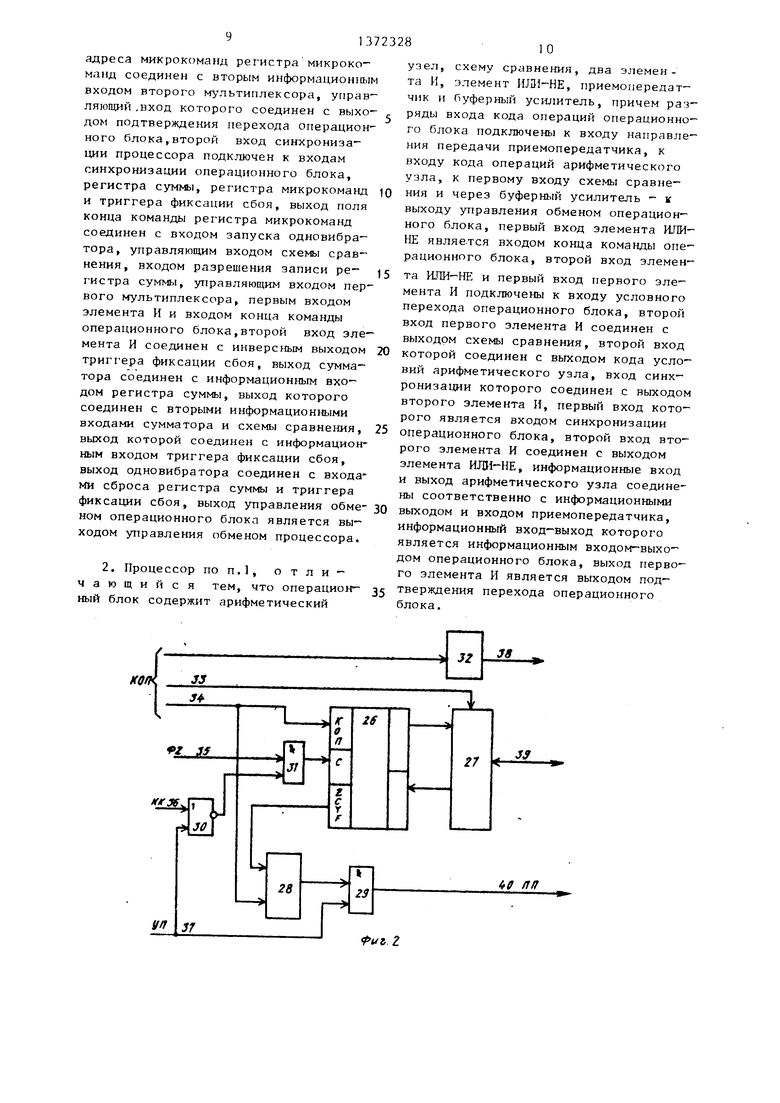

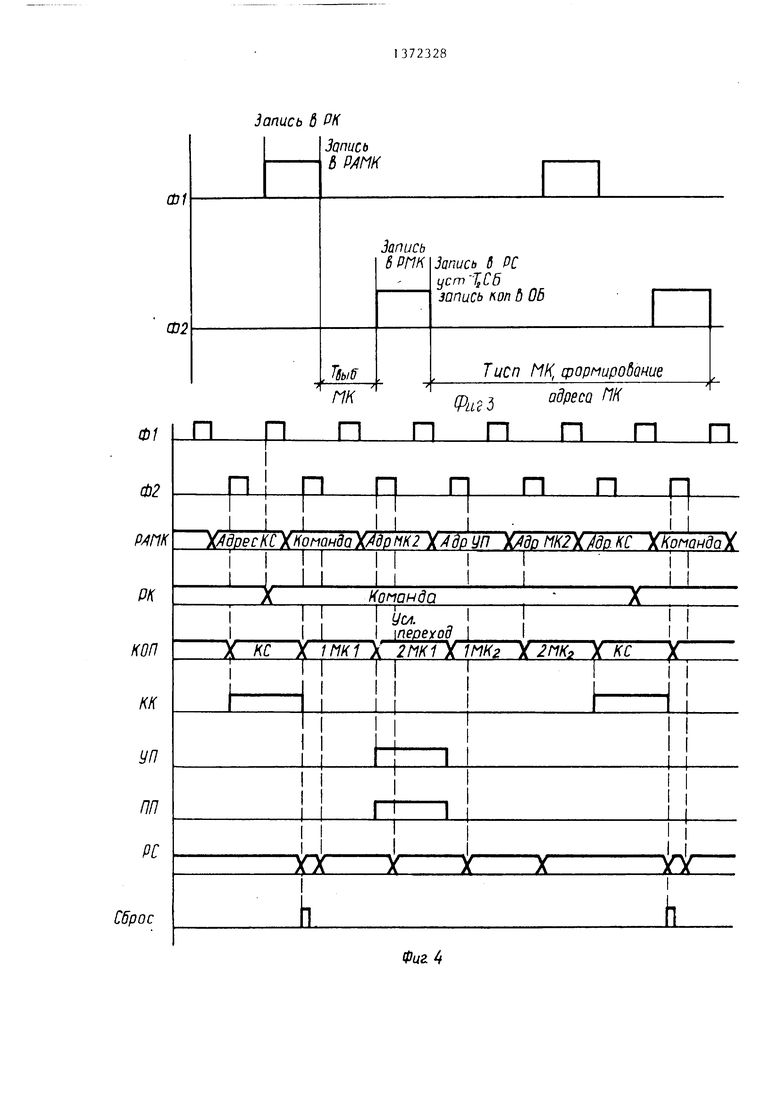

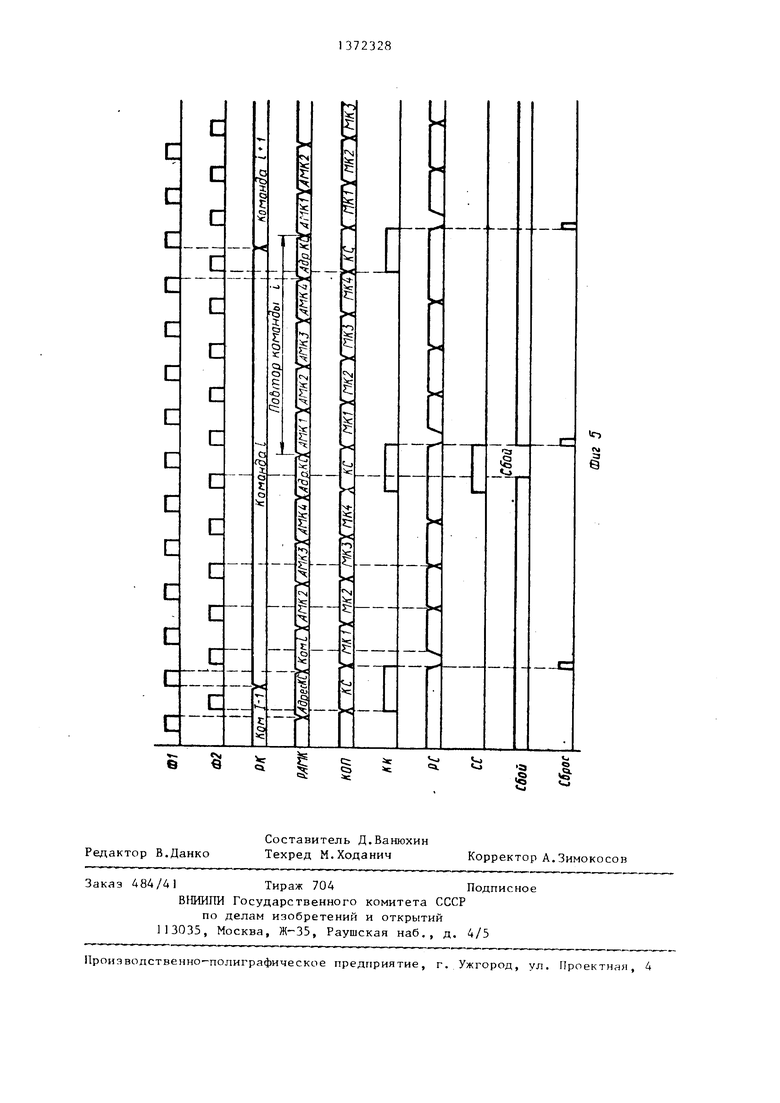

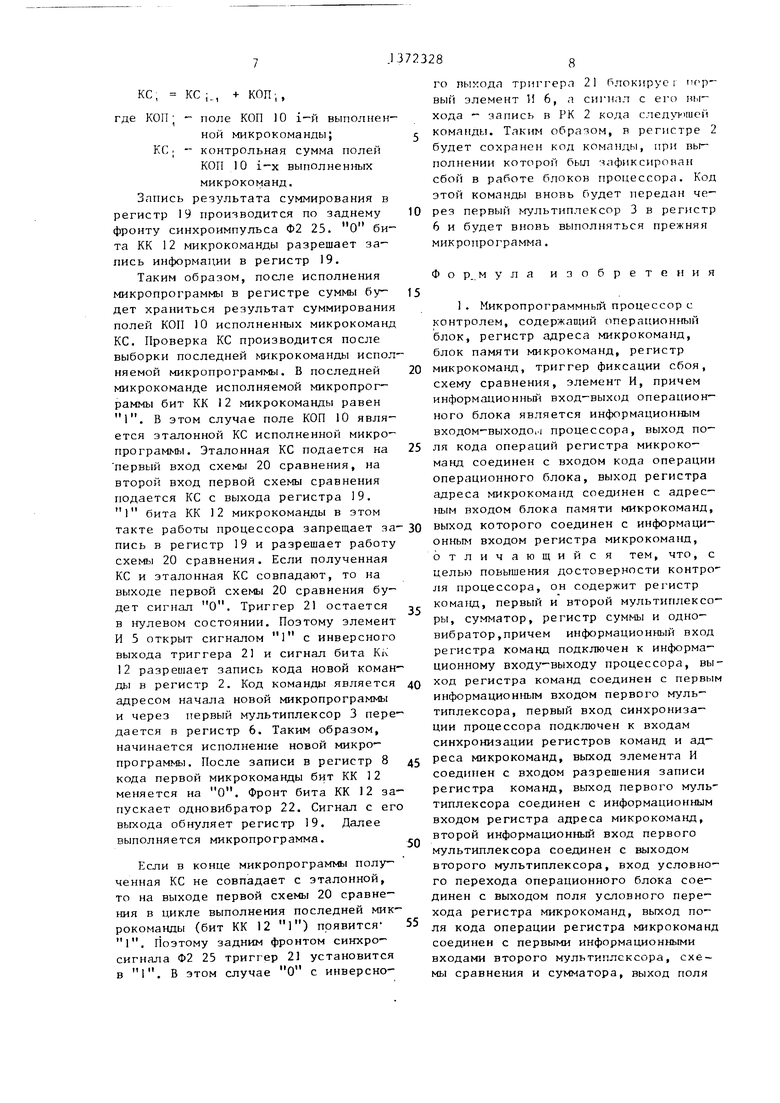

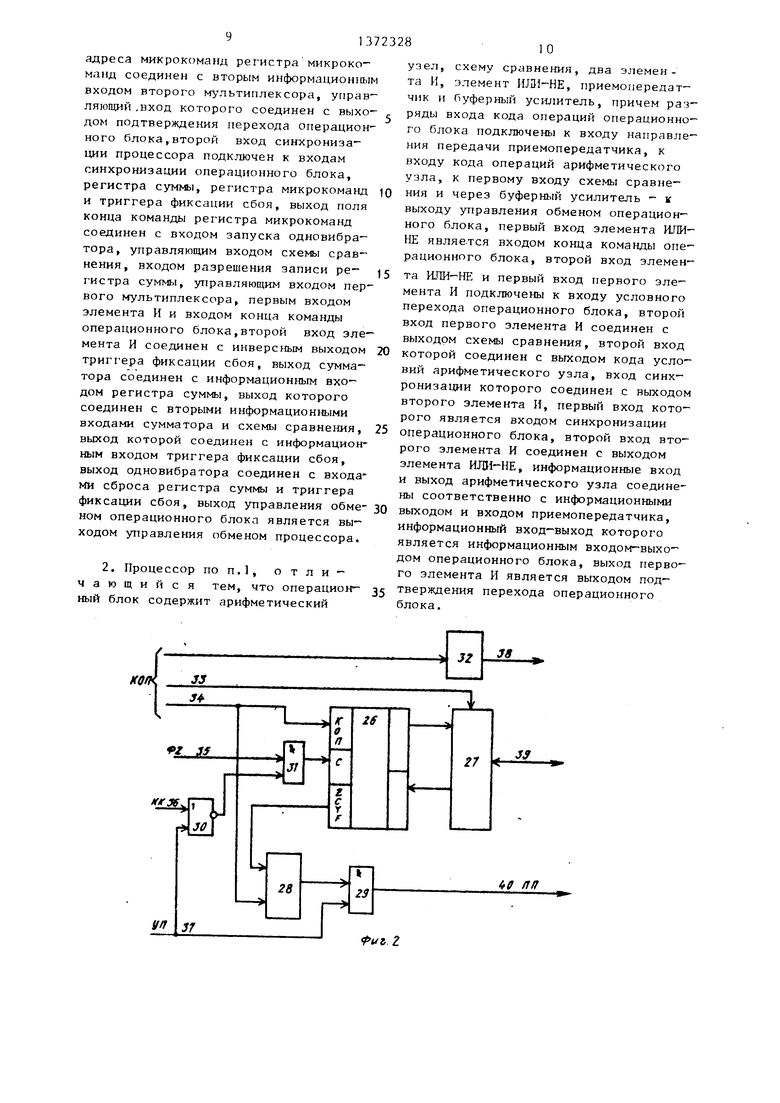

На Лиг. приведена функциональная схема микропрограммного процессора с контролем; на фиг.2 - функциональ- мая схема операционного блока; на фиг. 3-5 - временные диа1 раммы работы устройства.

Микропрограммный процессор (фиг.1 содержит операционный блок 1, ре- гистр 2 команд, первый мультиплексор 3, второй мультиплексор 4, элемент И 5, регистр 6 адреса микрокоманд, блок 7 памяти микрокоманд, регистр 8 микрокоманд с полями: условного пере хода (УП) 9, кода операции (КОП) 10, адреса микрокоманды (АМК) I1, конца команды (КК) 12, выход 13 подтверждения перехода (ПП), входы условного перехода 1 и кода операции 15, вы- ход 16 управления обменом и информационный вход - выход 17 операционного блока 1, сумматор 18, регистр 19 суммы, схему 20 сравнения, триггер 21 фиксации сбоя, одновибратор 22, вход 23 синхронизации операционного блока, первьш 24 и второй 25 входы синхронизации устройства.

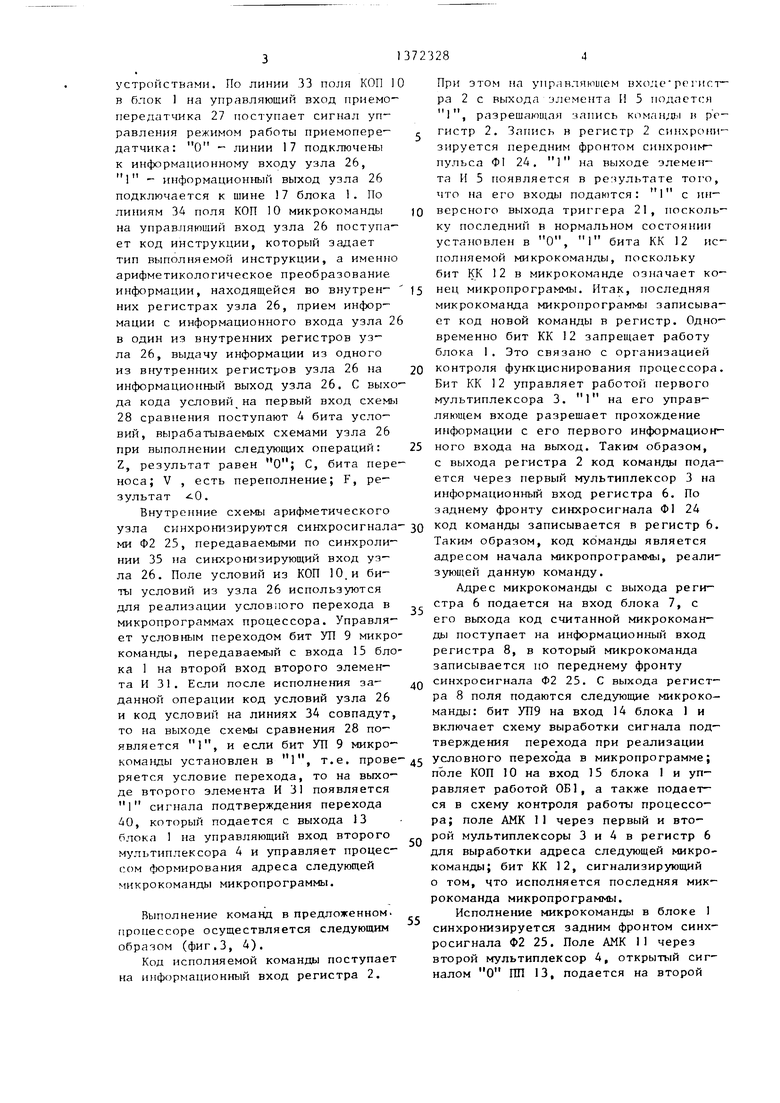

Операционный блок 1 (фиг.2) содержит арифметический узел 26, приемопередатчик 27, схему 28 сравнения, первый элемент И 29, элемент ИЛИ-НЕ 30, второй элемент И 31, буферный усилитель 32, вход 33 направления передачи приемопередатчика, вход ЗД кода операции арифметического узла, первый вход 35 второго элемента И, первый вход 36 элемента ИЛИ-НЕ, первый вход 37 первого элемента И, выход 38 буферного усилителя, информа- ционный вход-выход 39 приемопередат - чика, выход 40 первого элемента И.

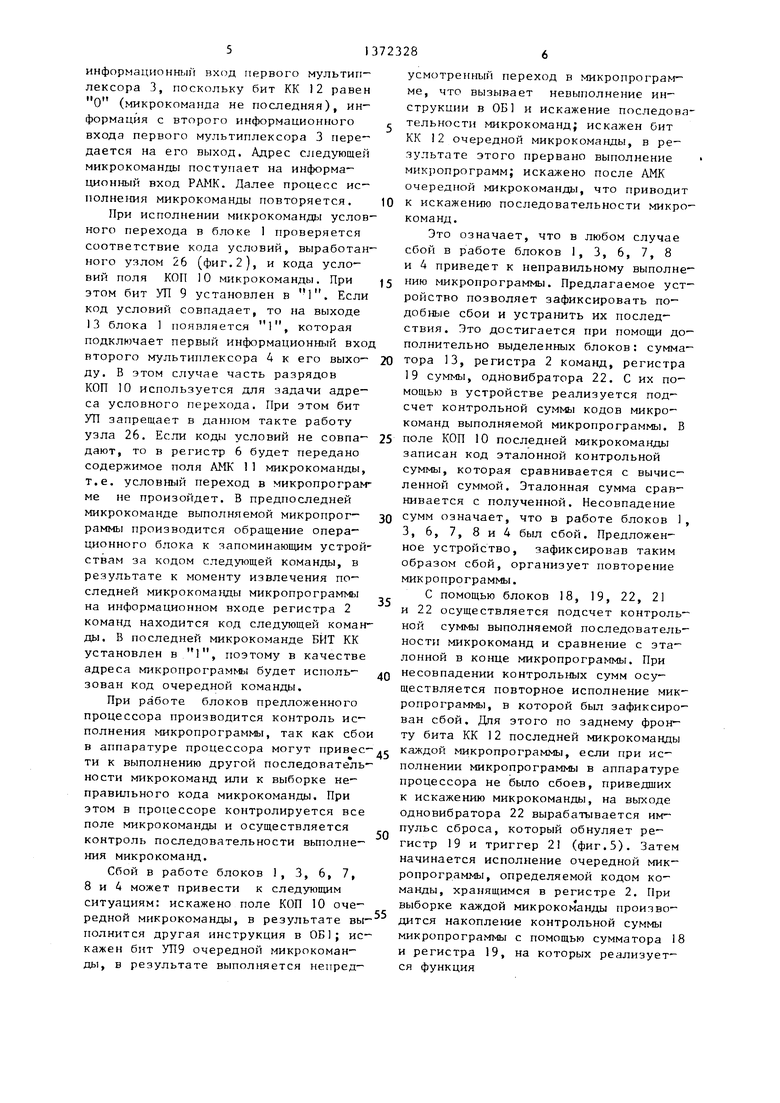

На фиг.З приведена схема, поясняющая синхронизацию работы блоков мик- ропрограммного процессора, где Ф1 - сигналы на первой линии синхронизации, Ф2 - сигналы на второй линии синхронизации.

На фиг.4 приведена временная диаг- вход 15 блока 1. При это м часть разрамма работы микропрограммного процессора в нормальном режиме, где Ф1 - синхросигналы на линии Ф1 24, Ф2 - синхросигналы на линии Ф2 25, РАМК -

рядов по линиям 31 через буфер 32 поступают на выход 16 блока 1 и являются управляющими сигналами процессора при обмене информацией с внешними

5 0 5 0

5

0

л.

адрес микрокоманды на выходе регистра 6, РК - код команды, записанный в регистре 2, КОП - поле КОП 10 микpoкoмaн ц I на выходе регистра 8, ИК - сигнал Конец команды на выходе регистра 8, УП - сигнал условного перехода нп выходе регистра В, 1Ш - сигнал на входе 13, PC - код ре- 1 истра 19, Сброс - сигнал сброса на выходе одновибратора 22.

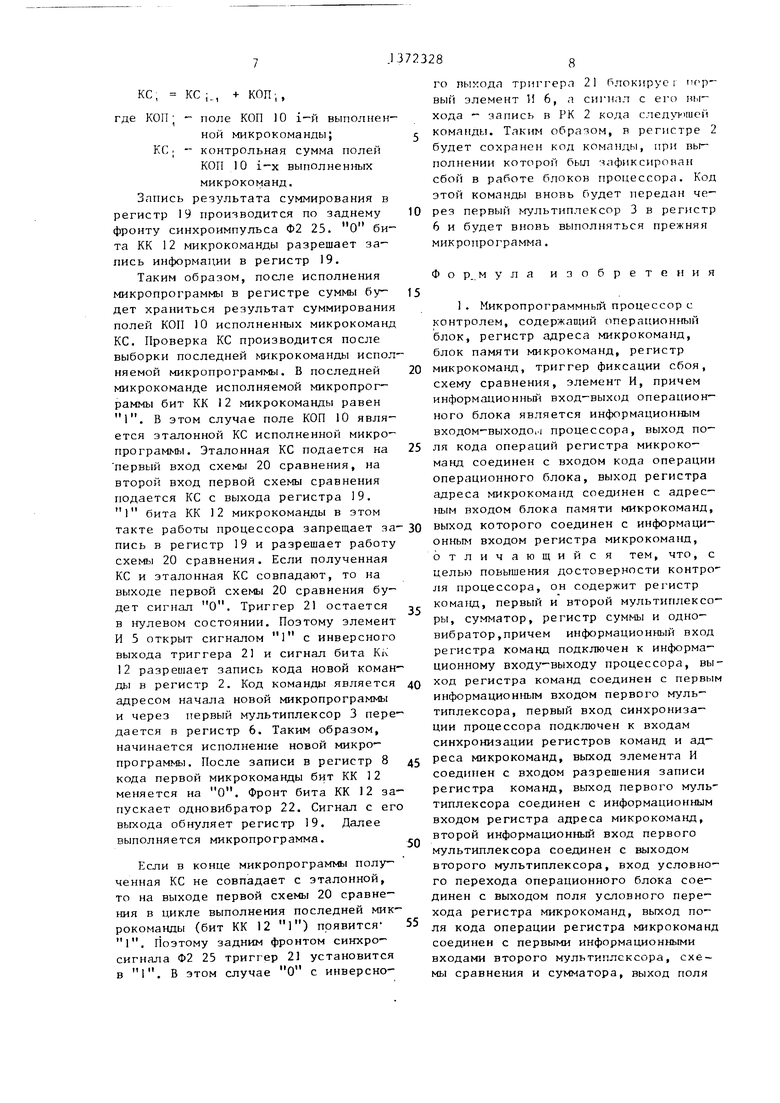

На фиг.5 приведена временная диаграмма работы микропрограммного процессора при наличии сбоя в его аппаратуре, где Ф1 - синхросигналы на линии Ф 24, Ф2 - синхросигналы на линии Ф2 25, РК - код команды, РАМК - адрес микрокоманды, КОП - поле КОП 10 микрокоманды, КК - сигнал бита КК 12, PC - код регистра 19, СС - сигнал на выходе первой схемы 20 сравнения, Сбой - сигнал на выходе триггера 21 фиксации сбоя,Сброс - сигнал сброса на выходе одновибрато- ра 22.

Микропрограммный процессор работает следующим образом.

Операционный блок 1 производит логическую и арифметическую обработки информации, поступающей на информационный вход 17 процессора из внешних устройств. При этом данные и адреса поступают в блок 1, а коды команд - в регистр 2. Команда, поступающая на вход регистра 2, порождает микропрограмму, вырабатываемую блоками 3, 4, 6-8 процессора. Микрокоманда микропрограммы управляет процес- |сом обработки информации в блоке 1 и процессом выборки следующей микрокоманды микропрограммы из блока 7. В процессе исполнения команды в регистре 2 хранится ее код, в регистре 6 - адрес следующей микрокоманды, в блоке 7 - коды микропрограмм, в регистре 8 - код исполняемой микрокоманды. Первый и второй мультиплексоры 3 и 4 управляют процессом формирования адреса следующей микрокоманды.

Операционный блок 1 функционирует следующим образом.

В качестве узла 26 может быть использована БИС К1804ВС2. Разряды поля КОП 10 микрокоманды поступают на

вход 15 блока 1. При это м часть разрядов по линиям 31 через буфер 32 поступают на выход 16 блока 1 и являются управляющими сигналами процессора при обмене информацией с внешними

устройствами. По линии 33 поля КОП 10 в блок 1 на управляющий вход приемопередатчика 27 поступает сигнал управления режимом работы приемопере- датчика: О - линии 17 подключены к информационному входу узла 26, 1 - информационный выход узла 26 подключается к шине 17 блока 1. По линиям 34 поля КОП 10 микрокоманды на управляющий вход узла 26 поступает код инструкции, который задает тип выполняемой инструкции, а именно арифметикологическое преобразование информации, находящейся во внутрен- них регистрах узла 26, прием информации с информационного входа узла 26 в один из внутренних регистров узла 26, выдачу информации из одного из внутренних регистров узла 26 на информационный выход узла 26. С выхода кода условий на первый вход схемы 28 сравнения поступают 4 бита условий, вырабатываемых схемами узла 26 при выполнении следующих операций: Z, результат равен С, бита переноса; V , есть переполнение; F, результат 0.

Внутренние схемы арифметического узла синхронизируются синхросигнала- ми Ф2 25, передаваемыми по синхроли- НИИ 35 на сиюсронизирующий вход узла 26. Поле условий из КОП 10.и биты условий из узла 26 используются для реализации условного перехода в микропрограммах процессора. Управляет условным переходом бит УП 9 микрокоманды, передаваемый с входа 15 блока 1 на второй вход второго элемента И 31. Если после исполнения за- данной операции код условий узла 26 и код условий на линиях ЗА совпадут, то на выходе схемы сравнения 28 появляется 1, и если бит УП 9 микрокоманды установлен в 1, т.е. проверяется условие перехода, то на выходе второго элемента И 31 появляется 1 сигнала подтверждения перехода 40, который подается с выхода 13

блока 1 на управляющий вход второго мультиплексора 4 и управляет процессом формирования адреса следующей микрокоманды микропрограммы.

Выполнение команд в предложенном, процессоре осуществляется следующим образом (фиг.З, 4).

Код исполняемой команды поступает на и}1формационный вход регистра 2.

с )0 15 20 25

зо -, Q 5

50

5

При этом на управляющем входе регистра 2 с выхода элемента И 5 подается 1, разрешающая запись коман/о : и р г- гистр 2. Запись в регистр 2 синхронизируется передним фронтом cинxpoи - пульса Ф1 24. 1 на выходе элемента И 5 появляется в ре: ультате того, что на его входы подаются: 1 с инверсного выхода триггера 21, поскольку последний в нормальном состоянии установлен в О, 1 бита КК 12 исполняемой микрокоманды, поскольку бит КК 12 в микрокоманде означает конец микропрограммы. Итак, последняя микрокоманда микропрограммы записывает код новой команды в регистр. Одновременно бит КК 12 запрещает работу блока 1. Это связано с организацией контроля функционирования процессора. Бит КК 12 управляет работой первого мультиплексора 3. 1 на его управляющем входе разрешает прохождение информации с его первого информационного входа на выход. Таким образом, с выхода регистра 2 код команды подается через первый мультиплексор 3 на информационный вход регистра 6. По заднему фронту синхросигнала Ф1 24 код команды записывается в регистр 6. Таким образом, код команды является адресом начала микропрограммы, реализующей данную команду.

Адрес микрокоманды с выхода регистра 6 подается на вход блока 7, с его выхода код считанной микрокоман- дь поступает на информационный вход регистра 8, в который микрокоманда записывается по переднему фронту синхросигнала Ф2 25. С выхода регистра 8 поля подаются следующие микрокоманды: бит УП9 на вход 14 блока 1 и включает схему выработки сигнала подтверждения перехода при реализации условного перехода в микропрограмме; поле КОП 10 на вход 15 блока 1 и управляет работой ОБ, а также подается в схему контроля работы процессора; поле АМК 11 через первый и второй мультиплексоры 3 и 4 в регистр 6 для выработки адреса следующей микрокоманды; бит КК 12, сигнализирующий о том, что исполняется последняя микрокоманда микропрограммы.

Исполнение микрокоманды в блоке 1 синхронизируется задним фронтом синхросигнала Ф2 25. Поле АМК II через второй мультиплексор 4, открытый сигналом О ПП 13, подается на второй

информационный вход первого мультиплексора 3, поскольку бит КК 12 равен о (микрокоманда не последняя), информация с второго информационного входа первого мультиплексора 3 передается на его выход. Адрес следующей микрокоманды поступает на информа- ционный вход РАМК. Далее процесс ис- 1юлне1шя микрокоманды повторяется.

При исполнении микрокоманды условного перехода в блоке 1 проверяется соответствие кода условий, выработанного узлом 26 (фиг,2), и кода условий поля КОП 10 микрокоманды. При этом бит УП 9 установлен в М, Если код условий совпадает, то на выходе 13 блока 1 появляется 1, которая подключает первый информационный вход второго мультиплексора 4 к его выхо- ду, В этом случае часть разрядов КОП 10 используется для задачи адреса условного перехода. При этом бит УП запрещает в данном такте работу узла 26, Если коды условий не совпа- дают, то в регистр 6 будет передано содержимое поля АМК 11 микрокоманды, т.е. условный переход в микропрограмме не произойдет, В предпоследней микрокоманде выполняемой микропрог- раммы производится обращение операционного блока к запоминающим устройствам за кодом следующей команды, в результате к моменту извлечения последней микрокоманды микропрограммы на информационном входе регистра 2 команд находится код следующей команды, В последнег микрокоманде БИТ КК установлен в 1, поэтому в качестве адреса микропрограммы будет исполь- зован код очередной команды,

При работе блоков предложенного процессора производится контроль исполнения микропрограммы, так как сбо в аппаратуре процессора могут привес ти к выполнению другой последовательности микрокоманд или к выборке неправильного кода микрокоманды. При этом в процессоре контролируется все поле микрокоманды и осуществляется контроль последовательности выполнения микрокоманд.

Сбой в работе блоков 1, 3, 6, 7, 8 и 4 может привести к следующим ситуациям; искажено поле КОП 10 очередной микрокоманды, в результате выполнится другая инструкция в ОБ 1; искажен бит УП9 очередной микрокоманды, Б результате выполняется непред-

0 5 о Q

5

0

5

усмотренный переход в микропрограмме, что вызывает невыполнение инструкции в ОБ и искажение последова- тельности микрокоманд; искажен бит КК 12 очередной микрокоманды, в результате этого прервано выполнение микропрограмм; искажено после АМК очередной микрокоманды, что приводит к искажению последовательности микрокоманд.

Это означает, что в любом случае сбой в работе блоков 1, 3, 6, 7, 8 и 4 приведет к неправильному выполнению микропрограммы. Предлагаемое устройство позволяет зафиксировать по- добнь е сбои и устранить их последствия. Это достигается при помощи дополнительно выделенных блоков : сумматора 13, регистра 2 команд, регистра 19 суммы, одновибратора 22. С их помощью в устройстве реализуется подсчет контрольной суммы кодов микрокоманд выполняемой микропрограммы. В поле КОП 10 последней микрокоманды записан код эталонной контрольной суммы, которая сравнивается с вычисленной суммой. Эталонная сумма сравнивается с полученной. Несовпадение сумм означает, что в работе блоков 1, 3, 6, 7, 8 и 4 был сбой. Предложенное устройство, зафиксировав таким образом сбой, организует повторение микропрограммы,

С помощью блоков 18, 19, 22, 21 и 22 осуществляется подсчет контрольной суммы выполняемой последовательности микрокоманд и сравнение с эталонной в конце микропрограммы. При несовпадении контрольных сумм осуществляется повторное исполнение микропрограммы, в которой был зафиксирован сбой. Для этого по заднему фронту бита КК 12 последней микрокоманды каждой микропрограммы, если при исполнении микропрограммы в аппаратуре процессора не было сбоев, приведших к искажению микрокоманды, на выходе одновибратора 22 вырабатывается импульс сброса, который обнуляет регистр 19 и триггер 21 (фиг.5). Затем начинается исполнение очередной микропрограммы, определяемой кодом команды, хранящимся в регистре 2. При выборке каждой микрокоманды производится накопление контрольной суммы микропрограммы с помощью сумматора 18 и регистра 19, на которых реализуется функция

КС, КС j, + КОП;

где КОП; - поле КОП 10 i-й выполненной микрокоманды; КС; - контрольная сумма полей КОП 10 i-X выполненных микрокоманд.

Запись результата суммирования в регистр 19 производится по заднему фронту синхроимпульса Ф2 25. О бита КК 12 микрокоманды разрешает запись информации в регистр 19.

Таким образом, после исполнения микропрограммы в регистре суммы будет храниться результат суммирования полей КОП 10 исполненных микрокоманд КС. Проверка КС производится после выборки последней микрокоманды испол-

няемой микропрограммы. В последней микрокоманде исполняемой микропрограммы бит КК 12 микрокоманды равен 1. В этом случае поле КОП 10 является эталонной КС исполненной микропрограммы. Эталонная КС подается на первый вход схемы 20 сравнения, на второй вход первой схемы сравнения подается КС с выхода регистра 19. 1 бита КК 12 микрокоманды в этом такте работы процессора запрещает за пись в регистр 19 и разрешает работу схемы 20 сравнения. Если полученная КС и эталонная КС совпадают, то на выходе первой схемы 20 сравнения будет сигнал О . Триггер 21 остается

в нулевом состоянии. Поэтому элемент И 5 открыт сигналом 1 с инверсного выхода триггера 21 и сигнал бита КК 12 разрешает запись кода новой команды в регистр 2. Код команды является адресом начала новой микропрограммы и через первый мультиплексор 3 передается в регистр 6. Таким образом, начинается исполнение новой микропрограммы. После записи в регистр 8 кода первой микрокоманды бит КК 12 меняется на О. Фронт бита КК 12 запускает одновибратор 22. Сигнал с его выхода обнуляет регистр 19. Далее выполняется микропрограмма.

Если в конце микропрограммы полученная КС не совпадает с эталонной, то на выходе первой схемы 20 сравнения в цикле выполнения последней микрокоманды (бит КК 12 1) появится- 1. Поэтому задним фронтом синхросигнала Ф2 25 триггер 21 установится в 1. В этом случае О с инверсно

10

15

20

5

0

5

О з

5

0

го пыхода триггера 21 блокирусi чор- вый элемент И 6, п сигнал с его i.i- хода - запись в РК 2 кода следчтиией команды. Таким образом, в регистре 2 будет сохранен код команды, при выполнении которой был зафиксирован сбой в работе блоков процессора. Код этой команды вновь будет передан через первый мультиплексор 3 в регистр 6 и будет вновь выполняться прежняя микропрограмма.

Фор. мула изобретения

1. Микропрограммный процессор с контролем, содержап1ий операционный блок, регистр адреса микрокоманд, блок памяти микрокоманд, регистр микрокоманд, триггер фиксации сбоя, схему сравнения, элемент И, причем информационный вход-выход операционного блока является информационным входом-выходОх- процессора, выход поля кода операций регистра микрокоманд соединен с входом кода операции операционного блока, выход регистра адреса микрокоманд соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, отличающийся тем, что, с целью повышения достоверности контроля процессора, он содержит регистр команд, первый и второй мультиплексоры, сумматор, регистр суммы и одно- вибратор,причем информационный вход регистра команд подключен к информационному входу-выходу процессора, выход регистра команд соединен с первым информационным входом первого мультиплексора, первый вход синхронизации процессора подключен к входам синхронизации регистров команд и адреса микрокоманд, выход элемента И соединен с входом разрешения записи регистра команд, выход первого мультиплексора соединен с информационным входом регистра адреса микрокоманд, второй информационный вход первого мультиплексора соединен с выходом второго мультиплексора, вход условного перехода операционного блока соединен с выходом поля условного перехода регистра микрокоманд, выход поля кода операции регистра микрокоманд соединен с первыми информационными входами второго мультиплексора, схемы сравнения и сумматора, выход поля

адреса микрокоманд регистра микрокоманд соединен с вторым информационным входом второго мультиплексора, управ ляющий.вход которого соединен с выхо- дом подтверждения перехода операцион- ного блока,второй вход синхрониза ции процессора подключен к входам синхронизации операционного блока, регистра суммы, регистра микрокоманд и триггера фиксации сбоя, выход поля конца команды регистра микрокоманд соединен с входом запуска одновибра- тора, управляющим входом схемы срав- нения, входом разрешения записи ре- гистра суммы, управляющим входом пер вого мультиплексора, первым входом элемента И и входом конца команды операционного блока,второй вход элемента И соединен с инверсным выходом триггера фиксации сбоя, выход сумматора соединен с информационным входом регистра суммы, выход которого соединен с вторыми информационными входами сумматора и схемы сравнения, выход которой соединен с информацион ным входом триггера фиксации сбоя, выход одновибратора соединен с входа- Ми сброса регистра суммы и триггера

узел, схему срг1внения, два элемента И, элемент ШД1-НЕ, приемопередат чик и буферный усилитель, причем ра ряды входа кода операций операционн го блока подключены к входу направл ния передачи приемопередатчика, к входу кода операций арифметического узла, к первому входу схемы сравнения и через буферный усилитель - к выходу управления обменом операцион ного блока, первый вход элемента ИЛИ НЕ является входом конца команды оп рационного блока, второй вход элеме та ИЛИ-НЕ и первый вход первого элемента И подключены к входу условног перехода операционного блока, второй вход первого элемента И соединен с выходом схемы сравнения, второй вход которой соединен с выходом кода усло вий арифметического узла, вход синхронизации которого соединен с выходо второго элемента И, первый вход кото рого является входом синхронизации операционного блока, второй вход вто рого элемента И соединен с выходом элемента ИЛИ-НЕ, информационные вход и выход арифметического узла соедине ны соответственно с информационными

фиксации сбоя, выход управления обме- ЗО выходом и входом приемопередатчика.

ном операционного блока является выходом управления обменом процессора.

2, Процессор по п.1, отличающийся тем, что операционный блок содержит арифметический

35

информационный вход-выход которого является информационным входом-выходом операционного блока, выход перво го элемента И является выходом подтверждения перехода операционного блока.

узел, схему срг1внения, два элемента И, элемент ШД1-НЕ, приемопередатчик и буферный усилитель, причем разряды входа кода операций операционного блока подключены к входу направления передачи приемопередатчика, к входу кода операций арифметического узла, к первому входу схемы сравнения и через буферный усилитель - к выходу управления обменом операционного блока, первый вход элемента ИЛИ- НЕ является входом конца команды операционного блока, второй вход элемента ИЛИ-НЕ и первый вход первого элемента И подключены к входу условного перехода операционного блока, второй вход первого элемента И соединен с выходом схемы сравнения, второй вход которой соединен с выходом кода условий арифметического узла, вход синхронизации которого соединен с выходом второго элемента И, первый вход которого является входом синхронизации операционного блока, второй вход второго элемента И соединен с выходом элемента ИЛИ-НЕ, информационные вход и выход арифметического узла соединены соответственно с информационными

выходом и входом приемопередатчика.

информационный вход-выход которого является информационным входом-выходом операционного блока, выход первого элемента И является выходом подтверждения перехода операционного блока.

Запись 6 Pff

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Устройство для управления цифровой вычислительной машиной | 1974 |

|

SU520591A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

Изобретерше относится к вычис и- тельной технике, в частности к процессорам с контролем. Пелью изобретения является повышение достоверности контроля микропрограммного процессора гтутем суммирования кодов микрокоманд и сравнения их суммы с контрольной суммой. В микропрограммный процессор с контролем дополнительно введены сумматор 18, регистр контрольной суммы 19, регистр команды 2, первый 3 и второй 4 мультиплексоры. Он также содержит операционный блок 1, регистр 6 адреса микрокоманд, блок 7 памяти микрокоманд, регистр 8 микрокоманд, схему сравнения 20, триггер фиксации сбоя 21, одновибратор 22, элемент И 5. 1 з.н. ф-лы, 5 ил. к

Запись 6

TSbiff

ПК

Запись

5дт

Запись б PC

уст %Сб

запись коп 5 06

Тисп МК, формиробоние

(PiL25

odpecQ /V/T

«-) «м

i

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-16—Подача