команд, выход признака условного перехода которого подключен к входу признака условного перехода операционкого блока и к первому входу сумма-. тора по модулю два, второй вход и выход которого подключены соответственно к перовму входу первого элемени- та ИЛИ и ко второму входу второго элемента РШИ, прямой выход триггера фиксации сбоев подключен к входу разре шения записи регистра микрокоманд, уп- равлякнций выход операционного блока подключен к выходу управления обменом процессора.

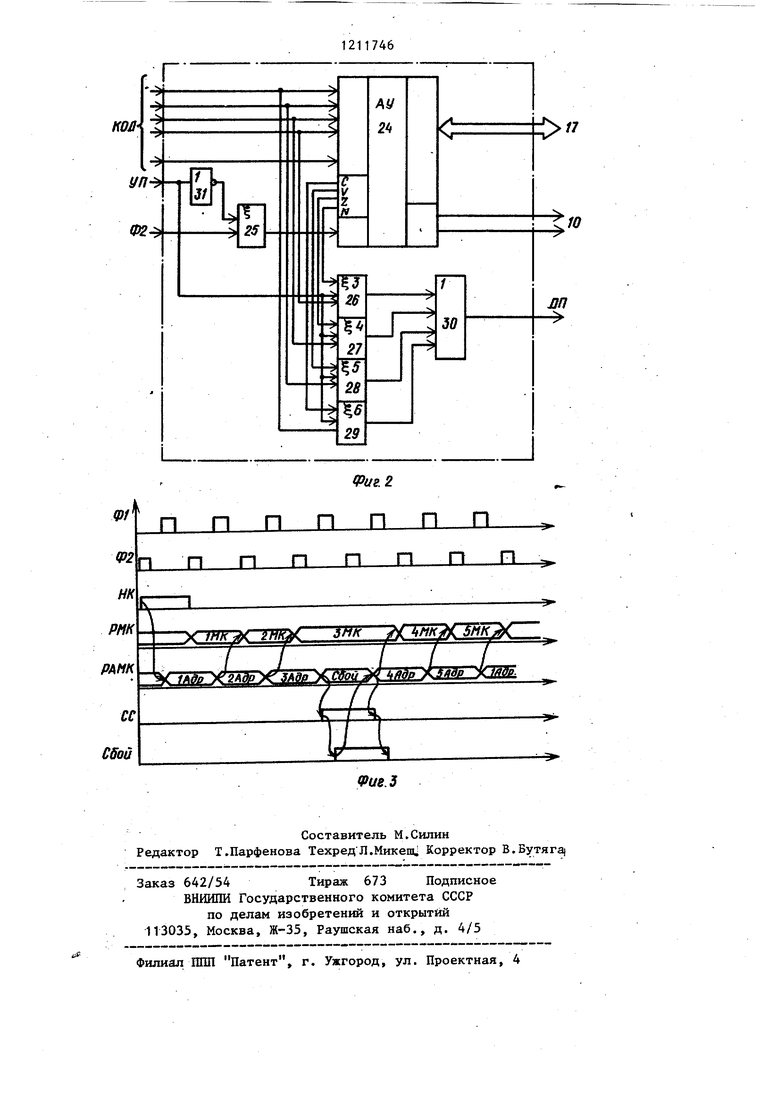

2. Процессор по п.1, о т л и чающийся тем, что операционный блок содержит арифметическое устройство, пять элементов И,элемент НЕ и элемент ИЛИ, причем вход кода операции арифметического устройства под- ключей к входу кода операции операционного блока, разряды (с первого по четвертый) входа кода операции операционного блока подключены к первым входам элементов И операционного блока соответственно с первого

Изобретение относится к вычисли- тзльной технике, в частности к про- ектированию процессоров с контролем и восстановлением при сбоях.

Целью изобретения является повышение быстродействия и достоверности функционирования.

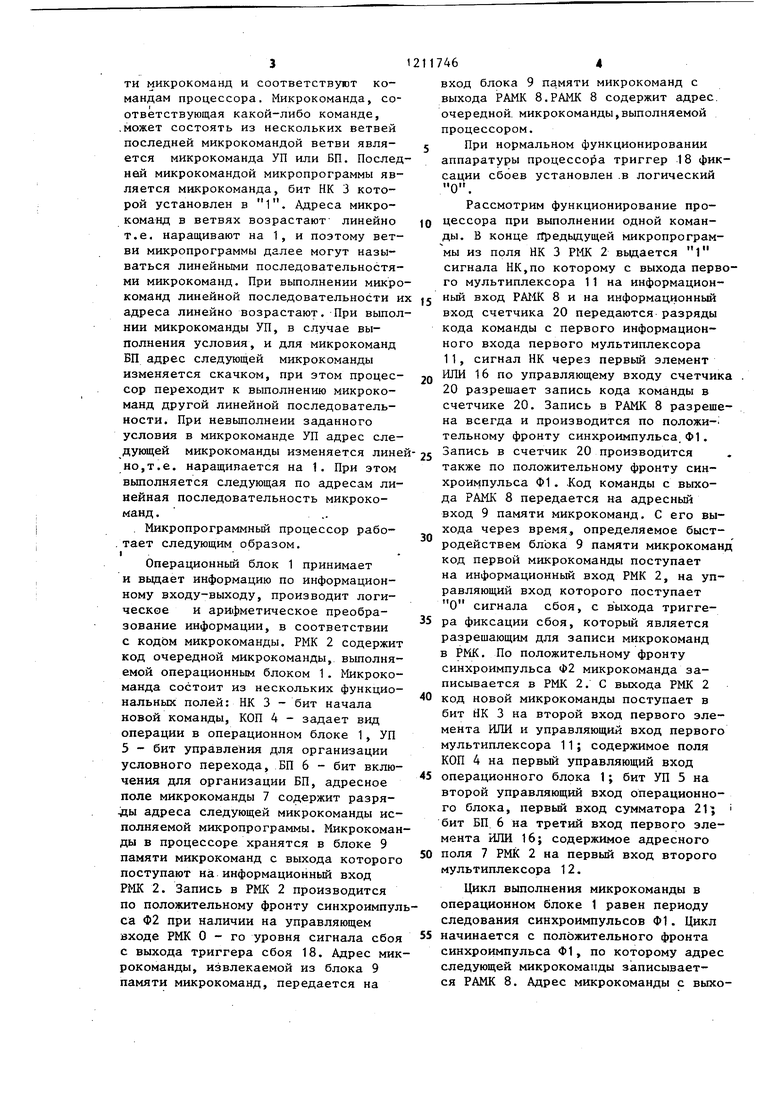

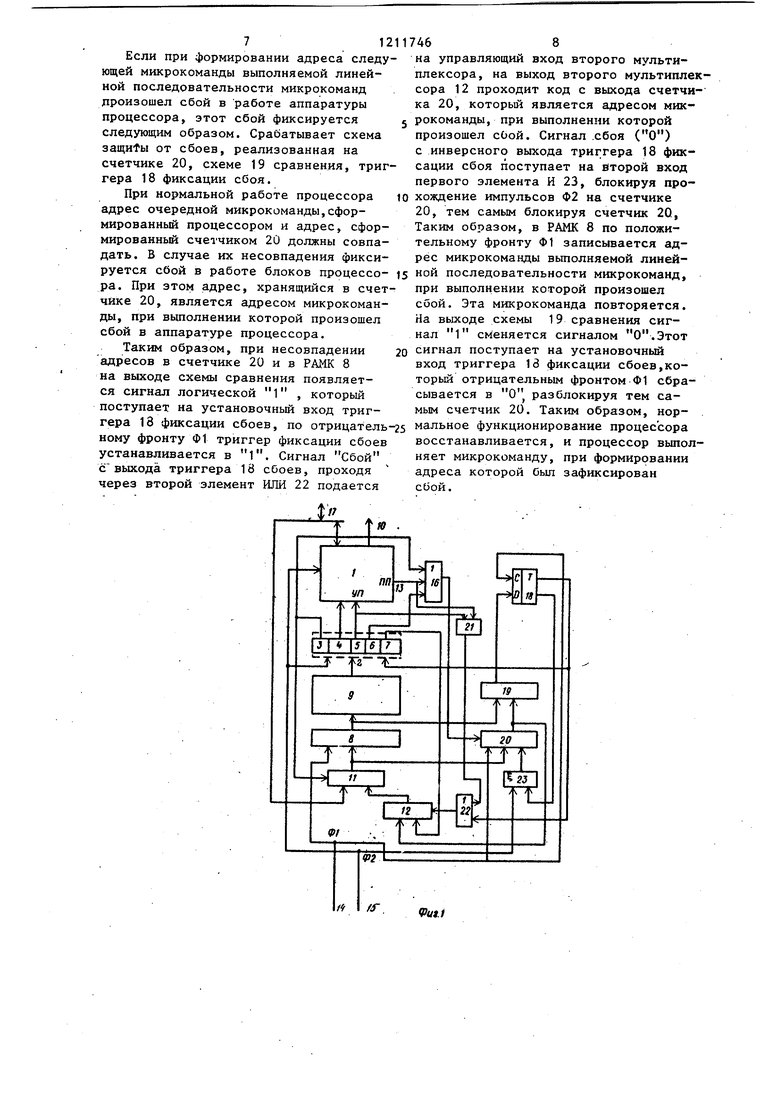

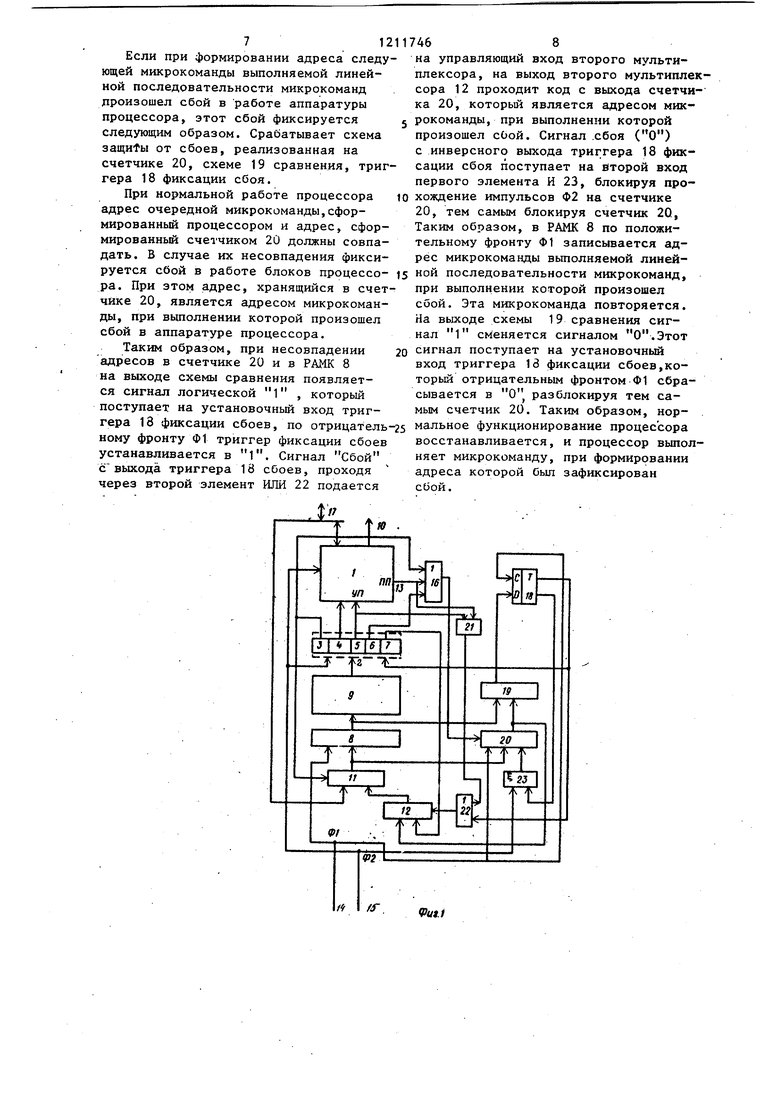

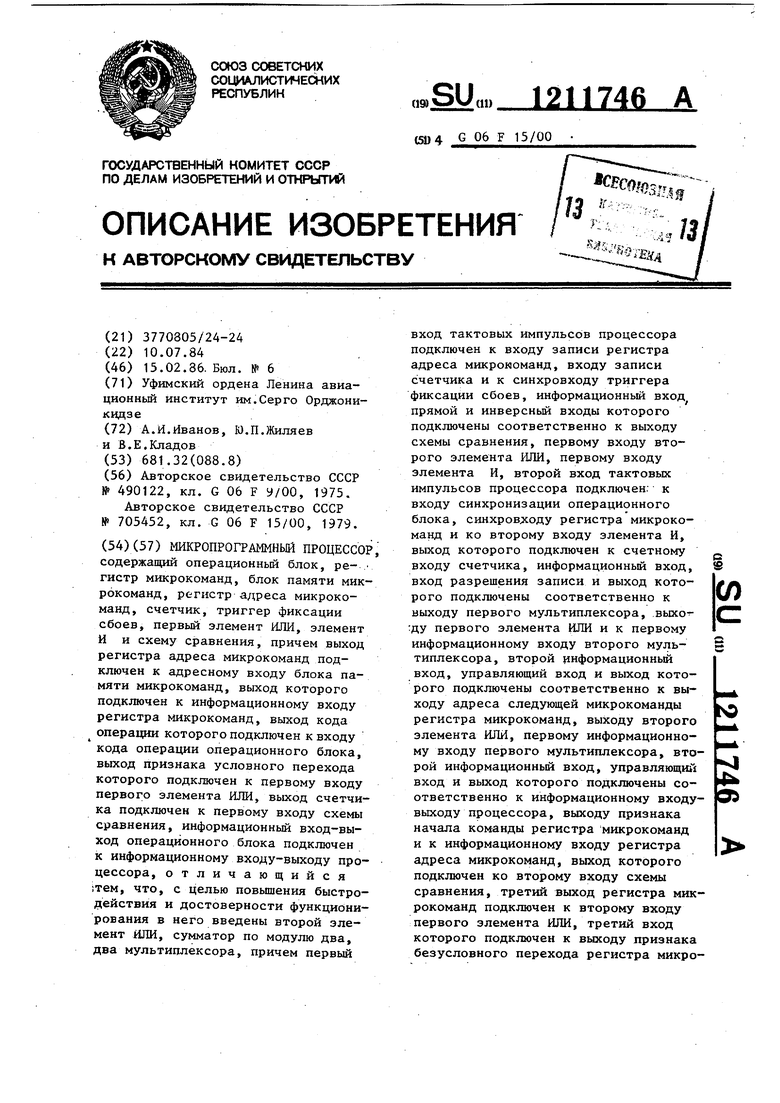

На фиг. 1 изображена функциональная схема процессора; на фиг. 2 - функциональная схема операционного блока; на фиг. 3 - временная диаграмма работы процессора.

Микропрограммньш процессор содержит операционньш блок 1, регистр 2 микрокоманд (РМК), поля признака; 3 - начала команды (НК), 4 - кода операции признака (КОП), 5 - условного перехода (УП) 6 - безусловного перехода (БП), 7 - адреса следующей микрокоманды, регистр 8 адреса микрокоманд (РАМК), блок 9 памяти микрокоманд, выход 10 управления обменом процессора, мультиплексоры 11 и 12, выход 13 подтверждения перехода, первый 14 и второй 15

по четвертый, вторые входы которых подключены к входу признака условного перехода операционного блока и к входу элемента НЕ, выход которого подключен к первому входу пятого элемента И операционного блока, второй вход и выход которрго подключены соответственно к входу синхронизации операционного блока и к входу синхронизации арифметического устройства, вьпсоды признаков переноса, равенства результата нулю, отрицательного результата и переполнения подключены соответственно к третьим входам элементов И операционного блока с первого по четвертьй, выходы которых подключены к входам элемента ИЛИ операционного блока, выход которого подключен к выходу признака усг ловного перехода операционного блока , информационньй вход-выход и выход признака готовности результата арифметического устройства подключены соответственно к информационному входу-выходу и управляющему выходу операционного блока.

входы тактовых импульсов процессора, элемент ИЛИ 16, информационньй вход-выход 17 процессора, триггер 18 фиксации сбоев, схему 19 сравнения, сч«тчик 20, сумматор 21 по модулю два, элемент ИЛИ 22, элемент И 23.

Операционный блок содержит арифметическое устройство 24, элементы И 25-29, элемент ИЛИ 30, элемент НЕ 31. На фиг. 3 приведена времмен- диафрагма работы микропрограммного процессора, где Ф1 - тактовые импульсы 14; Ф2 - тактовые импульсы

15, НК - сигнал начала команды; РМК - содержимое регистра микрокоманд; РАМК - содержимое регистра адреса микрокоманд; сбой - сигнал сбоя с выхода триггера сбоя 18;

СС - сигнал с выхода схемы сравнения 19. Арифметическое устройство 24 может быть реализовано на основе микросхемы К588ВС1.

Микропрограммы в предлагаемом

процессоре хранятся в блоке 9 памя10

ти микрокоманд и соответствуют командам процессора. Микрокоманда, соответствующая какой-либо команде, .может состоять из нескольких ветвей последней микрокомандой ветви является микрокоманда УП или БП. Последней микрокомандой микропрограммы является микрокоманда, бит НК 3 которой установлен в 1. Адреса микрокоманд в ветвях возрастают линейно т.е. наращивают на 1, и поэтому ветви микропрограммы далее могут называться линейными последовательностями микрокоманд. При выполнении микрокоманд линейной последовательности их jg адреса линейно возрастают. При выпол- нии микрокоманды УП, в случае выполнения условия, и для микрокоманд БП адрес следующей микрокоманды изменяется скачком, при этом процессор переходит к выполнению микрокоманд другой линейной последовательности. При невьшолнеии заданного условия в микрокоманде УП адрес слевход блока 9 памяти микрокоманд с выхода РАМК 8.РАМК 8 содержит адр очередной, микрокоманды,выполняемой процессором.

При нормальном функционировани аппаратуры процессора триггер 18 сации сбоев установлен .в логическ О.

Рассмотрим функционирование пр цессора при выполнении одной кома ды. В конце Предыдущей микропрогр мы из поля НК 3 РЖ 2 вьщается 1 сигнала НК,по которому с выхода п го мультиплексора 11 на информаци ньй вход РА11К В и на информационн вход счетчика 20 передаются разря кода команды с первого информацио ного входа первого мультиплексора 11, сигнал НК через первьй элемен ИЛИ 16 по управляющему входу счет 20 разрешает запись кода команды счетчике 20. Запись в РАМК 8 разр на всегда и производится по полож тельному фронту синхроимпульса. Ф1

20

дующей микрокоманды изменяется линей- 25 Запись в счетчик 20 производится

но,т.е. наращивается на 1. При этом выполняется следующая по адресам линейная последовательность микрокоманд. . Микропрограммньм процессор рабо-

.тает следующим образом. I

Операционный блок 1 принимает

и выдает информацию по информационному входу-выходу, производит логическое и арифметическое преобразование информации, в соответствии с кодом микрокоманды. РМК 2 содержит код очередной микрокоманды, выполняемой операционным блоком 1. Микрокоманда состоит из нескольких функциональных полей: НК 3 - бит начала новой команды, КОП 4 - задает вид операции в операционном блоке 1, УП 5 - бит управления для организации условного перехода, БП 6 - бит включения для организации БП, адресное поле микрокоманды 7 содержит разряды адреса следующей микрокоманды исполняемой микропрограммы. Микрокоманды в процессоре хранятся в блоке 9 памяти микрокоманд с выхода которого поступают на информационньй вход РМК 2. Запись в РМК 2 производится по положительному фронту синхроимпульса Ф2 при наличии на управляющем входе РМК 0-го уровня сигнала сбоя с выхода триггера сбоя 18. Адрес микрокоманды, извлекаемой из блока 9 памяти микрокоманд, передается на

30

35

40

также по положительному фронту си хроимпульса Ф1 . .Код команды с вых да РАМК 8 передается на адресный вход 9 памяти микрокоманд. С его хода через время., определяемое бы родействем блока 9 памяти микроко код первой микрокоманды поступает на информационный вход РМК 2, на равляющий вход которого поступает О сигнала сбоя, с в ыхода тригг ра фиксации сбоя, который являетс разрешающим для записи микрокоман в РМК. По положительному фронту синхроимпульса Ф2 микрокоманда за писывается в РМК 2. С выхода РМК код новой микрокоманды поступает бит НК 3 на второй вход первого э мента ИЛИ и управляющий вход перв мультиплексора 11; содержимое пол КОП 4 на первьй управляющий вход 45 операционного блока 1; бит УП 5 н второй управляющий вход операцион го блока, первый вход сумматора 2 бит БП 6 на третий вход первого э мента ИЛИ 16; содержимое адресног поля 7 РМК 2 на первый вход второ мультиплексора 12.

Цикл выполнения микрокоманды в операционном блоке 1 равен период следования синхроимпульсов Ф1. Ци начинается с положительного фронт синхроимпульса Ф1, по которому ад следующей микрокоманды записывает ся РАМК 8. Адрес микрокоманды с в

50

55

10

jg

2117464

вход блока 9 памяти микрокоманд с выхода РАМК 8.РАМК 8 содержит адрес, очередной, микрокоманды,выполняемой процессором.

При нормальном функционировании аппаратуры процессора триггер 18 фиксации сбоев установлен .в логический О.

Рассмотрим функционирование процессора при выполнении одной команды. В конце Предыдущей микропрограм- мы из поля НК 3 РЖ 2 вьщается 1 сигнала НК,по которому с выхода первого мультиплексора 11 на информацион- ньй вход РА11К В и на информационный вход счетчика 20 передаются разряды кода команды с первого информационного входа первого мультиплексора 11, сигнал НК через первьй элемент ИЛИ 16 по управляющему входу счетчика 20 разрешает запись кода команды в счетчике 20. Запись в РАМК 8 разрешена всегда и производится по положи-, тельному фронту синхроимпульса. Ф1.

20

Запись в счетчик 20 производится

также по положительному фронту синхроимпульса Ф1 . .Код команды с выхода РАМК 8 передается на адресный вход 9 памяти микрокоманд. С его выхода через время., определяемое быст- родействем блока 9 памяти микрокоманд код первой микрокоманды поступает на информационный вход РМК 2, на управляющий вход которого поступает О сигнала сбоя, с в ыхода триггера фиксации сбоя, который является разрешающим для записи микрокоманд в РМК. По положительному фронту синхроимпульса Ф2 микрокоманда записывается в РМК 2. С выхода РМК 2 код новой микрокоманды поступает в бит НК 3 на второй вход первого элемента ИЛИ и управляющий вход первого мультиплексора 11; содержимое поля КОП 4 на первьй управляющий вход операционного блока 1; бит УП 5 на второй управляющий вход операционного блока, первый вход сумматора 21 бит БП 6 на третий вход первого элемента ИЛИ 16; содержимое адресного поля 7 РМК 2 на первый вход второго мультиплексора 12.

Цикл выполнения микрокоманды в операционном блоке 1 равен периоду следования синхроимпульсов Ф1. Цикл начинается с положительного фронта синхроимпульса Ф1, по которому адрес следующей микрокоманды записывается РАМК 8. Адрес микрокоманды с выхо

да 8 передается на вход блока 9 памяти микрокоманд. На выходе блока 9 памяти 1Л1Крокоманд с задержкой, равной времени считывания, появляется код микрокоманды. К моменту появления синхроимпульса Ф2 на синхронизирующем входе РМК 2 на информационном входе РМК 2 устанавливается код микрокоманды. Запись в РМК производит- ,ся по положительному фронту синхроим- 10 ИЛИ 16 и подается на управляющий пульса Ф2 . После этого в операцион- вход счетчика 20, разрешая запись, ном блоке 1 начинается выполнение Адресное поле 7 РМК 2 содержит адКод условия, .заданного в поле КОП 4 РМК 2, сравнивается с выработанными признаками результата операции в операционном блоке 1. В случае совпадения кодов условия с кодом признаков результата на пер вом управляющем выходе операционного блока появляется 1, которая проходит на выход первого элемента

новой микрокоманды.

При выполнении арифметико-логичеких микрокоманд цикл повторяется.

Для микрокоманд безусловного перехода формирование адреса следующей микрокоманды осуществляется следующим образом. Поскольку бит БП 6 в РМК 2 установлен в 1, то на выходе первого элемента ИЛИ 16 появляется 1, которая подается на управляющий вход счетчика 20, разрешая запись в него. На первом управляющем выходе операционного блока 1 - О, поэтому на управляющем входе второго мультиплексора 12 - О, поскольку на обоих входах второго элемента ИЛИ 22 логические О. Таким образом, в счетчик 20 и в РАМК 8 положительным фронтом Ф1 записывается адрес новой линейной последовательности микрокоманды с адре сногр поля 7 РМК 2. После этого извлекается первая микрокоманда новой последовательности.

.Формулирование адреса следующей микрокоманды для микрокоманд условного перехода производится следующи образом. Бит УП 5 РМК 2 для микрокоманд условного перехода установлен в 1 и передается на второй управляющий вход операционного блока 1. Первые 4 разряда поля КОП 4 РМК 2 в этих микрокоманд содержат код условия, которое должно быть выполнено при реализации условного перехода. Условием могут быть признаки результата, вырабатывающиеся в операционном блоке 1 при выполнении арифметико-логических микрокоманд: равенство нулю результата операции; отрицательный результат операций; переполнение разрядной сетки при выполнении арифметических операций; установка бита переноса при сдвигах и арифметических операциях.

ИЛИ 16 и подается на управляющий вход счетчика 20, разрешая запись, Адресное поле 7 РМК 2 содержит адКод условия, .заданного в поле КОП 4 РМК 2, сравнивается с выработанными признаками результата операции в операционном блоке 1. В случае совпадения кодов условия с кодом признаков результата на первом управляющем выходе операционного блока появляется 1, которая проходит на выход первого элемента

реса перехода, которые передаются через второй 12 и и первьй 11 мультиплексоры на информационный вход РАМК 8 и информационный вход счетчика 20, поскольку на управляющий вход второго мультиплексора поступает О с выхода сумматора 21, на первый

вход которого поступает логическая 1 бита УП 5 микрокоманды, а на второй вход - логическая 1 сигнала 13 подтверждения перехода (ПП), а на управляющий вход первого мультиплек

сора подается логический О бита НК 3 микрокоманды.

По положительному фронту Ф1 производится запись в РАМК 8 и счетчик

20 адреса условного перехода в в.ьшол- няемой процессором микропрограмме. В случае несовпадения кода условия с кодом признаков результата на вы- ходе 13 и следовательно, на втором входе сумматора 21 находится логический О, в то время как на первом входе сумматора 21 - логическая 1. На выходе сумматора 21 находится 1, за счет чего на выходе второго элемента ИЛИ 22 - 1, и второй вход второго мультиплексора 12 коммутируется с его выходом, тем самым разрешая прохождение на вход РАМК 8 адреса следующей микрокоманды с выхода счетчика 20. Поскольку на управляющем входе 20 находится О с выхода первого элемента ИЛИ 16, запись в счетчик 20 запрещена. Содержимое счетчика 20 является адресом следующей микрокоманды выполняемой линейной последовательности микрокоманд, поскольку к моменту появления синроимпульса Ф1 к содержимому счетчику 20 была прибавлена 1. Таким образом, перехода не происходит

и из блока 9 памяти микрокоманд извлекается следующая микрокоманда выполняемой линейной последовательности- микрокоманд.

ющей микрокоманды выполняемой линейной последовательности микрокоманд произошел сбой в работе аппаратуры процессора, этот сбой фиксируется следующим образом. Срабатывает схема защи-Гы от сбоев, реализованная на счетчике 20, схеме 19 сравнения, триггера 18 фиксации сбоя.

При нормальной работе процессора адрес очередной микрокоманды,сфор- мированньй процессором и адрес, сфор- мироваиньй счетчиком 20 должны совпадать. В случае их несовпадения фиксируется сбой в работе блоков процессо- ts последовательности микрокоманд, ра. При зтом адрес, хранящийся в счет- при выполнении которой произошел

чйке 20, является адресом микрокоманды, при выполнении которой произошел сбой в аппаратуре процессора.

Таким образом, при несовпадении адресов в счетчике 20 и в РАМК 8 на выходе схемы сравнения появляется сигнал логической 1 , который поступает на установочньй вход тригсбой. Эта микрокоманда повторяется. На выходе схемы 19 сравнения сигнал 1 сменяется сигналом О.Этот 20 сигнал поступает на установочный вход триггера 13 фиксации сбоев,ко- торьй отрицательным фронтом-Ф сбрасывается в 0 разблокируя тем самым счетчик 20. Таким образом, норгера 18 фиксации сбоев, по отрицатель-25 мальное функционирование процессора ному фронту Ф1 триггер фиксации сбоев восстанавливается, и процессор выпол- устанавливается в 1. Сигнал Сбой няет микрокоманду, при формировании с выхода триггера 18 сбоев, проходя адреса которой был зафиксирован через второй элемент ИЛИ 22 подается сбой.

плексора, на выход второго мультиплексора 12 проходит код с выхода счетчика 20, который является адресом мик5 рокоманды, при выполнении которой произошел сОой. Сигнал .сбоя (О) с инверсного выхода триггера 18 фиксации сбоя поступает на второй вход первого элемента И 23, блокируя про10 хождение импульсов Ф2 на счетчике 20, тем самым блокируя счетчик 20, Таким образом, в РАМК 8 по положительному фронту Ф1 записывается адрес микрокоманды вьтолняемой линейсбой. Эта микрокоманда повторяется. На выходе схемы 19 сравнения сигнал 1 сменяется сигналом О.Этот 20 сигнал поступает на установочный вход триггера 13 фиксации сбоев,ко- торьй отрицательным фронтом-Ф сбрасывается в 0 разблокируя тем самым счетчик 20. Таким образом, норVutt

9/

п п п п пDа

Cffou

Составитель М.Силин Редактор Т.Парфенова Техред Л.Микеш Корректор В.Бутяга)

Заказ 642/54 Тираж 673 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

9ие.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор с контролем | 1986 |

|

SU1372328A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-10—Подача