Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УБМ), работающих в реальном масштабе.времени.

Целью изобретения является повышение достоверности и оперативности контроля устройства.

На чертеже представлена функцио- нальная схема устройства,

Устройство содержит первый блок 1 памяти, группу элементов ИЛИ 2, группу триггеров 3 прерьшаний, элемент 2И-14ПИ 4, триггер 5 ошибки, элемент И 6, первьй 7, второй 8 и четвертью 9 элементы НИИ,, регистр 10 счетчик, 11 я триггер 12 фиксации пре- рываний второй блок 13 памяти, мультиплексор 14,, третий элемент ИЛИ 15 и входы 16-20 устройства для подключения к выходам контролируемой вычислительной машины.

Устройство для контроля управ- ляюш1ей вычислительной машины может быть использовано в системах-автоматического управления, построенных на базе УВМ, работающей по жесткой програм е в реальном мз.сштабе вре-- мени. Оперативный контроль за ходом вычислительного процесса, осуществляемый в устройстве, для: контроля 1ГШ базируется на двух принципахs контроль правильности порядка включения в работу подпрограм обслуживания .прерываний от внешни: з стройств, кон тро ль. правильности порядка обращений к ПЗУ, ОЗУ и внешним устройствам в процессе выполнения каяэдой команды. Обе контрольные функ цкк хорошо дополняют друг друга.. Это относится и к собственно процессу контроля, где первая контрольная функция, надежно защищающая внешние устройства от не- санкционированного управления, но не обладающая по отношению к другим частям программы достоверностью и оперативностью, дополняется второй функцией,, подвергающей контролю процесс выполнения каж,1 ой команды во всех частях програм 1Ы и, следовательно, повьш5ающей достоверность контроля Это относится и к аппаратной реализации предлагаемого устройства, где первая и вторая ко 1трольные функции используют первьш блок 1 памяти, в котором тр(тий и четвертый информационные вькоды служат для

реализации второй контрольной функции.

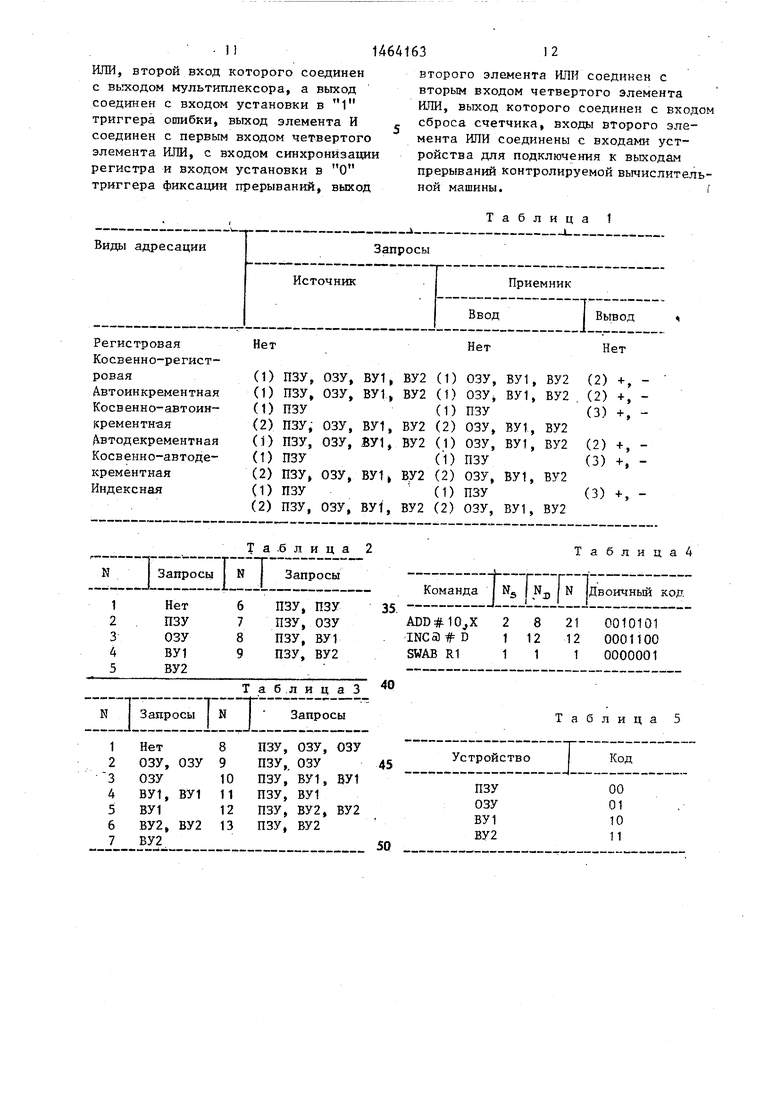

Рассмотрим подробнее вторую контрольную функцию. Она заключается в - том, чтобы хранить в первом блоке 1 памяти для каясдой команды ее расписание запросов к ПЗУ, ОЗУ и внешним устройствам. В процессе реального исполнения каждой команды проходит реальная серия запросов по линиям запросов управляющей вычислительной машины, которые заведены также в устройство для контроля УВМ (входы 16 запросов устройства). Происходит сравнение реальной серии запросов с той, которая должна быть для данной команды, и в случае несовпадения вырабатывается сигнал сбоя. Для примера будем считать, что управляющая вычислительная машина построена на основе МПК БИС с системой команд Электроника-60, например, на основе МПК БИС КР588. Оценим возмож- ное многообразие расписаний запросов при вьтолнении одной команды в данном конкретном случае. Будем считать что в системе содержится два внешних устройства, т„е. вырабатывается четыре различных запроса: ПЗУ, ОЗУ, ВУ1, ВУ2. Запросы здес вырабатываются на трех фазах исполнения команды; фазе выборки команды, фазе источника и фазе приемника. На фазе вы- борки команды всегда вырабатьтается один и тот же запрос - запрос ПЗУ. Запросы, которые вырабатываются на фазах источника и приемника, зависят от вида адресации соответственно источника и приемника. В табл.1 приведена эта информация, причем цифрой в скобах обозначен вид адресации источника или приемника (порядковый номер запроса на данной фазе), аза цифрой перечислены альтернативные виды запросов. Например, если в команде источник имеет косвенно-автоинкремент- ньш вид адресации, то на фазе источника будут выработаны два запроса: первьй - запрос ПЗУ, а второй - запрос одного из четырех перечисленных устройств в зависимости от конкретного адреса. Далее,, если в этой команде приемник имеет индексный вид адресации, то на фазе приемника будут выработаны два или три запроса: первые два вырабатываются на подфа- зе ввода и полностью аналогичны опи- санньм, а третий вырабатывается или

не вьфабатывается на подфазе вывода в зависимости от типа команды. Например, команда SUB (вычесть) производит вывод вычисленного значения, и запрос вырабатывается, а команда СМР (сравнить) работает аналогично, но вьюода не производит. Запрос на подфазе вывода (если он вырабатывается) всегда вырабатывается по отношению к тому же устройству, что и предыдущий запрос на подфазе ввода (откуда ввели- туда и выводим), поэтому возможные альтернативы заключаются здесь в его наличии или отсутствии, что и обозна чено знаками + или -. В табл.2 в явном виде приведено многоббразие расписаний запросов на фазе источника, которое получено из табл.1.

В табл.3 приведено многообразие расписаний запросов на фазе приемника, которое также получено из табл.1. .

Пример. Расписание запросов для нескольких команд.

1) ADD 10,X X Код команды 062767 000010 ХХХХХХ

Источник имеет автоинкрементный вид адресации и расположен в ПЗУ, а приемник имеет индексный вид адресации и расположен в ОЗУ, поэтому расписание запросов имеет вид

ПЗУ ПЗУ ПЗУ,ОЗУ,ОЗ Фаза выборки Фаза источни- Фаза при- команды ка емника

2) INC Э D D - регистр ВУ2 Код команды 005237

ХХХХХХ .

В этой команде источник отсутствует, поэтому связанных с ним запросов нет. Приемник имеет косвенно-автоинкрементный вид адресации и рас- положен в ВУ2, поэтому расписание запросов имеет вид

000301

ПЗУ, ВУ2, ВУ2 Фаза приемника 55

В этой команде источник отсутствует, поэтому связанных с ним запросов нет. Приемник имеет регистровую адресацию (является регистром R1),. поэтому связанных с ним запросов также нет, и расписание запросов будет имеет вид

ПЗУ Фаза выборки команды

Поскольку могут встретиться любые сочетания источника и приемника, то общее число возможных расписаний запросов в процессе вьтолнения одной команды равно 117 Все это множество расписаний нумеруется ледующим образом. Пусть N - номер расписания запросов на фазе источника согласно табл.2, а Njj - номер расписания запросов на фазе приемника согласно «табл.3, тогда номер расписания зап- росов для команды, имеющей такие источник и приемник, будет

N

13(N5 - 1) + N.

Для двоичного кодирования такой нумерации достаточно семь разрядов. В качестве примера приведем номера и двоичные коды расписаний запросов для рассмотренных команд, представленные в табл.4.

Из первого блока 1 памяти, из ячейки, адрес которой определяется кодом текущей команды, считывается с его третьих выходов (С - D,) соответствующий семиразрядный код расписания запросов. Часть схемы, состоящая из элемента И 6, первого 7 и четвертого 9 элементов ИЛИ, регистра 10, счетчика 11 и второго блока 13 памяти, служит для временной развертки закодированного расписания запросов, причем синхроимпульсами развертки служат реальные сигналы запросов, поступающие на входы запросов устройства 16. Код расписания запросов является адресом соответствующей зоны во втором блоке 13 памяти. Адрес зоны вводится во второй блок 13 памяти через его первые адресные входы (разряды А, - А-;). Число запросов в одном расписании не превышает шести, поэтому каждая зона состоит из восьми слов, адресуемых тремя разрядами Ag - А, (вто10

5Н64163

рые адресные входы второго блока памяти) о Двухразрядные скоза, хранящиеся во втором блоке памяти, являются кодами запрашивг. устройств так, как это показано s табл.5,

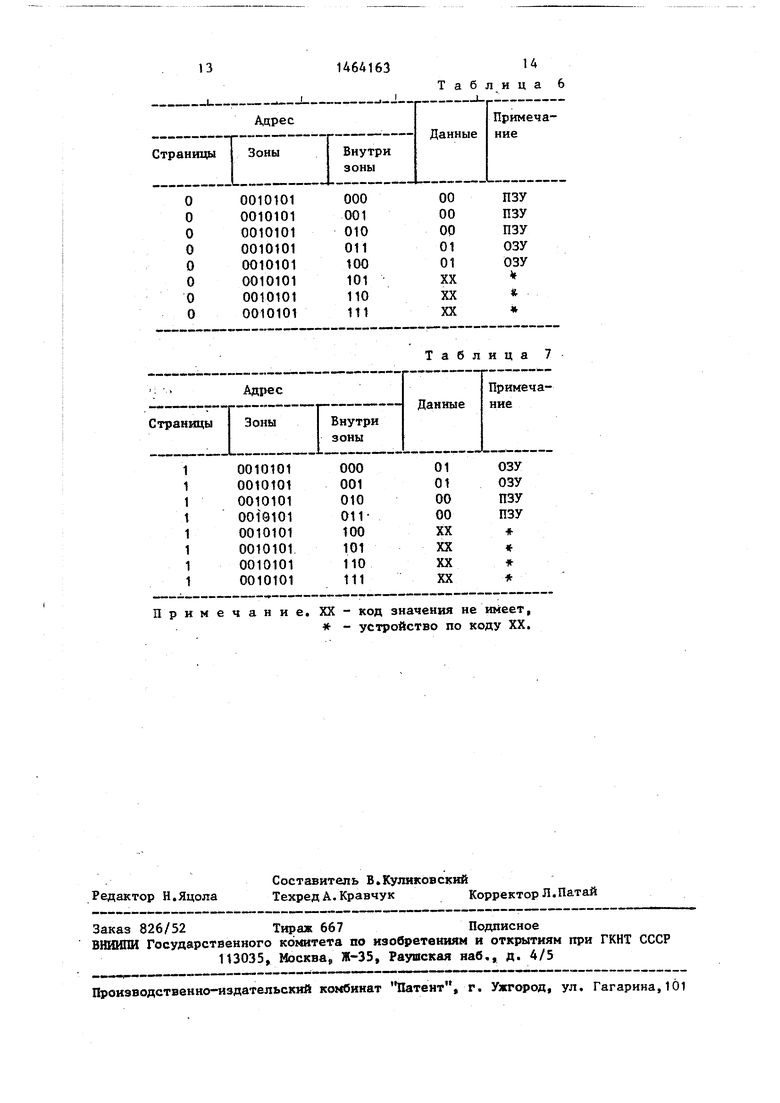

Таким oepasoMj в каждой зоне втоого блока. 13 памяти посггедовательно записаны коды запрашиваемых устройств согласно тому расписани о запросов, код которого адресует эту зону. В качестве rrpi-iMepa в табл«6 показана одна зона второго блока .3 памяти. Она а,цресуется кодом 0010101 (21) и, следовательно, соответствует рас- писанию запросов номер 2. Все ад- ресное пространство второго блока 13 памяти разбито на две страншда. Раз рядом адреса страницы является А (третий а дресньш вход),, Все сказанное о зонах второго блока 13 памяти относится только к его странице О о Необходимость страницы 1 вызвана следуюЕ1;иМо В управляющей вычислительной матине после предоставления пре- рьшання внешнему устройству, но еще до начала исполнения пер)зой команды из программы обработки щзерывания, по линиям запросов четыре

ви со ма те пр от ве та ад да пе -jg со ци хо К му ме ус ны с че ча ко на и

20

25

во

запроса; ОЗУ,, ОЗУ, ПЗУ, ПЗУ. Они связаны с занесением д.3:у:-с слов в ОЗУ (слово состояния программы и счетчик команд) и извле;Ч2ния двух слов из ПЗУ (noBbLH счетчик команды и новое слово состояния: программы) . Эти запросы ни с какигс-г :к:омандами програгдаз не связаны, и поэтому не могут, быть учтены на странице О, Для их учета предназначена страница 1,, все зоны которой икают одинаковое содержание,, в табл. 7, в частности, приведена одна из ,ни-х.

Сигнал на входе 17 сброса устройства, а также сигналы прерываний имеют высокий ак7 ивный уровень. Сигналы на входе 20 прерываний устройства являются сигнал,ами предоставления прерываний управ:аяющей вычислительной мапшны, а следовательно, появляются только послр завершения команды во время которой появилось требование прерывания« Появление сигналов на входе 20 прерываний устройства до завершения серии запросов принадлежащих текущей команде, невозможно

Устройство 4)унк що11ирует следующим образом

Сначала рассмотрим контроль правильности последовательности запросов в процессе вьшолнения каждой команды. Контролируемая УВМ последовательно выполняет команды основной программы в нормальном состоянии при отсутствии сбоев в работе УВМ. Блоки 1 и 13 памяти заранее прошиты в соответствии с правилами, приведенными в табл. 2., 3, 6, 1, После установления адресной информации на адресных входах 19, на информационных выходах первого блока 1 памяти появляется g соответствующая информация. Информа- ционньй разряд D, (четвертый выход) является при этом индикатором Команда - данные. Если по текущему адресу в основной программе размещен код команды, то разряд D, устанавливается в 1, а если данные - в О. Таким образомS импульс с управляющего входа 18 проходит через элемент И б только в том случае, если текущий адрес - адрес команды,, В этом случае он поступает на вход синхронизации регистра 10, и информация с третьих выходов пер0

5

вого блока 1 памяти (Б,, - В, ) , явяющаяся кодом расписания запросов анной команды, записывается в per гистр 10. Одновременно зтот Ш шульс через четвертый элемент ИЛИ 9 обнуяет счетчик 11 и устанавливает в

О триггер 12 фиксации прерываний. Таким образом, перед началом серии запросов, соответствуюпцгх данной команде, на первых адресных входах (А, - А) второго блока 13 памяти

установлен код расписания запросов, который сохраняется там вплоть до появления следующей команды, т.е. в течение всей серии запросов.

Триггер 12 находится в О, т.е„

во втором блоке 13 памяти выбрана страница 0. Счетчик 11 обнулен, т.е. установлен адрес начала соответствующей зоны страницы 0. Информация с выхода второго блока 13 памяти поступает на адресные входы мультиплексора 14. Все готово к прргходу серии запросов При появленш-г первого из них по любой из линий 16 на выходе первого элемента ИЛИ 7 появляется

импульс с высоким активным уровнем. Он поступает на вход синхронизации мультиплексора 14, коммутируя один из его информационных входов с выходом в соответствии с информацией

на адресных входах. Если импульс запроса пришел по расписанизо,

открывается именно тот канал мультиплексора, который связан с линией, по которой пришел импульс запроса. Например, если по расписанию пришел импульс Запрос ПЗУ, то с выходом мультиплексора будет соединен информационньш разряд D . Следовательно, сигнал на выходе мультиплексора Ьудет продолжать иметь низкий уровень, поскольку на входе открывшегося канала мультиплексора находится сигнал запроса с низким активным уровнем.

После того как импульс запроса закончится, сигнал снимется с входа синхронизации мультиплексора 14, все его каналы закрыты, и сигнал на его выходе продолжает иметь низкий уровень. Одновременно фронтом 1-0 т сигнала на счетном входе счетчика 11 код счетчика наращивается на единицу и будет адресовать следзгтощее слово в рассматриваемой зоне второго блока 13 памяти. Теперь устройство готово к приходу следующего импульса запроса.

После прохождения всех импульсов запроса, соответствующих данной команде, могут иметь место два продолжения. Первое - это выборка следующей команды с обнулением счетчика 11, триггера 12 и записью в регистр 10

6Д1638

рается первая команда из програмг-1Ы обработки прерывания, и процесс

работы устройства продолжается так, как описано.

Если в работе контролируемой УБМ возникнет сбой, который иршзо,1ит к нарушению порядка следования импульсов запроса, то это будет немедленно

10 обнаружено. Пусть, напр1даер, в какой то момент выполнения команды должен поступить импульс Запрос ПЗУ. Это выражается в том, что на адресные входы мультиплексора 14 будет подаг;

15 код 00. Вместо импульса З-апрос ПЗУ поступает, например, импульс Запрос ВУ1. Это приводит к тому, что открывается канал мультипле1ссора D , а сигнал высокого уровня (на D импуль-.

с.а запроса нет, и уровень неактив ный высокий) поступает на выход мультиплексора. После окончания импульса запроса мультиплексор закрывается, и уровень -сигнала на его выходе снова становится низким. Таким образом, при поступлении на вход 16 запросов импульса запроса не по расписанию, на выходе мультиплексора 14 сразу же возникает импульс.

Этот импульс через третий зл1 ;мент ШП 15 устанавливает в 1 триггер 5 ошибки, сигнализируя о том, что произошел сбой.

Рассмотрим контроль правильности

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1988 |

|

SU1539785A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

нового кода расписания запросов, пос- 5 включения в работу подпрограмм обслуживания прерываний от внешних у ройств. Функционирование этой части схемы, содержащей первый блок 1 nai ти (задействованы первые и вторые

ле чего весь описанный процесс повторяется. Второе - приход импульса с входов 20 прерываний, что соответствует предоставлению-прерывания одному из ВУ. В этом случае на выходе второго элемента ИЛИ 8 появляется импульс с высоким активным уровнем, который через четвертьй элемент ИЛИ 9 обнуляет счетчик 11 и устанавливает в 1 триггер 12, Теперь, перед приходом серии запросов ОЗУ, ОЗУ, ПЗУ, ПЗУ, которая всегда имеет место при 1редоставлейии прерывания, триггер 12 адресует страницу t во втором блоке 13 памяти, а счетчик 11 указы- Baet на начало зоны, причем неважно какая именно это зона, так как на странице 1 все они одинаковы. При правильном прохождении этой серии сигнал на выходе мультиплексора 14 имеет низкий уровень точно так же, как это описано.

После того, как рассматриваемая серия запросов закаш1ивается, выби 5 включения в работу подпрограмм обслуживания прерываний от внешних устройств. Функционирование этой части схемы, содержащей первый блок 1 nai-iH ти (задействованы первые и вторые

4Q выходы), группу элементов ШТК 2, группу триггеров 3 прерывакнй и элемент 2 И - ИЛИ 4. В первом блоке 1 памяти разряды D и D связаны с программой обслуживания прерывпиия

;jg от ВУ1. Это означает, что в блоке 1 памяти по тем адресам, по которым в основной памяти размещена программа обслз- живания прерывания от ВУ1 , записана некоторая информация в D и

50

DgS а по остальным адресам в D и D записаны О. По адресам програм а обслуживания прерывания от ВУ1 записана следующая информация: в D, - О для всех команд кроме последней, gg для последней .команды - в D - 1 для всех команд кроме последнеЙ5 для последней, команды - О. Анало- .гичным образом разряды D н D связаны с программой обслуживания прерывания от ВУ2„ Признаком правильности включения программы обслуживания прерывания является наличие перед этим соответствующего импульса прерывания на входах 20 прерываний.

Рассмотрим процесс правильного включения программы обсл:,гживания прерывания от ВУ1, Импульс на линии Прер, ВУ1 устанавливает в 1 первый триггер группы триггеров 3 прерываний. Сигнал Q с Ензерсного выхода этого триггера запрещает прохождение и шульсов с вьпсода D через элемент 2 И - ИЛИ 4, Тгюям образом, импульсы с выхода D, которые появляются во время работы программы обработки Прерывания от ВУ1, не проходят на выход элемента 2И-ИЛИ 4, потому что были замаскированы импульсом Прер, поступившим ранее. По окончании работы программы обработки импульс, который появляется на БД при выборке последней команды, через первый элемент ИЛИ 2 из группы устанавливает первый триггер 3 из группы 3 в О, т.е. сзсема возвращается в исходное состояние. Если происходит несанкционированное вклю- ,чение программы обработки прерывания от ВУ15 то импульсы с выхода D будут, беспрепятственно проходить на выход элемента 2И-ИЛИ 4, и далее через третий элемент ИЛИ 1-5 установят в 1 триггер 5 ошибки, что будет сигналом наличия сбоя.

Все элементы устройства являются стандартньми функциональными узлами, широко используемыми при построении цифровых устройств, и могут быть вьшолнены на базе серий К555 и К573.

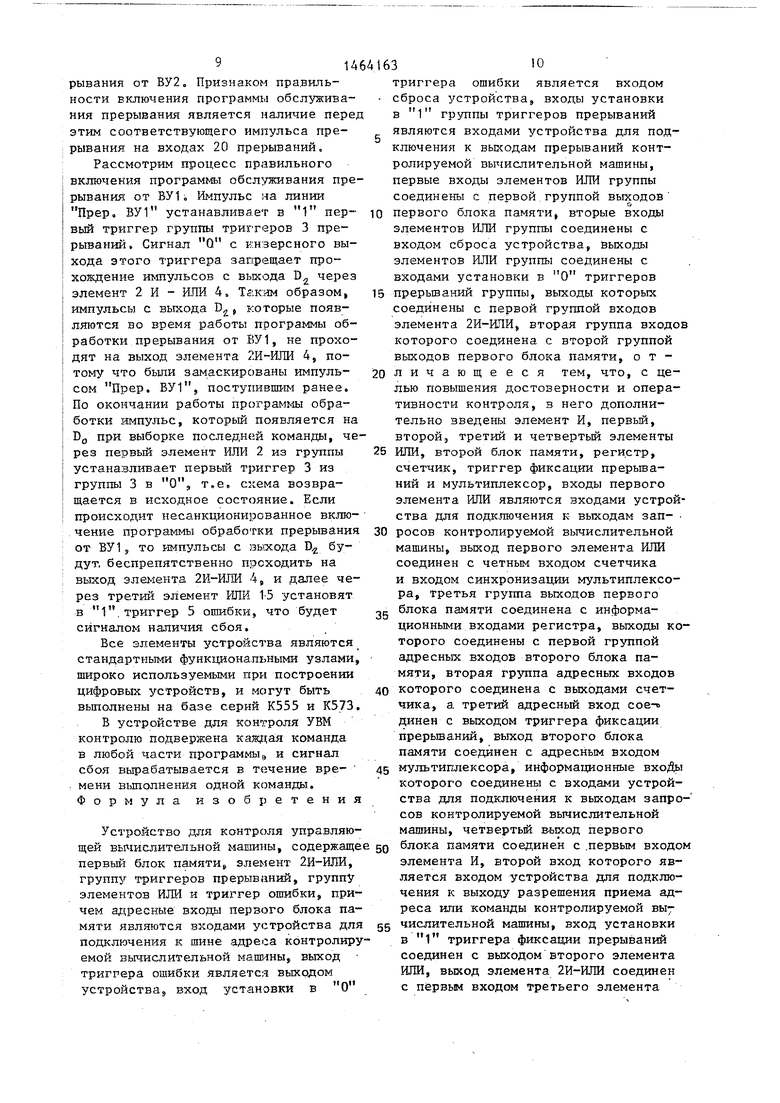

В устройстве для контроля УВМ контролю подвержена каждая команда в любой части программы,, и сигнал сбоя вырабатывается в течение вре- , мени В1 шолнения одной команды. Формула изобретения

Устройство для контроля управляютриггера ошибки является входом - сброса устройства, входы установки в 1 группы триггеров прерываний являются входами устройства для подключения к выходам прерываний контролируемой вычислительной машины, первые входы элементов ИЛИ группы соедине1ш с первой группой выходов 10 первого блока памяти, вторые входы элементов ИЛИ группы соединены с входом сброса устройства, выходы элементов ИЛИ группы соединены с входами установки в О триггеров 15 прерьшаний группы, выходы которых соединены с первой грутшой входов элемента 2И-ИЛИ, вторая группа входов которого соединена с второй группой выходов первого блока памяти, о т - 2оличающееся тем, что, с целью повышения достоверности и оперативности контроля, в него дополнительно введены элемент И, первьй, второй, третий и четвертьй элементы 25 ИЛИ, второй блок памяти, регистр, счетчик, триггер фикcaцIПi прерьшаний и мультиплексор, входы первого элемента ИЛИ являются входами устройства для подключения к выходам зап- 30 росов контролируемой вычислительной машины, выход первого элемента ИЛИ соединен с четным входом счетчика и входом синхронизации мультиплексора, третья группа выходов первого 2g блока памяти соединена с информационными входами регистра, выходы которого соединены с первой группой адресных входов второго блока памяти, вторая группа адресных входов 40 которого соединена с выходами счетчика, а третий адресный вход сое-в динен с выходом триггера фиксации прерьшаний, выход второго блока памяти соединен с адресным входом 45 мультиплексора, информационные вхоДь которого соединены с входами устройства для подключения к выходам запро- сов контролируемой вычислительной машины, четвертьй первого

щей вычислительной машины, содержащее gg блока памяти соединен с .первым входом первый блок памяти элемент 2И-ИЛИ, группу триггеров прерываний, группу элементов ИЖ и триггер ошибки, причем адресные входы первого блока памяти являются входами устройства для подключения к шине адреса контролиру™ емой вычислите,льной машины, выход триггера ошибки является выходом устройстваJ вход установки в О

элемента И, второй вход которого является входом устройства для подключения к выходу разрешения приема адреса или команды контролируемой вы 55 числительной машины, вход установки в 1 триггера фиксации прерываний соединен с выходом второго элемента ИЛИ, выход элемента 2И-ИЛИ соединен с первым входом третьего элемента

триггера ошибки является входом сброса устройства, входы установки в 1 группы триггеров прерываний являются входами устройства для подключения к выходам прерываний контролируемой вычислительной машины, первые входы элементов ИЛИ группы соедине1ш с первой группой выходов первого блока памяти, вторые входы элементов ИЛИ группы соединены с входом сброса устройства, выходы элементов ИЛИ группы соединены с входами установки в О триггеров прерьшаний группы, выходы которых соединены с первой грутшой входов элемента 2И-ИЛИ, вторая группа входов которого соединена с второй группой выходов первого блока памяти, о т - личающееся тем, что, с целью повышения достоверности и оперативности контроля, в него дополнительно введены элемент И, первьй, второй, третий и четвертьй элементы ИЛИ, второй блок памяти, регистр, счетчик, триггер фикcaцIПi прерьшаний и мультиплексор, входы первого элемента ИЛИ являются входами устройства для подключения к выходам зап- росов контролируемой вычислительной машины, выход первого элемента ИЛИ соединен с четным входом счетчика и входом синхронизации мультиплексора, третья группа выходов первого блока памяти соединена с информационными входами регистра, выходы которого соединены с первой группой адресных входов второго блока памяти, вторая группа адресных входов которого соединена с выходами счетчика, а третий адресный вход сое-в динен с выходом триггера фиксации прерьшаний, выход второго блока памяти соединен с адресным входом мультиплексора, информационные вхоДь которого соединены с входами устройства для подключения к выходам запро- сов контролируемой вычислительной машины, четвертьй первого

блока памяти соединен с .первым входом

элемента И, второй вход которого является входом устройства для подключения к выходу разрешения приема адреса или команды контролируемой вы числительной машины, вход установки в 1 триггера фиксации прерываний соединен с выходом второго элемента ИЛИ, выход элемента 2И-ИЛИ соединен с первым входом третьего элемента

ИЛИ, второй вход которого соединен с вьжодом мультиплексора, а выход соединен с входом установки в 1 триггера ошибки, выход элемента И соединен с первым входом четвертого элемента ИЛИ, с входом синхронизации регистра и входом установки в О триггера фиксации прерываний, выход

второго элемента ИЛТГ соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса счетчика, входы второго элемента ИЛИ соединены с входами устройства для подключения к выходам прерываний контролируемой вычислительной машины,

Таблица 1

Примечание,

XX - код значения не имеет, - устройство по коду XX.

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1159024, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-07—Публикация

1987-07-27—Подача