17

00

ел

(

fc

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1991 |

|

RU2011216C1 |

| Устройство для контроля управляющей вычислительной машины | 1990 |

|

SU1815645A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

Изобретение относится к вычислительной технике и может.быть использовано в вычислительных управляющих устройствах. Цель изобретения - уменьшение времени выполнения программы и расширение области применения за счет возможности работы с процессорами, с конвейером команд и опережающей выборкой команд. Поставленная цель достигается тем, что в устройство введены одновибратор 10, регистры 1 и 4, триггеры 6.8,21, элементы И 11 и ИЛ И 9, дополнительный связи. Контроль осуществляется путем суммирования кодов команД на линейном участке программы и сравнения при переходе на новый линейный участок реального и прогнозируемого адреса перехода. 2 ил. (Л С

flte/

Изобретение относится к вычислительной технике и может быть использовано при построении надежных управляющих вычислительных машин (УВМ), нечувствительных к сбоям программы.

Целью изобретения является уменьшение времени выполнения программы и расширение области применения за счет возможности работы с процессорами с конвейером команд и опережающей выборкой команд.

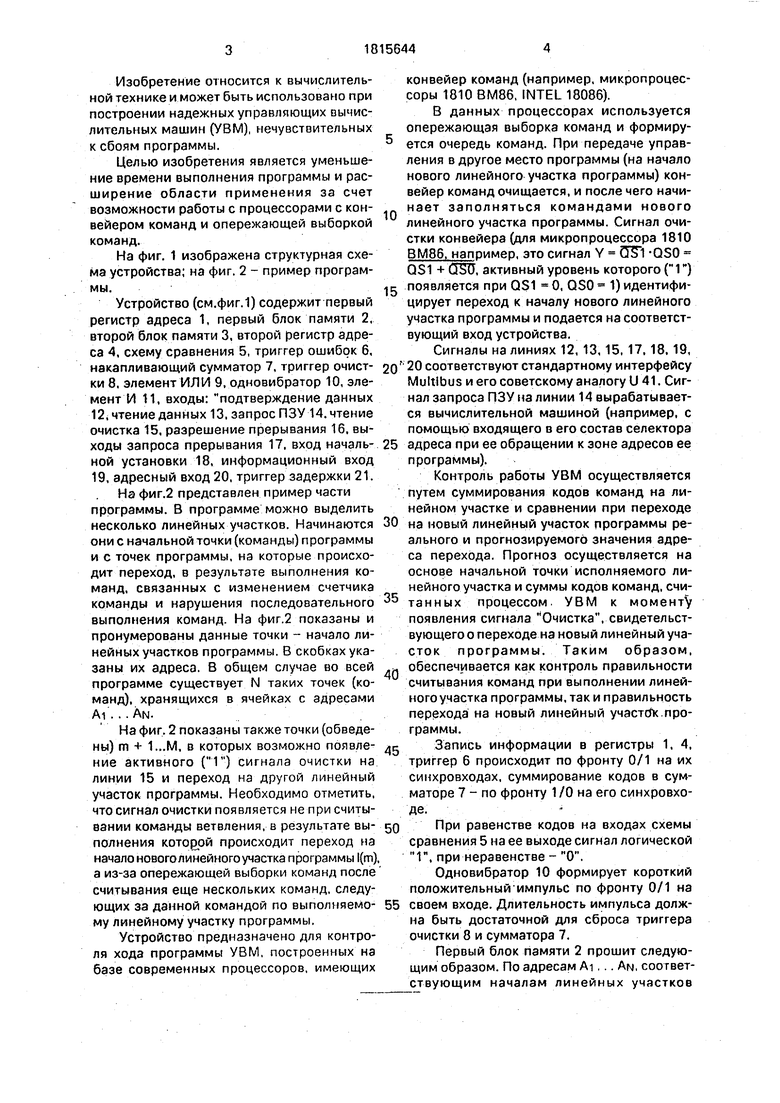

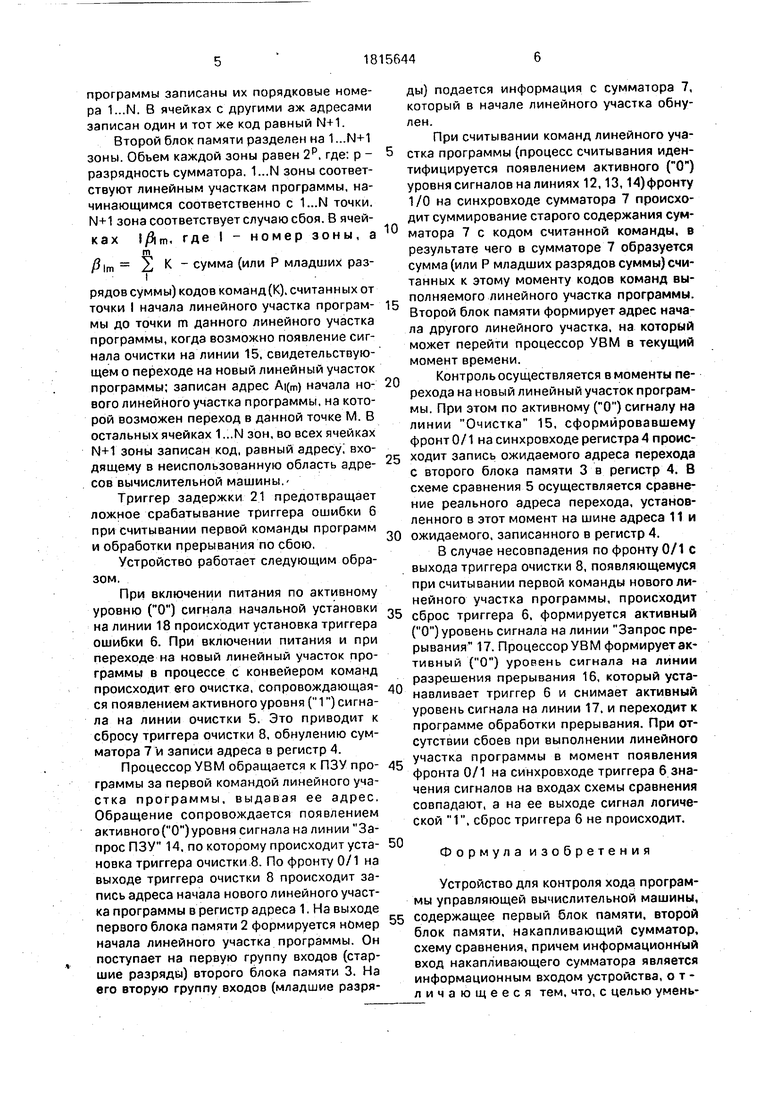

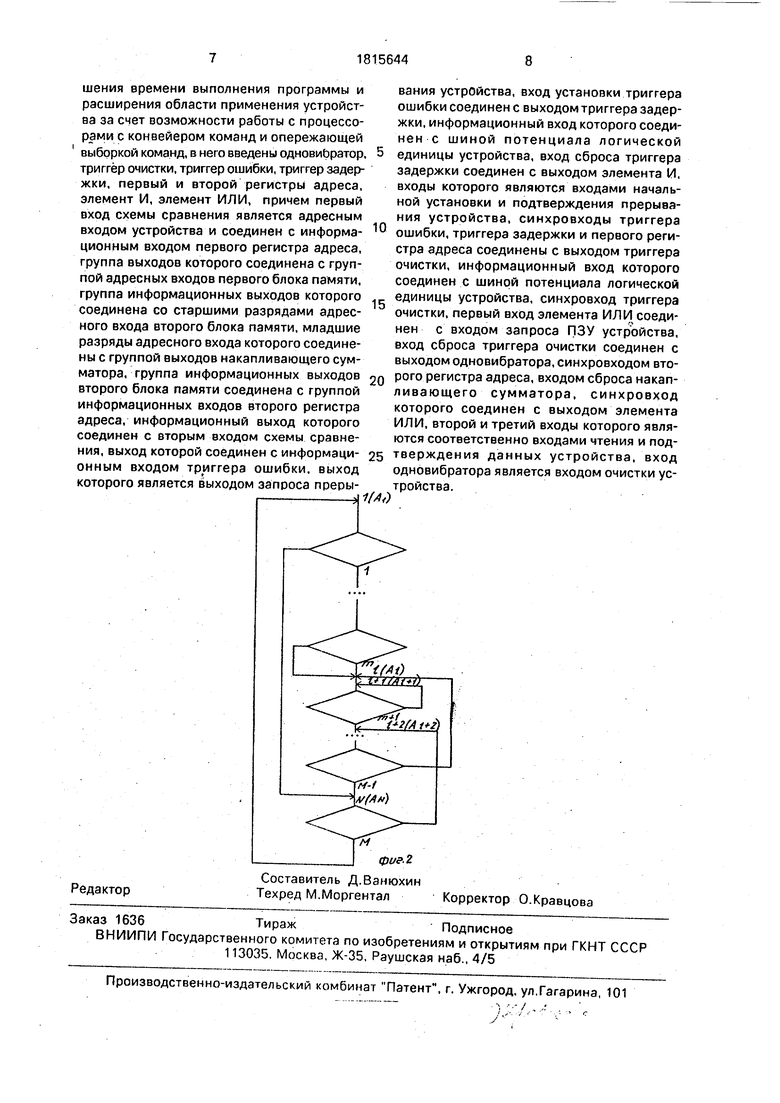

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - пример программы.

Устройство (см.фиг.1) содержит первый регистр адреса 1, первый блок памяти 2, второй блок памяти 3, второй регистр адреса 4, схему сравнения 5, триггер ошибок 6, накапливающий сумматор 7, триггер очистки 8, элемент ИЛИ 9, одновибратор 10, элемент И 11, входы: подтверждение данных 12, чтение данных 13. запрос ПЗУ 14. чтение очистка 15. разрешение прерывания 16. выходы запроса прерывания 17. вход начальной установки 18, информационный вход 19, адресный вход 20, триггер задержки 21.

На фиг.2 представлен пример части программы. В программе можно выделить несколько линейных участков. Начинаются они с начальной точки (команды) программы и с точек программы, на которые происходит переход, в результате выполнения команд, связанных с изменением счетчика команды и нарушения последовательного выполнения команд. На фиг.2 показаны и пронумерованы данные точки - начало линейных участков программы. В скобках указаны их адреса. В общем случае во всей программе существует N таких точек (команд), хранящихся в ячейках с адресами AI ... ANНа фиг. 2 показаны также точки (обведены) m + 1...М, в которых возможно появление активного (1) сигнала очистки на линии 15 и переход на другой линейный участок программы. Необходимо отметить, что сигнал очистки появляется не при считывании команды ветвления, в результате выполнения которой происходит переход на начало нового линейного участка программы l(m) а из-за опережающей выборки команд после считывания еще нескольких команд, следующих за данной командой по выполняемому линейному участку программы.

Устройство предназначено для контроля хода программы УВМ, построенных на базе современных процессоров, имеющих

,

Ю

конвейер команд (например, микропроцессоры 1810 ВМ86, INTEL 18086).

В данных процессорах используется опережающая выборка команд и формиру5 ется очередь команд. При передаче управления в другое место программы (на начало нового линейного участка программы) конвейер команд очищается, и после чего начинает заполняться командами нового линейного участка программы. Сигнал очистки конвейера (для микропроцессора 1810 ВМ86. например, это сигнал Y QS1-QSO QS1 + Q5TJ, активный уровень которого (1)

15 появляется при QS1 0, QSO идентифицирует переход к началу нового линейного участка программы и подается на соответствующий вход устройства.

Сигналы на линиях 12, 13,15, 17,18, 19,

20f 20 соответствуют стандартному интерфейсу Multibus и его советскому аналогу U 41. Сигнал запроса ПЗУ на линии 14 вырабатывается вычислительной машиной (например, с помощью входящего в его состав селектора

25 адреса при ее обращении к зоне адресов ее программы).

Контроль работы УВМ осуществляется путем суммирования кодов команд на линейном участке и сравнении при переходе

30 на новый линейный участок программы реального и прогнозируемого значения адреса перехода. Прогноз осуществляется на основе начальной точки исполняемого линейного участка и суммы кодов команд, счи35 тайных процессом. УВМ к моменту появления сигнала Очистка, свидетельствующего о переходе на новый линейный участок программы. Таким образом,

.. обеспечивается как контроль правильности считывания команд при выполнении линейного участка программы, так и правильность перехода на новый линейный участо1с.программы.

45 Запись информации в регистры 1. 4, триггер 6 происходит по фронту 0/1 на их синхровходах, суммирование кодов в сумматоре 7 - по фронту 1 /0 на его синхровхо- де.

50 При равенстве кодов на входах схемы сравнения 5 на ее выходе сигнал логической Г, при неравенстве - О.

Одновибратор 10 формирует короткий положительный импульс по фронту 0/1 на

55 своем входе. Длительность импульса должна быть достаточной для сброса триггера очистки 8 и сумматора 7.

Первый блок памяти 2 прошит следующим образом. По адресам AI ,.. AN, соответствующим началам линейных участков

программы записаны их порядковые номера 1...N. В ячейках с другими аж адресами записан один и тот же код равный N+1.

Второй блок памяти разделен на 1 ...N+1 зоны. Объем каждой зоны равен 2Р. где: р - разрядность сумматора. 1...N зоны соответствуют линейным участкам программы, начинающимся соответственно с 1...N точки. N+1 зона соответствует случаю сбоя. В ячейках 1/3|т, гДе номер зоны, а

2 К - сумма (или Р младших разрядов суммы) кодов команд (К), считанных от точки I начала линейного участка програм- мы до точки m данного линейного участка программы, когда возможно появление сигнала очистки на линии 15, свидетельствующем о переходе на новый линейный участок программы; записан адрес Ai(m) начала но- вого линейного участка программы, на которой возможен переход в данной точке М. В остальных ячейках 1 ...N зон, во всех ячейках N+1 зоны записан код, равный адресу; входящему в неиспользованную область адре- сов вычислительной машины,Триггер задержки 2.1 предотвращает ложное срабатывание триггера ошибки 6 при считывании первой команды программ и обработки прерывания по сбою,

Устройство работает следующим образом.

При включении питания по активному уровню (О) сигнала начальной установки на линии 18 происходит установка триггера ошибки 6. При включении питания и при переходе на новый линейный участок программы в процессе с конвейером команд происходит его очистка, сопровождающая- ся появлением активного уровня ( 1) сигнала на линии очистки 5. Это приводит к сбросу триггера очистки 8, обнулению сумматора 7 и записи адреса в регистр 4.

Процессор УВМ обращается к ПЗУ про- граммы за первой командой линейного участка программы, выдавая ее адрес. Обращение сопровождается появлением активного (О) уровня сигнала на линии Запрос ПЗУ 14. по которому происходит уста- новка триггера очистки 8. По фронту 0/1 на выходе триггера очистки 8 происходит запись адреса начала нового линейного участка программы в регистр адреса 1, На выходе первого блока памяти 2 формируется номер начала линейного участка программы. Он поступает на первую группу входов (старшие разряды) второго блока памяти 3. На его вторую группу входов (младшие разря

0

5 0 5

с 0

5 0 5

0

ды) подается информация с сумматора 7, который в начале линейного участка обнулен.

При считывании команд линейного участка программы (процесс считывания идентифицируется появлением активного (О) уровня сигналов на линиях 12,13,14)фронту 1/0 на синхровходе сумматора 7 происходит суммирование старого содержания сумматора 7 с кодом считанной команды, в результате чего в сумматоре 7 образуется сумма (или Р младших разрядов суммы) считанных к этому моменту кодов команд выполняемого линейного участка программы. Второй блок памяти формирует адрес начала другого линейного участка, на который может перейти процессор УВМ в текущий момент времени.

Контроль осуществляется в моменты перехода на новый линейный участок программы. При этом по активному (О) сигналу на линии Очистка 15, сформировавшему фронт 0/1 на синхровходе регистра 4 происходит запись ожидаемого адреса перехода с второго блока памяти 3 в регистр 4. В схеме сравнения 5 осуществляется сравнение реального адреса перехода, установленного в этот момент на шине адреса 11 и ожидаемого, записанного в регистр 4.

В случае несовпадения по фронту 0/1 с выхода триггера очистки 8, появляющемуся при считывании первой команды нового линейного участка программы, происходит сброс триггера 6, формируется активный (О) уровень сигнала на линии Запрос прерывания 17. Процессор УВМ формирует активный (О) уровень сигнала на линии разрешения прерывания 16, который устанавливает триггер 6 и снимает активный уровень сигнала на линии 17. и переходит к программе обработки прерывания. При отсутствии сбоев при выполнении линейного участка программы в момент появления фронта 0/1 на синхровходе триггера 6 значения сигналов на входах схемы сравнения совпадают, а на ее выходе сигнал логической 1, сброс триггера 6 не происходит.

Формула изобретения

Устройство для контроля хода программы управляющей вычислительной машины, содержащее первый блок памяти, второй блок памяти, накапливающий сумматор, схему сравнения, причем информационный вход накапливающего сумматора является информационным входом устройства, отличающееся тем. что, с целью уменьшения времени выполнения программы и расширения области применения устройства за счет возможности работы с процессорами с конвейером команд и опережающей выборкой команд, в него введены одновиЬратор. триггер очистки, триггер ошибки, триггер задержки, первый и второй регистры адреса, элемент И, элемент ИЛИ, причем первый вход схемы сравнения является адресным входом устройства и соединен с информационным входом первого регистра адреса, группа выходов которого соединена с группой адресных входов первого блока памяти, группа информационных выходов которого соединена со старшими разрядами адресного входа второго блока памяти, младшие разряды адресного входа которого соединены с группой выходов накапливающего сумматора, группа информационных выходов второго блока памяти соединена с группой информационных входов второго регистра адреса, информационный выход которого соединен с вторым входом схемы сравнения, выход которой соединен с информационным входом триггера ошибки, выход которого является выходом запроса прерывания устройства, вход установки триггера ошибки соединен с выходом триггера задержки, информационный вход которого соединен с шиной потенциала логической

единицы устройства, вход сброса триггера задержки соединен с выходом элемента И, входы которого являются входами начальной установки и подтверждения прерывания устройства, синхровходы триггера

ошибки, триггера задержки и первого регистра адреса соединены с выходом триггера очистки, информационный вход которого соединен с шиной потенциала логической единицы устройства, синхровход триггера очистки, первый вход элемента ИЛИ соединен с входом запроса ПЗУ устройства, вход сброса триггера очистки соединен с выходом одновибратора, синхровходом второго регистра адреса, входом сброса накапливающего сумматора, синхровход которого соединен с выходом элемента ИЛИ, второй и третий входы которого являются соответственно входами чтения и подтверждения данных устройства, вход

одновибратора является входом очистки устройства.

| Устройство для контроля хода программ | 1980 |

|

SU894713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-15—Публикация

1990-08-20—Подача