f6

О)

ел о ь ел

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1991 |

|

RU2011216C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Устройство для контроля хода программы | 1987 |

|

SU1451703A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

Изобретение относится к .вычислительной технике и может быть использовано в вычислительных управляющих устройствах. Цель изобретения - повышение достоверности контроля и расширение области применения за счет возможности контроля процессоров с конвейером команд. Поставленная цель достигается тем, что в устройство для контроля управляющей вычислительной машины дополнительно введены регистр адреса 2, первая 7 и вторая 8 схемы сравнения. Контроль производится путем сравнения реальной и ожидаемой временной диаграммы контролируемых управляющих сигналов. Обеспечивается контроль управляющих вычислительных машин, реализованных на процессорах с опережающей выборкой команд. 2 ил. Ј

Щиг.1

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах (УВМ).

Цель изобретения - повышение достоверности контроля и расширение области применения за счет возможности контроля процессоров с конвейером команд.

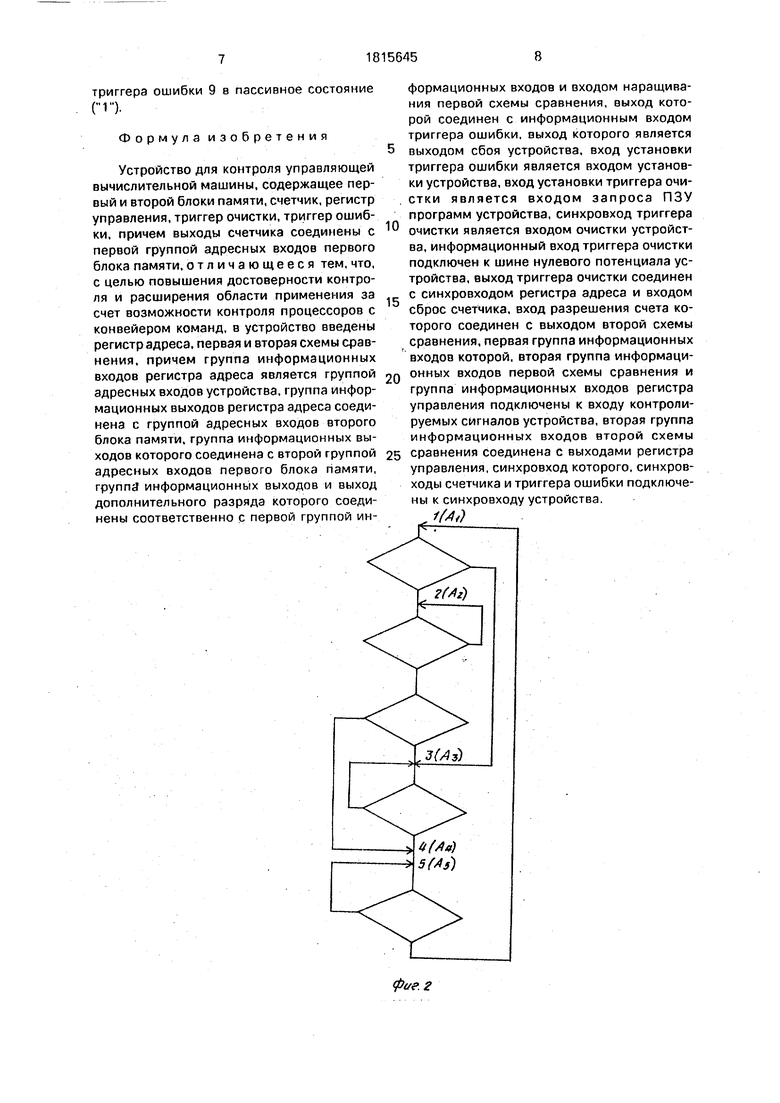

На фиг. 1 изображена структурная схема устройства.

Устройство содержит триггер очистки 1, регистр адреса 2, второй блок памяти 3, счетчик 4, первый блок памяти 5, регистр управления 6, первую 7, вторую 8 схемы сравнения, триггер ошибок 9, входы адресов 10, входы очистки 11, запроса ПЗУ программы 12, синхронизации 13, входы контролируемых сигналов 14, установки 15, выход сбоя устройства 16.

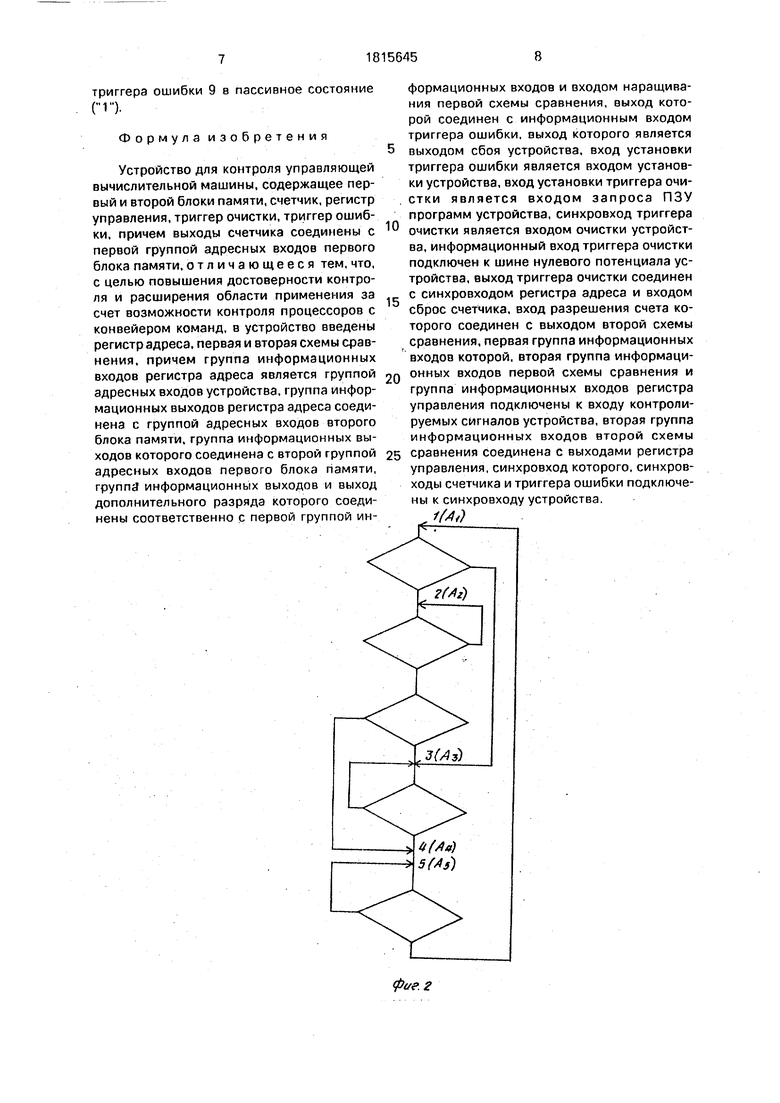

На фиг. 2 представлен пример части программы. В программе можно выделить несколько линейных участков. Наминаются они с начальной точки (команды) программы и с точек программы, на которые происходит переход, в результате выполнения команд, связанных с изменением счетчика команды и нарушения последовательного выполнения команд. На фиг. 2 показаны и пронумерованы данные точки - начало линейных участков программы. В скобках указаны их адреса. В общем случае по всей программе - № точек (команд), хранящихся в ячейках с адресами AI...AN.

Первый блок памяти 3 прошит следующим образом. По адресам AI....AN соответствующим началам линейных участков программы записаны их порядковые номера 1 ...N. В остальных - один и тот же код, не равный 1...N, например 1...1.

Область памяти второго блока 5 разделена на 1...N+1 зоны. Обьем каждой зоны равен 2м, где м - разрядность счетчика 4.1...N зонам соответствуют последовательности управляющих сигналов при выполне- нии линейных участков программы, начинающихся соответственно с 1 ...N точки, В ячейке U. где: L 1...N, К 0...2м-1 - значения сигналов соответственно на первой и второй группе входов второго блока памяти 5, записан код, соответствующий ожидаемому значению сигналов на проверяемых линиях 14 к моменту прихода к+1 фронта 0/1 синхроимпульсов на линии 13 (учитываются лишь те фронты 0/1 синхроимпульсов на линии 13. к приходу которых значения сигналов на контролируемых линиях 14 изменилось по отношению к предыдущему фронту 0/1. Подсчет

0

осуществляется относительно появления активного сигнала запроса ПЗУ программ). Ячейки второго блока памяти 5 имеет дополнительный по отношению к числу контролируемых линий 14 разряд. Он соединен с дополнительным входом первой схемы сравнения 7. В 1...N зонах в этом разряде записан О, в N-H зоне - 1. В других разрядах ячеек N+1 зоны может быть записана произвольная информация. N+1 зона (к ней происходит обращение, если на первой группе входов второго блока памяти 5 - код, отличный от 1...;1N) соответствует сбою при

с переходе на новый линейный участок программы, при котором переход происходит на адрес, отличающийся от начального адреса линейного участка программы (AL..AN). Для уменьшения объема второго блока

0 памяти 5 при большой длине линейных участков ( 2м циклов, связанных с изменением сигналов на проверяемых линиях 14) может использоваться их искусственное разбив . ние при помощи команд безусловного пере5 хода (их выполнение сопровождается очисткой конвейера команд), например, на следующую команду, записанную в следующей ячейке памяти программ.

Устройство предназначено для контро0 ля УВМ, построенных на базе современных процессоров, имеющих конвейер команд (например, микропроцессоры 1810В86, INTEL 18086).

В данных процессорах используется

5 опережающая выборка команд и формируется очередь команд. При передаче управления в другое место программы (на начало нового линейного участка программы) конвейер команды очищается, после чего начинается заполняться командами нового линейного участка программы. Сигнал очистки конвейера (для микропроцессора 1810 ВМ 86 это сигнал Y QS1-QSO QS1-QSO,

с активный уровень (1) которого появляется при QS1 О, QSO 1) идентифицирует переход к началу нового линейного участка программы и подается на соответствующий вход устройства.

0 Активный (О) уровень сигнала запроса ПЗУ программ вырабатывается процессором УВМ по фронту 0/1 синхроимпульса (например, с помощью входящего в его состав селектора адреса) при обращении к зо5 не адресов, по которым хранится программа УВМ.

Выходной сигнал сбоя устройства подается на вход перезапуска (RESET) процессора УВМ. В ответ на него им выдается

активный сигнал на линии установки 15 и осуществляется перезапуск.

Контроль работы УВМ осуществляется проверкой последовательности следования сигналов управления передачи адресов и данных (ввод, вывод и т.д.) на линиях 14, в том числе и сигналов выборки модулей УВМ (Запрос ПЗУ программ, запрос ОЗУ, Запрос устройства ввода-вывода). Используется детерминированность поведения УВМ на каждом линейном участке программы. При отсутствии сбоев на линиях управления передачей адресов и данных формируется строго определенная временная диаграмма, которую можно вычислить еще до начала прогона самой программы .

Таким образом обеспечивается контроль правильности обращения процессора проверяемой УВМ к остальным ее модулям (ПЗУ, ОЗУ. устройствам ввода-вывода и т.д.) в процессе выполнения линейных участков программы.

Запись информации в регистры 2, 6, триггеры 1, 3, наращивание счетчика 4 происходит по фронту 0/1 на их синхровходах. Наращивание счетчика 4 происходит только при наличии сигнала логического О на его входе разрешения счета.

При равенстве сигналов на первой и второй группе входов схем сравнения 7, 8 - на их выходе сигнал логической 1. при неравенстве О. При появлении активного (1) сигнала на дополнительном входе схемы сравнения 7 на ее выходе - сигнал логического О независимо от соотношения сигналов на первой и второй группе входов.

Регистр 6 и вторая схема сравнения 8 обеспечивают управление счетчиком 4. При совпадении сигналов на контролируемых линиях 14 к моменту фронта 0/1 синхроимпульса с их значениями, записанными в регистр 6 фронтом 0/1 предыдущего синхроимпульса с их значениями, записанными, на выходе второй схемы сравнения 8 - логическая 1. что препятствует наращиванию счетчика 8. Если значения сигналов изменились, за время такта, то к приходу фронта 0/1 синхроимпульса сигналы на входах второй группы сравнения не совпадают на ее выходе появляется логический О, что обеспечивает наращивание счетчика по фронту 0/1.

В регистр б по этому же фронту записывается новое значение сигналов на контролируемых линиях 14. Подобное управление счетчиком 4-уменьшает развертку временной диаграммы и тем самым объем второго блока памяти 5. Значения сигналов рас

сматриваются только во время фронтов 0/1 синхроимпульсов в блоке памяти 5 отсутствует повторение тактов с неизменным значением сигналов на контролируемых линиях 14.

Устройство работает следующим обра- зом.

При включении питания процессор УВМ формирует активный уровень сигнала установки 15. который сбрасывает триггер ошибки 9. При включении питания и при переходе на новый линейный участок программы происходит очистка конвейера команд процессора УВМ, сопровождающаяся появлением активного (1) уровня сигнала на линии очистки 11, приводящим к сбросу триггера очистки 1 и счетчика 4.

Процессор УВМ обращается за первой

командой нового линейного участка программы, выдавая ее адрес. Обращение сопровождается появлением ее активного (О) уровня сигнала на линии запроса ПЗУ программ 12, по которому происходит установка триггера очистки 1. По появляющемуся на выходе триггера очистки 1 фронту 0/1 происходит нового линейного участка программы в регистр адреса 2. На выходе первого блока памяти 3 формируется номер

начала нового линейного участка программы. Он поступает на первую группу входов второго блока памяти 5, на его вторую группу входов подается информация со счетчика 4.

По мере поступления синхроимпульсов на линии 13 происходит наращивание счетчика 4, на выходе второго блока памяти 5 формируется ожидаемая временная диаграмма контролируемых сигналов на линиях

При отсутствии сбоев к фронту 0/1 очередного синхроимпульса сигналы на обоих группах схемы сравнения 7 совпадают, на ее выходе - 1, триггер ошибки остается в установленном состоянии, активный уровень (О) сигнала сбоя на линии 16 не выдается.

При сбое из-за несоответствия между сигналами на входе первой схемы сравнения к приходу фронта 0/1 синхросигнала на

линии 13 на выходе схемы сравнения 7 - О, происходит сброс триггера ошибки 9, выдается активный уровень (О) сигнала сбоя на линии 16. По нему осуществляется перезапуск УВМ и по сигналу установки установка

триггера ошибки 9 в пассивное состояние (1).

Формула изобретения

Устройство для контроля управляющей вычислительной машины, содержащее первый и второй блоки памяти, счетчик, регистр управления, триггер очистки, триггер ошибки, причем выходы счетчика соединены с первой группой адресных входов первого блока памяти, отличающееся тем, что, с целью повышения достоверности контроля и расширения области применения за счет возможности контроля процессоров с конвейером команд, в устройство введены регистр адреса, первая и вторая схемы сравнения, причем группа информационных входов регистра адреса является группой адресных входов устройства, группа информационных выходов регистра адреса соединена с группой адресных входов второго блока памяти, группа информационных выходов которого соединена с второй группой адресных входов первого блока памяти, группа информационных выходов и выход дополнительного разряда которого соединены соответственно с первой группой ин0

5

0

5

формационных входов и входом наращивания первой схемы сравнения, выход которой соединен с информационным входом триггера ошибки, выход которого является выходом сбоя устройства, вход установки триггера ошибки является входом установки устройства, вход установки триггера очистки является входом запроса ПЗУ программ устройства, синхровход триггера очистки является входом очистки устройства, информационный вход триггера очистки подключен к шине нулевого потенциала устройства, выход триггера очистки соединен с синхровходом регистра адреса и входом сброс счетчика, вход разрешения счета которого соединен с выходом второй схемы сравнения, первая группа информационных входов которой, вторая группа информационных входов первой схемы сравнения и группа информационных входов регистра управления подключены к входу контролируемых сигналов устройства, вторая группа информационных входов второй схемы сравнения соединена с выходами регистра управления, синхровход которого, синхров- ходы счетчика и триггера ошибки подключены к синхровходу устройства.

М

| Авторское свидетельство СССР №1159024,6 06 F 11/30 | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1993-05-15—Публикация

1990-08-20—Подача