Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1334146A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения унифицированных устройств сопряжения ЭВМ, например, с внешними запоминающими устройствами. Целью изобретения является повышение быстродействия и достоверности передаваемой информации. Устройство содержит операционный блок, блок памяти микроопераций, блок памяти микрокоманд, блок памяти данных, блок памяти констант, группу мультиплексоров, регистр адреса микроопераций, регистр микроопераций, два регистра адреса микрокоманд, регистр микрокоманд, регистр приема, регистр выдачи, регистр слова состояния, счетчик, два дешифратора синхроимпульсов, генератор тактовых импульсов, группу шинных формирователей 2 ил

Изобретение относится к вычислительной технике и может быть использовано для построения унифицированных устройств сопряжения ЭВМ, например, с внешними запоминающими устройствами.

Целью изобретения является повышение быстродействия и достоверности передаваемой информации.

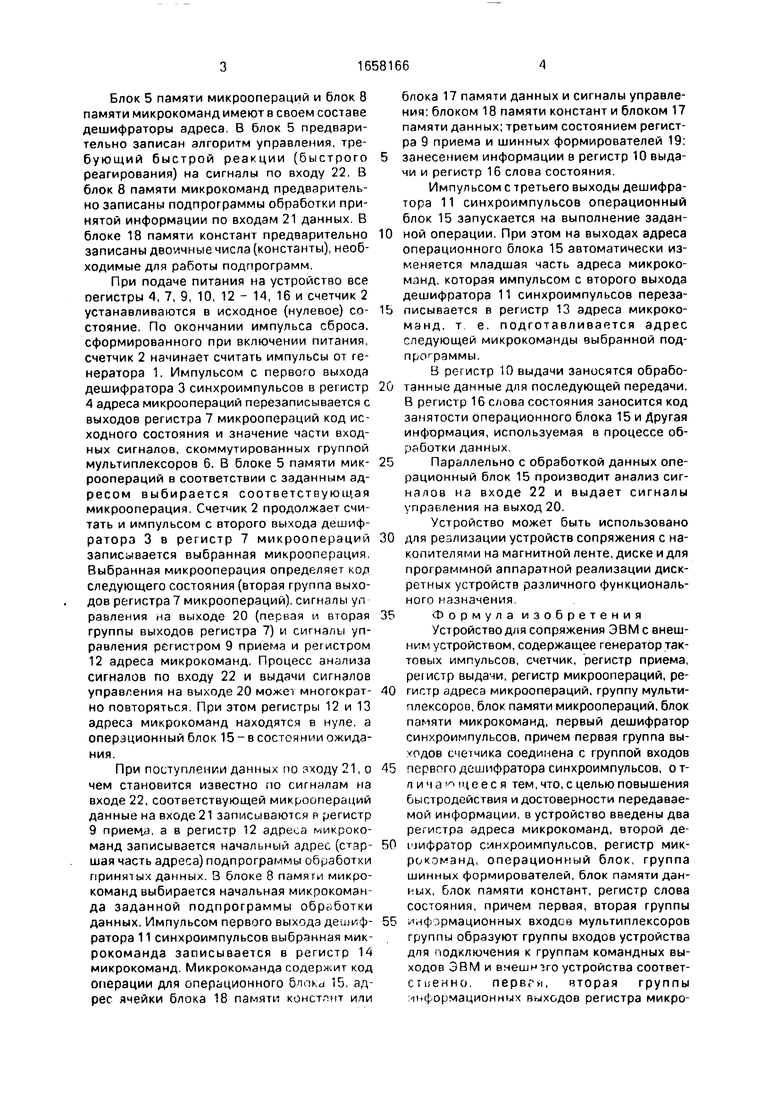

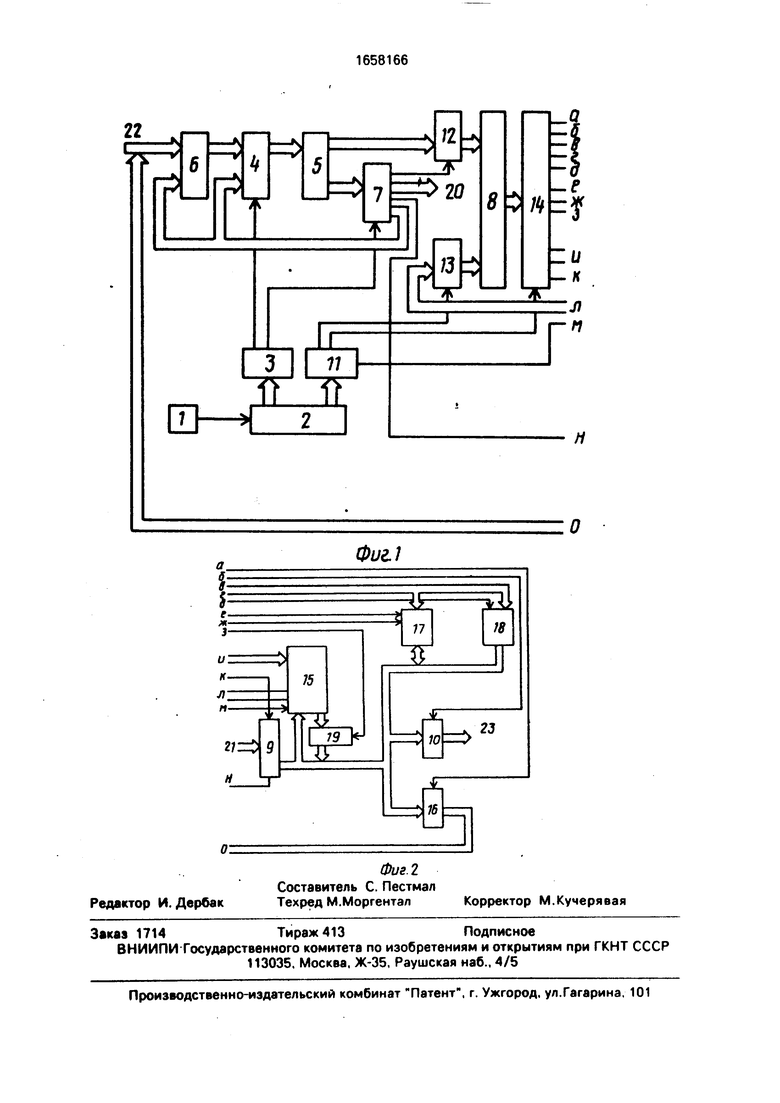

На фиг. 1 и 2 приведены схемы устройства.

Устройство содержит (фиг. 1 и 2) генератор 1 тактовых импульсов, счетчик 2, дешифратор 3 синхроимпульсов, регистр 4 адреса микроопераций, блок 5 памяти микроопераций, группу мультиплексоров б, регистр 7 микроопераций, блок 8 памяти микрокоманд, регистр 9 приема, регистр 10 выдачи, дешифратор 11 синхроимпульсов, регистры 12 и 13 адреса микрокоманд, регистр 14 микрокоманд, операционный блок t5, регистр 16 слова состояния, блок 17 памяти данных, блок 18 памяти констант, группу шинных формирователей 19, входы и выходы 20 - 23.

В качестве операционного блока 15 используется серийный микропроцессор типа 582ИК1.

Микропроцессор в устройстве выполняет в зависимости от реализуемого алгоритма работы следующие функции: прием данных с магистрали (регистр 9, блок 17 и блок 18); выдача данных на магистраль (регистры 10, 16 и блок 17); наращивание адреса микрокоманды; выдача младшей части адреса блока 8 памяти микрокоманд; сложение чисел; сравнение чисел; засылка чисел в регистры микропроцессора, сдвиг числа вправо (влево).

Устройство работает следующим образом.

Os

сл

00

Оч

Блок 5 памяти микроопераций и блок 8 памяти микрокоманд имеют в своем составе дешифраторы адреса. В блок 5 предварительно записан алгоритм управления, требующий быстрой реакции (быстрого реагирования) на сигналы по входу 22. В блок 8 памяти микрокоманд предварительно записаны подпрограммы обработки принятой информации по входам 21 данных. В блоке 18 памяти констант предварительно записаны двоичные числа (константы), необходимые для работы подпрограмм.

При подаче питания на устройство все пегистры 4, 7, 9, 10, 12 - 14, 16 и счетчик 2 устанавливаются в исходное (нулевое) состояние. По окончании импульса сброса, сформированного при включении питания, счетчик 2 начинает считать импульсы от генератора 1. Импульсом с первого выхода дешифратора 3 синхроимпульсов в регистр 4 адреса микроопераций перезаписывается с выходов регистра 7 микроопераций код исходного состояния и значение части входных сигналов, скоммутированных группой мультиплексоров 6. В блоке 5 памяти микроопераций в соответствии с заданным адресом выбирается соответствующая микрооперация. Счетчик 2 продолжает считать и импульсом с второго выхода дешифратора 3 в регистр 7 микроопераций записывается выбранная микрооперация. Выбранная микрооперация определяет кол следующего состояния (вторая группа выходов регистра 7 микроопераций), сигналы ул равления на выходе 20 (первая и вторая группы выходов регистра 7) и сигналы управления регистром 9 приема и регистром 12 адреса микрокоманд. Процесс анализа сигналов по входу 22 и выдачи сигналов управления на выходе 20 может многократно повторяться. При этом регистры 12 и 13 адреса микрокоманд находятся в нуле, а операционный блок 15-всостоянии ожидания.

При поступлении данных по эходу 21, о чем становится известно по сигналам на входе 22, соответствующей микроопераций данные на входе 21 записываются в регистр 9 приему, а в регистр 12 адреса микрокоманд записывается начальный адрес (старшая часть адреса) подпрограммы обработки принятых данных. В блоке 8 памяти микрокоманд выбирается начальная микрокоманда заданной подпрограммы обработки данных, Импульсом первого выхода дешифратора 11 синхроимпульсов выбранная микрокоманда записывается в регистр 14 микрокоманд. Микрокоманда содержит код операции для операционного 15, адрес ячейки блока 18 памяти констлнт или

блока 17 памяти данных и сигналы управления: блоком 18 памяти констант и блоком 17 памяти данных; третьим состоянием регистра 9 приема и шинных формирователей 19:

занесением информации в регистр 10 выдачи и регистр 16 слова состояния.

Импульсом с третьего выходы дешифратора 11 синхроимпульсов операционный блок 15 запускается на выполнение задан0 ной операции. При этом на выходах адреса операционного блока 15 автоматически изменяется младшая часть адреса микрокоманд, которая импульсом с второго выхода дешифратора 11 синхроимпульсов перезаЬ писывается в регистр 13 адреса микрокоманд, т, е. подготавливается адрес следующей микрокоманды выбранной под- профаммы.

В регистр 10 выдачи заносятся обрабо0 тайные данные для последующей передачи. В регистр 16 слова состояния заносится код занятости операционного блока 15 и Другая информация, используемая в процессе обработки данных.

5Параллельно с обработкой данных операционный блок 15 производит анализ сигналов на входе 22 и выдает сигналы управления на выход 20.

Устройство может быть использовано

0 для резлизации устройств сопряжения с накопителями на магнитной ленте, диске и для программной аппаратной реализации дискретных устройств различного функционального назначения.

5Формула изобретения

Устройство для сопряжения ЭВМ с внешним устройством, содержащее генератор тактовых импульсов, счетчик, регистр приема, регистр выдачи, регистр микроопераций, ре0 гистр адреса микроопераций, группу мультиплексоров, блок памяти микроопераций, блок памяти микрокоманд, первый дешифратор синхроимпульсов, причем первая группа выходов счетчика соединена с группой входов

5 первого дешифратора синхроимпульсов, от- л и ч а щ е е с я тем, что, с целью повышения быстродействия и достоверности передаваемой информации, в устройство введены два регистра адреса микрокоманд, второй де0 шифратор синхроимпульсов, регистр микрокоманд, операционный блок, группа шинных формирователей, блок памяти данных, блок памяти констант, регистр слова состояния, причем первая, вторая группы

5 информационных входов мультиплексоров группы образуют группы входов устройства для подключения к группам командных выходов ЭВМ и внешнего устройства соответ- стиенно. первги, вторая группы информационных выходов регистра микроопераций образуют группы выходов устройства для подключения к группам командных входов ЭВМ и внешнего устройства соответственно, первая, вторая группы информационных входов регистра приема образуют группы входов устройства для подключения к группам информационных выходов ЭВМ и внешнего устройства соответственно, первая, вторая группы информационных выходов регистра выдачи образуют группы выходов устройства для подключения к группам информационных входов ЭВМ и внешнего устройства соответственно, при этом группа информационных выходов регистра слова состояния соединена с третьей группой информационных входов мультиплексоров группы, группа информационных выходов которых соединена с первой группой информационных входов регистра адреса микроопераций, группа выходов которого соединена с группой адресных входов блока памяти микроопераций, первая группа информационных выходов которого соединена с группой информационных входов регистра микроопераций,третья группа информационных выходов которого соединена с группой управляющих входов мультиплексоров группы и с второй группой информационных входов регистра адреса микроопераций, синхровход которого соединен с первым выходом первого дешифратора синхроимпульсов, второй выход которого соединен с синхровходов регистра микроопераций, первый информационный выход которого соединен с синхровходом первого регистра адреса микрокоманд, группа информационных входов и группа информационных выходов которого соединены соответственно с второй группой информационных выходов блока памяти микроопераций и с группой старших разрядов адресных входов блока памяти микрокоманд, группа младших разрядов адресных входов и группа информационных выходов которого соединены соответственное группой информационных

выходов второго регистра адреса микрокоманд и с группой информационных входов регистра микрокоманд, синхровход которого соединен с первым выходом второго дешифратора синхроимпульсов, второй выход которого соединен с синхровходом второго регистра адреса микрокоманд, группа информационных входов которого соединена с группой адресных выходов операционного блока, группа входов кода операции которого соединена с первой группой информационных выходов регистра микрокоманд, первый, второй, третий, четвертый, пятый, шестой и седьмой информационные

выходы которого соединены соответственно с первым синхровходом регистра приема, с синхровходом и с входом записи-чтения блока памяти данных, с синхровходом блока памяти констант, с синхровходами регистра

выдачи и регистра слова состояния, с управляющими входами шинных формирователей группы, информационные входы которых соединены с группой информационных выходов операционного блока, группа

информационных входов которого соединена с группой информационных выходов регистра приема, с информационными выходами шинных формирователей группы, с группами информационных входов регистра выдачи и регистра слова состояния, с группой информационных входов-выходов блока памяти данных, с группой информационных выходов блока памяти констант, группа адресных входов которого соединена с группой адресных входов блока памяти данных и с второй группой информационных выходов регистра микрокоманд, синхровыход генератора тактовых импульсов соединен со счетным входом счетчика, вторая группа выходов которого соединена с группой входов второго дешифратора синхроимпульсов, третий выход которого соединен с тактовым вход операционного блока, второй синхровход регистра приема соединен с вторым

информационным выходом регистра микроопераций.

гг.

/2

Фиг.1

;0bi

23

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1989-02-06—Подача