Изобретение относится к вычислительной технике и может быть использовано при создании персональных компьютеров для обеспечения обмена данными между внутренними шинами процессоров и системной шиной ЭВМ.

Известно устройство для обмена данными, входящее в состав персональной ЭВМ, содержащее арифметико-логическое устройство (АЛУ), регистр микрокоманд, микропрограммную память, блок регистров, мультиплексор (патент США № 4680701, кл. G Об F 13/00, 1987).

Известно также устройство обмена данными, содержащее оперативную память, память микропрограмм, регистр команд, дешифратор команд, регистр адреса, регистр состояния, устройство управления вводом- выводом (патент США № 4777590, кл. G 06 F 15/02, 1986).

Недостатком известных аналогов является невысокое быстродействие.

Наиболее близким к изобретению по технической сущности является устройство, содержащее память микропрограмм, регистр микрокоманд, регистр адреса, регистр команд, блок приемопередатчиков, мультиплексор и триггер условий, блок регистров, счетчик команд, тактовый генератор, формирователь запроса и блок управления выборкой кода, причем выход регистра адреса соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выход поля следующего адреса которого соединен с первым информационным входом регистра адреса, первый вход-выход блока приемопередатчиков является информационным входом-выходом устройства, второй вход- выход блока приемопередатчиков соединен с первой информационной шиной и информационным входом регистра команд, выход поля управления регистра микрокоманд соединен с информационным входом блока приемопередатчиков и управляющим входом регистра адреса, выход и группа выходов счетчика команд, управляющий вход счетчика команд соединены с выходом управления регистра микрокоманд, первая группа выходов которого соединена с группой информационных входов третьего регистра, выходы которого соединены с управляющими входами блока приемопередатчиков и с первым входом первого элемента И-НЕ; второй вход которого соединен с выходом соответствующего разряда регистра микрокоманд, группа выходов которого соединена с первой группой адресных входов постоянного запоминающего устройства и первым входом второго элемента И-НЕ, второй вход которого соединен через первый элемент НЕ с первым выходом второго регистра, соединенногопервым и вторым входами с управляющим и первым информационным входами блока приемопередатчиков, второй информационный вход и группа входов которого соединены соответственно с прямым выходом

триггера и выходом поля константы регистра микрокоманд, вторая группа адресных входов постоянного запоминающего устройства соединена с группой выходов первого регистра, первый, второй, третий и

5 четвертый выходы второго регистра соединены соответственно с управляющими входами регистра команд, счетчика команд, формирователя запроса и блока регистра, соединенного с входом второго элемента

0 И-НЕ, и являются входом блокировки процессора, выход второго элемента НЕ соединен с синхровходами триггера условий, регистра адреса и формирователя запроса, информационный вход которого соединен с

5 выходом счетчика команд (авт. св. № 1769612, кл. G 06 F 13/00, 1990).

Однако известное устройство не обеспечивает достаточно высокое быстродействие.

0Целью изобретения является повышение быстродействия.

Цель достигается тем, что в устройство, содержащее память микропрограмм, регистр микрокоманд, регистр адреса, регистр

5 команд, блок приемопередатчиков, мультиплексор, триггер условий, блок регистров, счетчик команд, тактовый генератор, формирователь запроса и блок управления выборкой кода, причем выход регистра адреса

0 соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выход поля следующего адреса ко- торого соединен с первым

5 информационным входом регистра адреса, первый вход-выход блока приемопередатчиков является информационным входом- выходом устройства, второй вход-выход блока приемопередатчиков соединен с пер0 вой информационной шиной и информационными входами регистра команд и счетчика команд, выход поля управления регистра микрокоманд соединен с информационным входом блока приемопередат5 чиков и управляющим входом регистра адреса, выход счетчика команд соединен с информационными входами регистра команд и формирователя запроса, выход которого соединен с входом запроса прерывания блока управления выборкой кода, с первого по четвертый выходы и первая группа выходов которого соединены соответственно с синхровходами регистра команд, счетчика команд, формирователя запроса и блока регистров и с группой управляющих входов блока приемопередатчиков, выход тактового генератора соединен с синхровходом блока управления выборкой кода, первая группа входов которого соединена с группой выходов блока приемопередатчиков, а группа адресных входов - с группой адресных выходов регистра микрокоманд, группа информационных выходов блока регистров через вторую информационную шину соединены с первой группой выходов блока приемопередатчиков, пятый выход блока управления выборкой кода является выходом блокировки АЛУ устройства, а вторая группа выходов соединена с второй группой информационных входов блока приемопередатчиков, группа выходов счетчика команд соединена через третью информационную шину с третьей группой информационных входов блока приемопередатчиков, группа выходов мультиплексора условий соединена с третьей группой информационных входов регистра адреса и входом триггера условий, синхровход которого соединен с шестым выходом блока управления выборкой кода, а выход - с информационным входом мультиплексора условий, группа входов которого является группой входов устройства для подключения к выходам логических условий процессора и выходу переполнения блока регистров, группа выходов регистра команд через вторую информационную шину соединена с первой группой информационных входов блока приемопередатчиков, в веде- ны блок формирования начальных адресов, блок загрузки, регистр, блок дешифрации прерываний, при этом группа входов запросов блока дешифрации прерываний является группой входов устройства для подключения к выходам запросов внешних устройств, а группа выходов и первый выход соединены с второй группой информационных входов регистра адреса и адресным входом блока формирования начальных адресов, группа адресных входов и группа выходов которого соединены соответственно с группой выходов регистра команд и второй группой информационных входов регистра адреса, первый и второй выходы блока формирования начальных адресов соединены с управляющими входами счетчика команд и блока регистров, а управляющий вход - с выходом триггера условий, группа адресных входов блока загрузки и вход маски блока дешифрации прерываний соединены соответственно с группой выходов и выходом регистра, группа информационных входов, синхровход и управляющий вход которого соединены соответственно с третьей

информационной шиной устройства, третьим выходом блока управления выборкой кода и третьим выходом регистра микрокоманд, группа выходов блока загрузки соединена с первой информационной

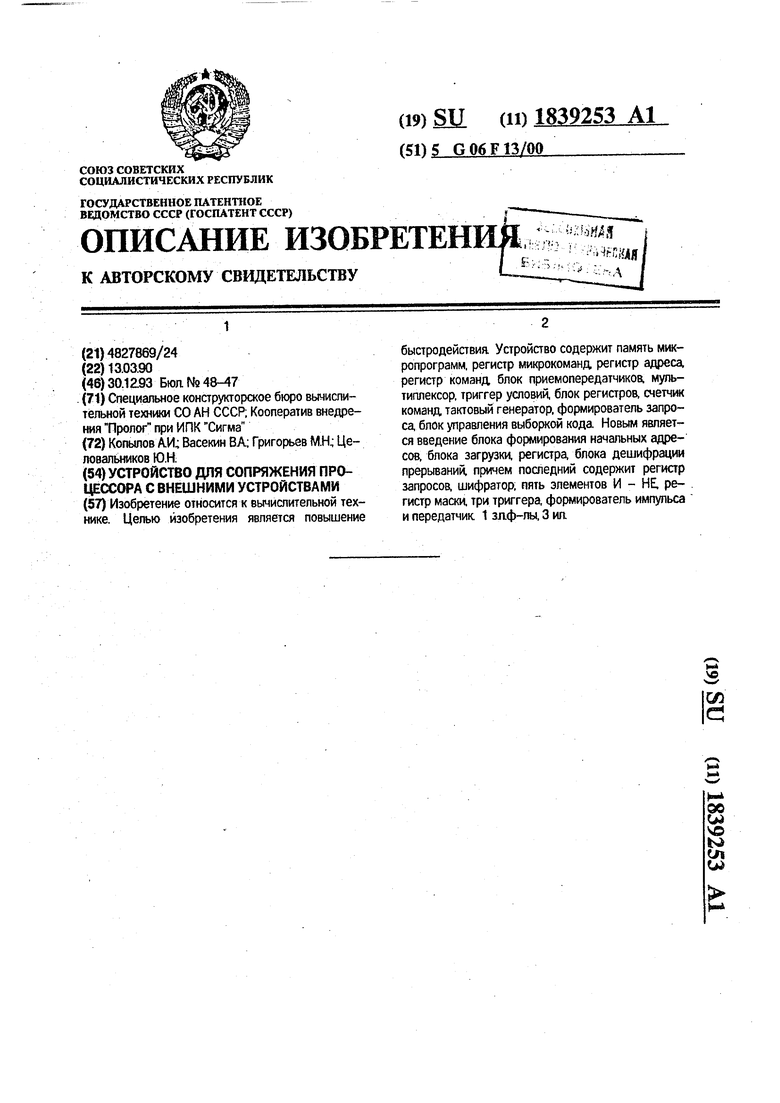

0 шиной, синхровход, управляющий вход и первый, второй, третий выходы блока дешифрации прерываний соединены соответственно с седьмым -выходом блока управления выборкой кода и четвертым вы5 ходом регистра микрокоманд, входом логических условий блока управления выборкой кода, входом сброса регистра микрокоманд и выходом ответа устройства. Блок дешифрации прерываний содержит регистр запро0 сов, шифратор, пять элементов И-НЕ, регистр маски, три триггера, формирователь импульса, передатчик, причем группа входом передатчика и группа информационных входов регистра запросов образуют

5 группу входов запросов блока, группа выходов регистра запросов соединена с первой группой входов шифратора и группой входов первого элемента И-НЕ, группа выходов шифратора является группой выходов

0 блока, выход первого элемента И-Н Е соединен с первым входом второго элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом данных

5 регистра маски, выход которого является первым выходом блока, а группа выходов соединена с второй группой входов шифратора, вход запуска формирователя импульса, первый вход четвертого элемента И-НЕ,

0 входы сброса первого, второго триггеров, вход установки третьего триггера и с второго по четвертый входы второго элемента И- НЕ образуют вход маски блока, выход формирователя импульса соединен с вто5 рым входом третьего элемента И-НЕ и вторым входом данных регистра маски, второй вход четвертого элемента И-НЕ соединен с единичным выходом первого триггера, а выход - с третьим входом третьего элемента

0 И-НЕ и третьим входом данных регистра маски, нулевой выход второго триггера соединен с четвертым входом третьего элемента И-НЕ и четвертым информационным входом регистра маски, единичный выход

5 третьего триггера соединен с его входом сброса, нулевой выход-с первым выходом блока, синхровходы регистра запросов, шифратора, управляющий вход регистра маски образуют управляющий вход блока, синхровходы третьего триггера, регистр маски и первый вход блока приемопередатчиков образуют синхровход блока, входы пятого элемента И-НЕ соединены с группой входов запросов блока, а выход соединен с входом блока приемопередатчиков, пер- вый, второй и третий выходы которого соединены соответственно с синхровходами первого, второго триггеров и входом данных третьего триггера, четвертый, пятый и шестой выходы блока приемопередатчиков об- разуют первый выход блока, а седьмой и восьмой выходы - второй и третий выходы блока.

При анализе технических решений, известных в вычислительной технике, не обна- ружено решений с признаками, сходными с отличительными признаками заявляемого решения, что дает основание считать предлагаемое техническое решение соответствующим критериям существенные отличия и новизна. Этот вывод подтверждается тем, что создается недостижимый ранее положительный эффект, заключающийся в повышении быстродействия и обус- ловленный новыми признаками по сравнению с использованием известных технических решений.

Благодаря введению блока формирования начальных адресов, блока загрузки, регистра, блока шифрации прерываний с соответствующими связями и выполнению блока дешифрации прерываний содержащим регистр запросов, шифратор, пять элементов И-НЕ, регистр маски, три триггера, формирователь импульса, передатчик заяв- ляемое техническое решение приобретает новые свойства, получение которых не обеспечивают прототип и другие технические решения, а именно создается возможность повысить быстродействие устройства и со- ответственно персональной ЭВМ, в которую оно входит.

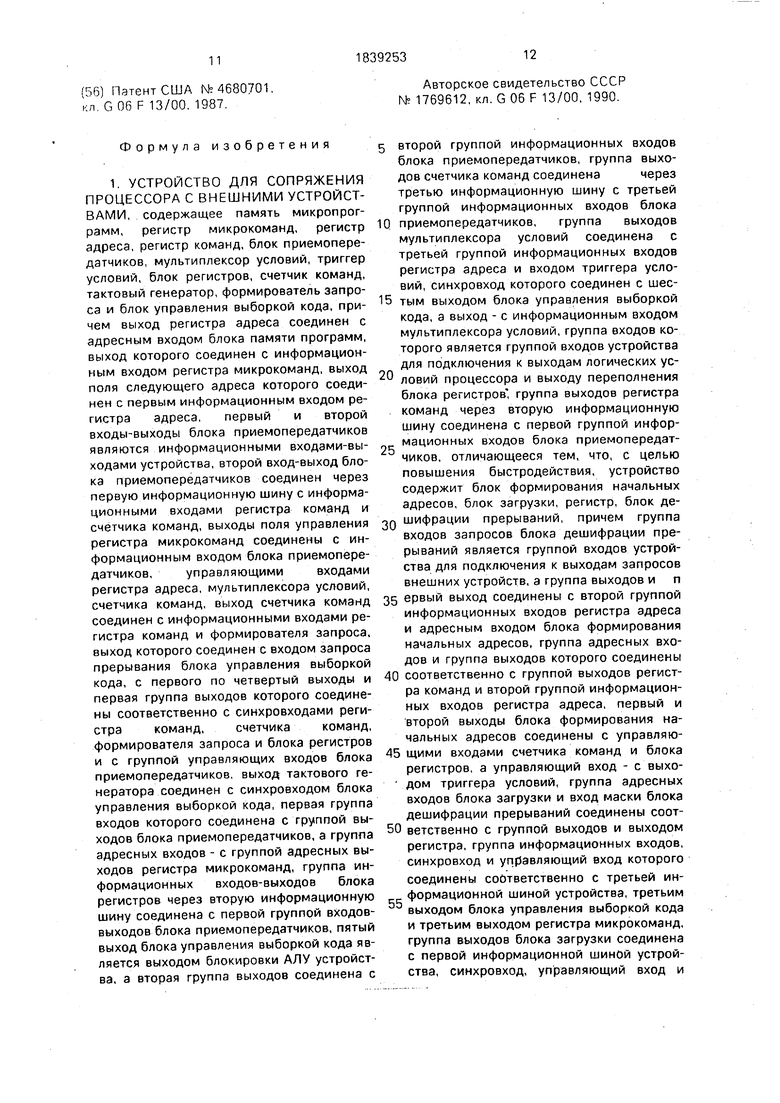

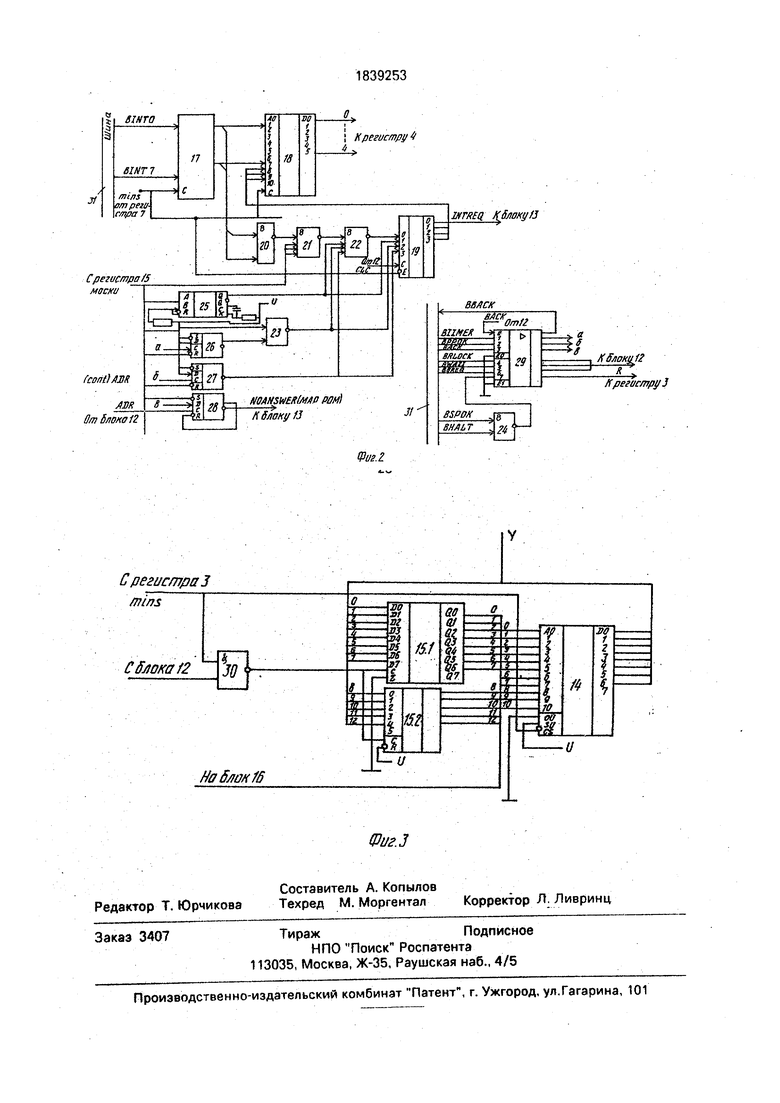

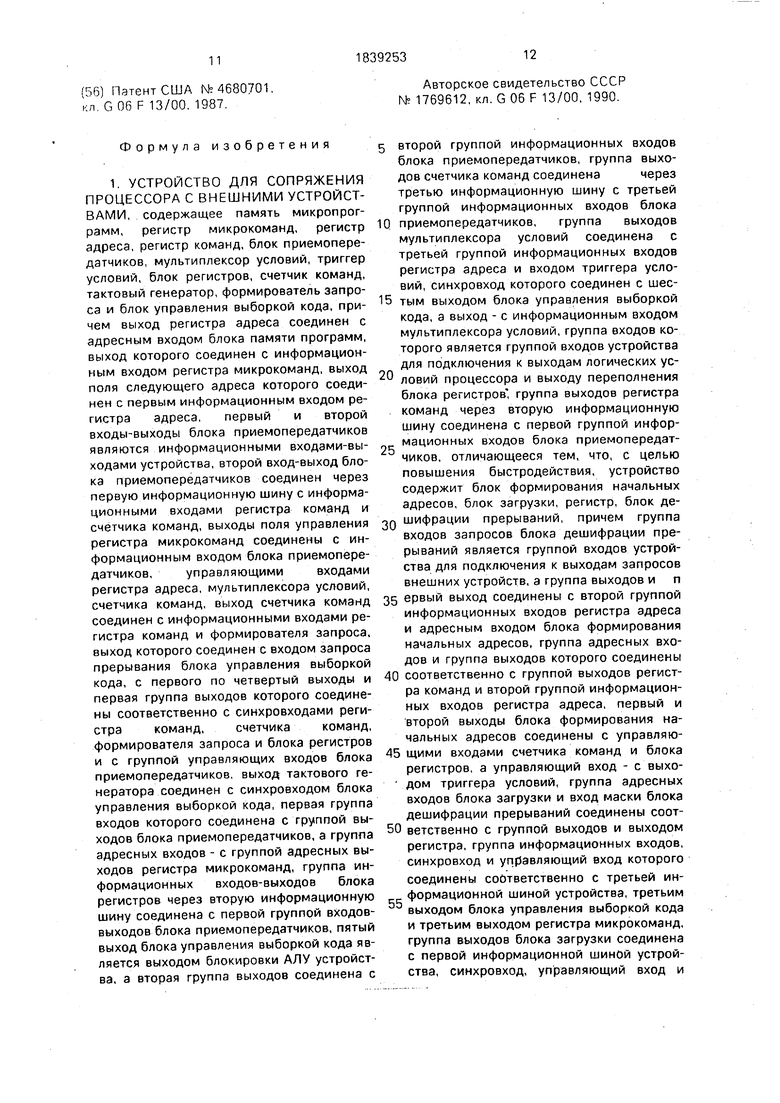

Схема предлагаемого устройства приведена на фиг. 1; на фиг. 2 изображена схема блока дешифрации прерываний; на фиг. 3 показаны блок начальной загрузки и регистры маски.

Устройство содержит (фиг. 1) тактовый генератор 1, память 2 микропрограмм, регистр 3 микрокоманд, регистр 4 адреса, ре- гистр 5 команд, блок приемопередатчиков 6, мультиплексор 7 условий, триггер 8 условий, блок 9 регистров, формирователь 10 запроса, счетчик 11 команд, блок 12 управления выборкой кода, блок 13 формирования на- чальных адресов, блок 14 начальной загрузки, регистр 15, блок 16 дешифрации прерываний.

Блок дешифрации прерываний (фиг. 2) содержит регистр 17 запросов, шифратор

18, регистр 19 маски, элементы И-НЕ 20,21, 22,23,24, формирователь 25 импульса, триггеры 26, 27, 28, передатчик 29. На фиг. 3 изображены блок 14 начальной загрузки, регистры 15.1 и 15.2 маски, элемент И-НЕ 30. Кроме того, на фигурах показаны системная шина 31 ЭВМ, шины В, Y, А - 32, 33, 34,

Устройство предназначено для выборки, дешифрации и исполнения потока команд, обработки прерываний от внешних устройств, обслуживания запросов на прямой доступ к памяти, операций начальной загрузки при обмене внутренних шин процессора с системной шиной ЭАМ. Оно является микропрограммным устройством, Внутренняя архитектура процессора трех- шинная. Разрядность обрабатываемых процессоров данных 32 бита.

Количество тактов, затрачиваемое устройством на исполнение команды, зависит от ее сложности. Большинство простых команд исполняется за 1-3 такта, т.е. время исполнения таких команд 195-500 не, включая время выборки кода.

Системная шина 31 ЭВМ - быстродействующий канал обмена информацией, соединяющей центральный процессор, память и все внешние устройства. Шина содержит 58 линий связи, Минимальное время обмена данными между устройствами 300 не. Разрядность передаваемых данных 32 бита. Устройство обмена обслуживает запросы прерываний от внешних устройств, контролирует предоставление прямого доступа к памяти. Шина содержит 32 линии адреса данных, остальные линии являются управляющими.

Память 2 микропрограмм реализована на восьми микросхемах 556РТ18, регистр 3 микрокоманд представляет собой конвейерный регистр, реализованный на пяти микросхемах 531ИР23 и шести микросхемах 1804ИР1. Ширина слова микрокоманды 64 разряда. Микропрограмма хранится в памяти 2 микропрограмм. Длина микропрограмм 2048 микрокоманд. Текущая исполняемая микрокоманда хранится в конвейерном регистре 3 микрокоманд. В микрокоманде поля адреса регистра 4 адреса и константы совмещены. Через блок приемопередатчиков 6 младший байт этого поля может быть выдан на шину В. Регистр 4 адреса выполнен на микросхеме 1804ВУ4. Регистр 5 команд выполнен на четырех микросхемах 531ИР22. Блок приемопередатчиков выполнен на микросхемах 531АПЗ и обеспечивает коммутацию внутренних шин устройства и внешней шины (канала). При этом в качестве адреса обращения могут выбираться шины

А, В, Y. Источником передаваемых данных может быть только шина В. В роли приемника данных от внешних устройств (или памяти) может выступать только шина Y. Управление коммутацией шин осуществля- ется микропрограммой, Мультиплексор 7 условий выполнен на микросхеме 531КП7, триггер 8 условий - на микросхеме 531ТМ2. Блок 9 регистров, реализованный в виде двухпортовой стековой памяти, выполнен на восьми микросхемах 1802ИР1, а указатель стека - на микросхеме 531 НЕ 17, подключен к шине В.

Работа устройства основана на выполнении программы, записанной в памяти программ ЭВМ (на фигурах не показана).

Слово команды с шины 31 ЭВМ через блок приемопередатчиков 6 поступает на шину Y и затем в регистр 5 команд. Каждому коду команды соответствует определенная последовательность микроопераций (микропрограмма), заложенных в памяти 2 микропрограмм. Начальный адрес каждой микропрограммы формируется в регистре 4 адреса как функция от кода поступающей команды с блока 13 с учетом логических условий, поступающих с мультиплексора 7 условий.

Любой цикл обращения к системной шине 31 начинается с адресации пассивно- го устройства. После завершения адресной части цикла процессор (или другое активное устройство) выполняет прием или передачу данных. Функции синхронизации при передаче адреса или приеме/передаче данных выполняют сигналы управления BADP, BOAT, BACK, BWAIT.

Команды из внешней памяти (на фигурах не показана) выбираются словами и за- носятся в регистр 5 команд. Приемопередатчики 6 обеспечивают коммутацию внутренних шин процессора и внешней шины ЭВМ. При этом в качестве адреса обращения к внешней шине могут выби- раться шины А, В, Y, Источником передаваемых данных может быть только шина В. В роли приемника данных от внешних устройств (или памяти) может выступать только шина Y. Управление коммутацией шин про- изводится блоком 12 управления выборкой кода, с помощью которого формируются циклы внешней шины. Блок 12, кроме того, осуществляет перезарядку регистра 5 команд при его опустошении, управляет пря- мым доступом к шине 31 ЭВМ, формирует тактовые сигналы процессора. Весь процессор тактируется одним сигналом С. За один такт этого сигнала исполняется одна микрокоманда. Блок 12 управления формирует

две различные длительности этого сигнала (по указанию текущей исполняемой микрокоманды) 180 и 120 не, Длинный такт используется в цикле передачи данных по внешней шине и в случае исполнения АЛУ команды, требующей сквозного переноса. Текущая микрокоманда с выхода регистра 3 микрокоманд производит увеличение содержания счетчика 11 команд или заносит в него новое значение с шины Y. При этом формирователь 10 запроса вырабатывает сигнал, поступающий на вход блока 12. Блок 12 управления выборкой-кода прекращает тактирование схем процессора, отключает от шины Y все источники и выдает на внешнюю шину текущее содержимое счетчика 11 команд в качестве адреса, после этого переключает шину Y на приме данных с внешней шины и заносит принятые данные в регистр 5 команд. Затем блок 12 возобновляет тактирование процессора. Блок 14 начальной загрузки представляет собой ПЗУ 573 РФ2 объемом 2 кбайт, подключенное к шине Y. Регистры 15.1 и 15.2 (выполненные на микросхемах 531ИР23 и 531ТМ9 соответственно) содержат адреса для блока 14 (ПЗУ). Во время исполнения процессором команд регистр 15 является физическим адресом маски прерываний.

При старте процессор считывает содержимое блока ПЗУ 14 в память по указанному в нем адресу и передает управление на считанную программу. Формат данных, записанных в ПЗУ 14, следующий, Данные рассматриваются как последовательный набор 32 разрядных слов. Байты ПЗУ 14 собираются в слове, начиная с младшего (младший байт ПЗУ соответствует младшему байту нулевого слова). Нулевое слово содержит адрес памяти, куда загружены остальные слова, начиная с второго. Первое слово - регистр процесса, которому передано управление после записи всей информации в память.

Если прерывания в регистре 15 не запрещены и есть запросы на прерывание, то переход по содержимому блока 13 не совершается, а делается переход по вектору микропребывания. Запрос на прерывание инициируется внешним устройством на выделенной ему одной из линий.

Таким образом, введение блоков формирования начальных адресов, блока загрузки, регистра и блока дешифрации прерываний, выполненного в предложенном виде, позволяет сократить время обработки информации, т.е. повысить быстродействие.

(56) Патент США №4680701, к л. G 06 F 13/00. 1987.

Авторское свидетельство СССР № 1769612, кл. G 06 F 13/00, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение 2 быстродействия Устройство содержит память микропрограмм, регистр микрокоманд регистр адреса, регистр команд блок приемопередатчиков, мультиплексор, триггер условий, блок регистров, счетчик команд тактовый генератор, формирователь запроса, блок управления выборкой кода. Новым является введение блока формирования начальных адресов, блока загрузки, регистра, блока дешифрации прерываний, причем последний содержит регистр запросов, шифратор, пять элементов И - НЕ. регистр маски, три триггера, формирователь импульса и передатчик. 1 злф-пы, 3 ил.

Формула изобретения

0

второй группой информационных входов блока приемопередатчиков, группа выходов счетчика команд соединеначерез третью информационную шину с третьей группой информационных входов блока

Q приемопередатчиков, группа выходов мультиплексора условий соединена с третьей группой информационных входов регистра адреса и входом триггера условий, синхровход которого соединен с шес5 тым выходом блока управления выборкой кода, а выход - с информационным входом мультиплексора условий, группа входов которого является группой входов устройства для подключения к выходам логических условий процессора и выходу переполнения блока регистров , группа выходов регистра команд через вторую информационную шину соединена с первой группой информационных входов блока приемопередатчиков, отличающееся тем, что, с целью повышения быстродействия, устройство содержит блок формирования начальных адресов, блок загрузки, регистр, блок деQ шифрации прерываний, причем группа входов запросов блока дешифрации прерываний является группой входов устройства для подключения к выходам запросов внешних устройств, а группа выходов и п

5 ервый выход соединены с второй группой информационных входов регистра адреса и адресным входом блока формирования начальных адресов, группа адресных входов и группа выходов которого соединены

0 соответственно с группой выходов регистра команд и второй группой информационных входов регистра адреса, первый и второй выходы блока формирования начальных адресов соединены с управляю5 щими входами счетчика команд и блока

регистров, а управляющий вход - с выхо дом триггера условий, группа адресных

входов блока загрузки и вход маски блока

дешифрации прерываний соединены соот0 ветственно с группой выходов и выходом регистра, группа информационных входов, синхровход и управляющий вход которого соединены соответственно с третьей информационной шиной устройства, третьим выходом блока управления выборкой кода и третьим выходом регистра микрокоманд, группа выходов блока загрузки соединена с первой информационной шиной устройства, синхровход, управляющий вход и

5

первый, второй, третий выходы блока дешифрации прерываний соединены соответственно с седьмым выходом блока управления выборкой кода и четвертым выходом регистра микрокоманд, входом логических условий блока управления выборкой кода, входом сброса регистра микрокоманд и выходом ответа устройства.

О

0

рого по четвертый входы второго элемента И - НЕ образуют вход маски блока, выход формирователя импульса соединен с вторым входом третьего элемента И - НЕ и вторым входом данных регистра маски, второй вход четвертого элемента И - НЕ соединен с единичным выходом первого триггера, а выход - с третьим входом третьего элемента И -НЕ и третьим входом данных регистра маски, нулевой выход второго триггера соединен с четвертым входом третьего элемента И - НЕ и четвертым информационным входом регистра маски, единичный выход. третьего триггера

5 соединен с его входом сброса, нулевой выход соединен с первым выходом блока, синхровходы регистра запросов, шифрато- . ра, управляющий вход регистра маски образуют управляющий вход блока, синхровходы третьего триггера, регистра маски и первый вход приемопередатчика образует синхровход блока, входы пятого элемента И - НЕ соединены с группой входов запросов блока, а выход соединен с входом при5 емопередатчика, первый, второй и третий выходы которого соединены соответственно с синхровходами первого, второго триггеров и входом данных третьего триггера, четвертый, пятый и шестой выходы приемопередатчика образуют первый выход блока, а седьмой и восьмой выходы - второй и третий выходы блока.

0

0

О т 6лот 12

дгг/ffQ Щёлоку 13

К5локц12

КрегиструЗ

Авторы

Даты

1993-12-30—Публикация

1990-03-13—Подача