Изобретение относится к вычислительной технике и может быть использовано при создании программируемых контроллеров, автоматизированных систем управления технологическими процессами (АСУТП), а также в системах автоматизации научных экспериментов.

При проведении работ, носящих экспериментальный характер, в частности при отработке изделий и узлов ракетно-технической техники (РКТ), в том числе и в условиях имитации реальной окружающей среды использования, стоят задачи управления объектом испытания, технологическим оборудованием, а также техническими средствами АСУТП.

Одной из основных задач, стоящих перед АСУТП, при проведении экспериментальных работ по отработке изделий РКТ является управление узлами и агрегатами по временным циклограммам, определяемыми программой испытаний.

Циклограммы таких работ отличаются значительной сложностью, а также включают в себя функции обработки (конъюнкция, дизъюнкция, инверсия и т.д.). Длительность циклограмм варьируется в диапазоне от десятка секунд до нескольких часов. При этом дискретность задания временных интервалов должна соответствовать 0,1 мс. Число включений достигает нескольких тысяч при изменении временных интервалов в широком диапазоне - от 1 мс до 500 с. Характер управления исполнительными элементами в реализации одного эксперимента одновременно может носить циклический и нециклический характер. При этом выдвигаются довольно высокие требования к точности привязки формируемых управляющих воздействий к реальному времени эксперимента.

Таким образом, разрешение проблемы организации программно-логического временного управления по сложности циклограмм является актуальной задачей.

Известно программно-логическое временное устройство [1] , содержащее арифметический блок, память, макропрограммный регистр, адресный регистр, селектор, составленный из И-схемы, декодер памяти, соединенные между собой межэлементными связями. Устройство позволяет реализовать программно-логическое временное управление. Данное устройство обеспечивает высокоскоростное управление исполнительными элементами за счет параллельности реализации микропрограммного управления и одновременного уменьшения требования к оперативной памяти. Однако использование данного устройства ограничено при реализации программно-временных циклограмм управления, так как время обработки сигналов прерывания таймера и время его загрузки последующими временными интервалами требуют времени как для формирования интервалов, так и для формирования команд управления, а следовательно, времени занятости интерфейса связи, соединяющего модули, входящие в устройство. Это вносит погрешность как в формирование временных интервалов, так и в выдачу команд управления. Учитывая, что количество временных интервалов может достигать десятков тысяч, вносится значительная погрешность в циклограммы эксперимента, что недопустимо при проведении экспериментальных работ, так как это приводит к рассинхронизации управляющих сигналов исполнительными элементами с системой регистрации параметров, а следовательно, и к искажению программы поставленного эксперимента.

Наиболее близким по технической сущности к заявляемому изобретению является программно-логическое временное устройство [2], реализующее микропрограммное управление. Устройство содержит центральный процессор, элемент 2-И, оперативно-запоминающее устройство временных команд, блок выходных каналов, двоичный счетчик, соединенные между собой соответствующими межэлементными связями.

Данное устройство позволяет формировать временные команды управления, и, кроме того, за счет закрытия ключей, отсоединяющих шину данных центрального процессора во время реализации циклограмм, возможна реализация параллельной обработки информации по функциям дизъюнкции, конъюнкции, инверсии и т.д.

Однако данное устройство не позволяет формировать одновременно циклический и нециклический характер управления исполнительными элементами, так как центральный процессор не может одновременно реализовать две или несколько микропрограмм управления, и, кроме того, при перестройке микропрограмм в реальном масштабе времени, что обусловлено требованиями программ эксперимента, вносится погрешность в точность формирования команд управления. Это приводит к накоплению ошибки при реализации программ управления, содержащих значительное количество микропрограмм.

Таким образом, узкие функциональные возможности и низкая точность формирования временных команд управления при реализации сложных циклограмм ограничивают его применение при управлении экспериментальными работами.

Техническая задача, решаемая изобретением, заключается в расширении функциональных возможностей устройства при обеспечении точности формирования временных команд управления.

Это достигается тем, что в программно-логическое временное устройство, содержащее центральный процессор, элемент 2-И, оперативно-запоминающее устройство временных команд, блок выходных каналов, двоичный счетчик, согласно изобретению, введены пульт управления, интерфейс устройства, девять информационно-управляющих шин, оперативно-запоминающее устройство, постоянно-запоминающее устройство, блок таймера времени эксперимента, блок таймера выдачи импульсных команд, блок выходных усилителей, два буферных регистра, причем центральный процессор и пульт управления первой и второй информационно-управляющими шинами соответственно соединены с интерфейсом устройства, к которому через третью информационно-управляющую шину подключен блок таймера выдачи импульсных команд, выходы которого являются управляющими входами блока выходных усилителей, выходы блока выходных усилителей управляют исполнительными элементами, четвертой информационно-управляющей шиной к интерфейсу устройства подключен блок таймера времени эксперимента, выход которого соединен со счетным входом двоичного счетчика, входы параллельного занесения информации которого через пятую информационно-управляющую шину связаны с интерфейсом устройства, выходы двоичного счетчика соединены со входами первого буферного регистра, выходы которого шестой информационно-управляющей шиной соединены с адресными входами оперативно-запоминающего устройства временных команд, шина данных которого имеет связь с блоком выходных каналов, выходы которого управляют исполнительными элементами, вход записи оперативно-запоминающего устройства временных команд соединен со входом выборки второго буферного регистра и шиной записи интерфейса устройства, а вход чтения - с выходом элемента 2-И, один из входов которого соединен с шиной чтения интерфейса устройства, а второй вход - с выходом блока таймера времени эксперимента, который в свою очередь соединен с шиной запроса прерывания интерфейса устройства и входом выборки первого буферного регистра, интерфейс устройства седьмой информационно-управляющей шиной соединен с входом второго буферного регистра, выходы которого шестой информационно-управляющей шиной соединены с шиной данных и адреса оперативно-запоминающего устройства выходных команд, а восьмой и девятой информационно-управляющими шинами соответственно соединены с постоянно-запоминающим устройством и с оперативно-запоминающим устройством.

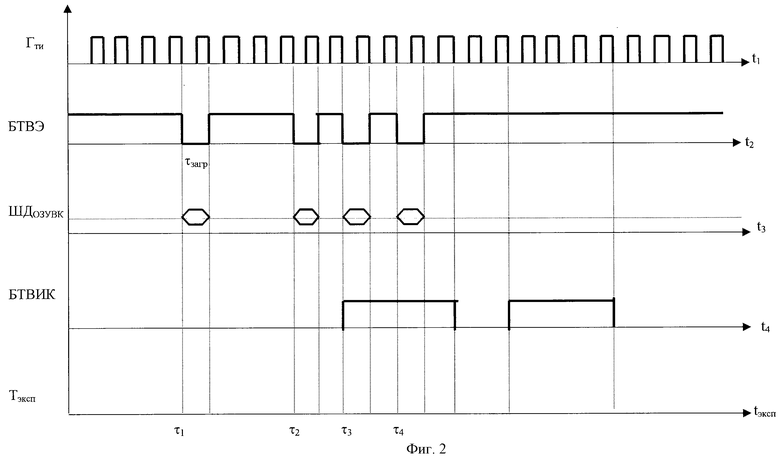

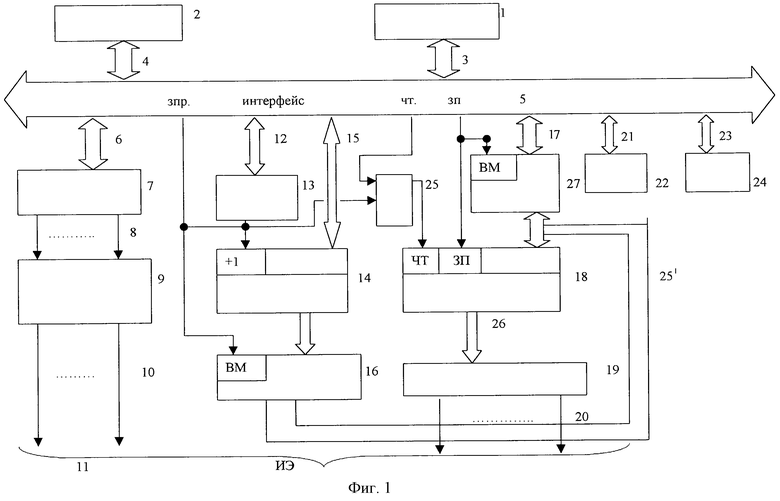

На фиг. 1 представлена функциональная схема программно-логического временного устройства, а на фиг.2 представлена временная диаграмма его работы.

Программно-логическое устройство содержит центральный процессор 1, элемент 2-И 25, оперативно-запоминающее устройство временных команд 18, блок выходных каналов 19, двоичный счетчик 14, пульт управления 2, интерфейс устройства 5, девять информационно-управляющих шин 4, 3, 6, 12, 15, 17, 21, 23, 25', оперативно-запоминающее устройство 24, постоянно-запоминающее устройство 22, блок таймера времени эксперимента 13, блок таймера выдачи импульсных команд 7, блок выходных усилителей 9, два буферных регистра 16, 27.

Центральный процессор 1 и пульт управления 2 первой 3 и второй 4 информационно-управляющими шинами соответственно соединены с интерфейсом устройства 5. К интерфейсу устройства 5 через третью информационно-управляющую шину 6 подключен блок таймера выдачи импульсных команд 7, выходы 8 которого являются управляющими входами блока выходных усилителей 9. Выходы 10 блока выходных усилителей 9 управляют исполнительными элементами 11. Через четвертую информационно-управляющую шину 12 к интерфейсу устройства 5 подключен блок таймера времени эксперимента 13, выход которого соединен со счетным входом двоичного счетчика 14, имеющего через пятую информационно-управляющую шину 15 связь с интерфейсом устройства 5. Выходы двоичного счетчика 14 соединены с входами первого буферного регистра 16, выходы которого шестой информационно-управляющей шиной 25' соединены с шиной адреса оперативно-запоминающего устройства временных команд 18.

Шина данных 26 оперативно-запоминающего устройства временных команд 18 имеет связь с блоком выходных каналов 19, выходы 20 которого управляют исполнительными элементами 11. Вход записи оперативно-запоминающего устройства временных команд 18 соединен с входом выборки второго буферного регистра и шиной записи интерфейса устройства 5, а вход чтения - с выходом элемента 2-И 25. Один из входов элемента 2-И 25 соединен с шиной чтения интерфейса устройства 5, а второй вход - с выходом блока таймера времени эксперимента 13, который в свою очередь соединен с шиной запроса прерывания интерфейса устройства 5. Интерфейс устройства 5 седьмой информационно-управляющей шиной 17 соединен с входами второго буферного регистра 27, выходы которого шестой информационно-управляющей шиной 25' соединены с шиной адреса и данных оперативно-запоминающего устройства временных команд 18, а восьмой информационно-управляющей шиной 21 - с постоянно-запоминающим устройством 22 и девятой информационно-управляющей шиной 23 - с оперативно-запоминающим устройством 24.

Центральный процессор 1 осуществляет управление устройством (фиг.1), формирование программ управления. Пульт управления 2 служит для связи устройства с оператором и визуального отображения работы устройства.

Центральный процессор 1 и пульт управления 2 соединены информационно-управляющими шинами 3 и 4 соответственно с интерфейсом устройства 5, выполненным в стандарте PC1.

Блок таймера выдачи импульсных команд 7 (выполнен по патенту РФ 2071168) служит для организации циклических программ управления исполнительными элементами, которые позволяют формировать длительность включения, паузу между включениями и число включений.

Блок таймера времени эксперимента 13 (выполнен по патенту РФ 2001507) служит для выдачи одиночных импульсных команд в заданные моменты времени эксперимента.

Двоичный счетчик 14 служит для формирования адреса для оперативно-запоминающего устройства временных команд 18, которое позволяет формировать одиночные импульсные команды управления на исполнительные элементы параллельным кодом.

Блок выходных усилителей 9 и блок выходных каналов 19 служат для нормализации сигналов управления к уровням, необходимым для управления исполнительными элементами. Постоянно-запоминающее устройство 22 служит для хранения программ экспериментальных работ. Оперативно-запоминающее устройство 24 служит для оперативной работы с сервисными программами устройства.

Работа устройства осуществляется следующим образом. По выбору оператором номера эксперимента в соответствии с требованиями программы центральный процессор 1 через второй буферный регистр 27 загружает оперативно-запоминающее устройство временных команд 18, начиная с некоторого адреса Аm, кодами, соответствующими управляющим сигналам на исполнительные элементы, на глубину k, равную количеству временных интервалов, задействованных в данной программе. Таким образом, каждому временному интервалу будет соответствовать свой набор команд управления. В двоичный счетчик 14 по информационно-управляющей шине 15, используя информационные входы параллельной записи, центральный процессор 1 заносит слово, соответствующее адресу Am-1. В оперативно-запоминающем устройстве 24 центральный процессор 1 организует два блока памяти: один для массива загружаемых временных интервалов, другой для массива параметров циклических программ. Таким образом заканчивается подготовительная часть подготовки к эксперименту.

Работа устройства в режиме управления экспериментом иллюстрируется временной диаграммой, приведенной на фиг.2, где ось t2 отображает выдачу импульсных команд с блока таймера времени эксперимента (БТВЭ), ось t3 отображает выдачу импульсных команд управления исполнительными элементами с шины данных оперативно-запоминающего устройства временных команд (ШДОЗУВК), ось t4 отображает выдачу циклических команд управления исполнительными элементами с блока таймера выдачи импульсных команд (БТВИК), ось tэксп отображает временные интервалы, формируемые устройством времени эксперимента (Тэксп).

На счетные входы блока таймера времени эксперимента и блока таймера выдачи импульсных команд с генератора тактовых импульсов (Гти) поступает импульсная последовательность с частотой, определяемой требованиями к дискретности задания временных интервалов, в данном случае равной 10 кГц (см. фиг. 2, ось t1). По команде "ПУСК" центральный процессор из блока памяти массива временных интервалов считывает первую ячейку памяти, соответствующую первому временному интервалу, и загружает блок таймера времени эксперимента 13. По отработке временного интервала τ1 (см. фиг.2, ось tэксп) блок таймера времени эксперимента 13 выдает импульс длительностью, равной периоду тактовой частоты (см. фиг. 2, ось t2), который поступает на счетный вход двоичного счетчика 14. Двоичный счетчик 14 формирует первый адрес Аm для оперативно-запоминающего устройства временных команд.

Одновременно импульс с блока таймера времени эксперимента 13 поступает на разрешающий вход первого буферного регистра 16, и код адреса, сформированный двоичным счетчиком 14, по шестой информационно-управляющей шине 25' поступает на адресные входы оперативно-запоминающего устройства временных команд 18. Импульс с блока таймера времени эксперимента 13 через схему 2-И 25 поступает на вход чтения оперативно-запоминающего устройства временных команд 18. Таким образом, ячейка памяти с адресом, сформированным двоичным счетчиком 14, считывается на блок выходных каналов 19, который формирует управляющие сигналы на исполнительные элементы 11, не отвлекая на это ресурсы центрального процессора 1. Выходной импульс с блока таймера времени эксперимента 13 через интерфейс устройства 5 также поступает на шину запроса прерывания центрального процессора 1, который загружает блок таймера времени эксперимента 13 следующим временным интервалом. Таким образом осуществляется параллельная работа центрального процессора 1 по загрузке таймера времени эксперимента 13 с функциями выдачи управляющих команд на исполнительные элементы 11, что значительно повышает быстродействие системы.

Если в программе проведения экспериментальных работ необходимо выдавать на исполнительные клеммы циклические импульсы команды управления с определенными длительностью, паузой между включениями и числом включений, то центральный процессор 1 по запросу прерывания вместе с блоком таймера времени эксперимента 13 загружает блок таймера выдачи импульсных команд 7, который по окончании загрузки (см. фиг.2, ось t3) начинает формировать импульсные команды управления с заданными длительностью, паузой и числом включений. Импульсные команды управления поступают через блок выходных усилителей 9 на исполнительные элементы. Так осуществляется независимая параллельная работа центрального процессора 1, блока таймеров времени эксперимента 13 и блока таймеров выдачи импульсных команд 7. Поскольку в функции центрального процессора 1 входит только загрузка таймеров, а управление исполнительными элементами осуществляют другие устройства, это ведет к значительному сокращению статической и динамической длин программного обеспечения. Это в свою очередь позволяет осуществить центральному процессору 1 выполнение подпрограммы по запросу прерывания за период тактовой частоты, поступающей на блоки таймеров 13 и 7. А так как таймеры 13 и 7 осуществляют свои отсчеты по заднему фронту импульсов тактовой частоты, то это позволяет вести сквозной отсчет времени эксперимента, исключая инструментальную погрешность (кроме погрешности генератора тактовых импульсов).

Так, за счет использования принципов независимости параллельной работы данное устройство обеспечивает высокие быстродействие и точность задания временных команд управления, исключая временные сдвиги между командами управления. Это позволяет значительно повысить качество проведения экспериментальных работ.

Источники информации

1. Патент США 4467415, МКИ G 06 F 9/36, 1984 г.

2. Патент РФ 2079876, МКИ G 06 F 9/22, 1997.

Изобретение относится к вычислительной технике и может быть использовано при создании программируемых контроллеров, в автоматизированных системах управления технологическими процессами, а также в системах автоматизации научных экспериментов. Техническим результатом является расширение функциональных возможностей путем одновременной реализации программ, носящих циклический и нециклический характер, при одновременном повышении точности выдачи временных команд управления исполнительными элементами. Устройство содержит центральный процессор, элемент 2-И, оперативно-запоминающее устройство временных команд, блок выходных каналов, двоичный счетчик, пульт управления, интерфейс устройства, девять информационно-управляющих шин, оперативно-запоминающее устройство, постоянно-запоминающее устройство, блок таймера времени эксперимента, блок таймера выдачи импульсных команд, блок выходных усилителей, два буферных регистра. 2 ил.

Программно-логическое временное устройство, содержащее центральный процессор, элемент 2-И, оперативно-запоминающее устройство временных команд, блок выходных каналов, двоичный счетчик, отличающееся тем, что в него введены пульт управления, интерфейс устройства, девять информационно-управляющих шин, оперативно-запоминающее устройство, постоянно-запоминающее устройство, блок таймера времени эксперимента, блок таймера выдачи импульсных команд, блок выходных усилителей, два буферных регистра, причем центральный процессор и пульт управления первой и второй информационно-управляющими шинами соответственно соединены с интерфейсом устройства, к которому через третью информационно-управляющую шину подключен блок таймера выдачи импульсных команд, выходы которого являются управляющими входами блока выходных усилителей, выходы блока выходных усилителей управляют исполнительными элементами, четвертой информационно-управляющей шиной к интерфейсу устройства подключен блок таймера времени эксперимента, выход которого соединен со счетным входом двоичного счетчика, входы параллельного занесения информации которого через пятую информационно-управляющую шину связаны с интерфейсом устройства, выходы двоичного счетчика соединены со входами первого буферного регистра, выходы которого шестой информационно-управляющей шиной соединены с адресными входами оперативно-запоминающего устройства временных команд, шина данных которого имеет связь с блоком выходных каналов, выходы которого управляют исполнительными элементами, вход записи оперативно-запоминающего устройства временных команд соединен со входом выборки второго буферного регистра и шиной записи интерфейса устройства, а вход чтения - с выходом элемента 2-И, один из входов которого соединен с шиной чтения интерфейса устройства, а второй вход - с выходом блока таймера времени эксперимента, который, в свою очередь, соединен с шиной запроса прерывания интерфейса устройства и входом выборки первого буферного регистра, интерфейс устройства седьмой информационно-управляющей шиной соединен с входом второго буферного регистра, выходы которого шестой информационно-управляющей шиной соединены с шиной данных и адреса оперативно-запоминающего устройства выходных команд, а восьмой и девятой информационно-управляющими шинами соответственно соединены с постоянно-запоминающим устройством и с оперативно-запоминающим устройством.

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| RU 2071168 C1, 27.12.1996 | |||

| ПРОГРАММНОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 1992 |

|

RU2006895C1 |

| ПРОГРАММНОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 1994 |

|

RU2097820C1 |

| Устройство микропрограммного управления | 1988 |

|

SU1661762A1 |

| Программное временное устройство | 1987 |

|

SU1418654A1 |

| US 4467415 A, 21.08.1984 | |||

| СПОСОБ КОРРЕКЦИИ АСТИГМАТИЗМА У ПАЦИЕНТОВ С ТОНКОЙ РОГОВИЦЕЙ | 2011 |

|

RU2456972C1 |

Авторы

Даты

2003-02-20—Публикация

2001-10-09—Подача