Изобретение относится к цифровой вычислительной технике и может быть использовано, в частности, при построении арифметических устройств ЦВМ.

Известны устройства, в которых связь между разрядами осуществляется цепью распространения переносов.

Известен параллельный комбинационный сумматор, который содержит n полных одноразрядных сумматоров, выходы переносов которых подключены к первым входам элементов И переноса, вторые входы которых соединены с дополнительной входной шиной. Выходы элементов ИЛИ переноса подключены к первым входам элементов И переноса, вторые входы которых (за исключением элемента ИЛИ переноса старшего разряда) соединены с выходом элемента И, первый вход которого соединен со входом переноса младшего разряда, а второй с выходом элемента НЕ. Ко второму входу элемента ИЛИ переноса старшего разряда подключен выход элемента И. Выходы элемента ИЛИ переноса подключены ко входам переносов старших разрядов [1]

Известен параллельный сумматор с одновременным переносом, который содержит блок формирования поразрядных сумм и поразрядных переносов, в состав которого входят четыре элемента образования поразрядных сумм и поразрядных переносов, блок формирования переносов во все разряды, в состав которого входят три элемента формирования переноса в старший и два последующих разряда соответственно, блок формирования результата, в состав которого входят четыре элемента учета переносов [2]

Наиболее близким к изобретению является вычислительное устройство, описанное в работе [3] Устройство содержит блок поразрядной арифметики, блок сдвига, блок формирования переносов, группу элементов ИЛИ, блок формирования результата, причем первая и вторая группы входов бока поразрядной арифметики, входы блока сдвига, первые группы входов блока формирования переносов и блока формирования результата подключены к входам устройства, первая и вторая группы входов группы элементов ИЛИ подключены соответственно к вторым группам выходов блока поразрядной арифметики и группы элементов ИЛИ, вторая и третья группы входов блока формирования результата подключены соответственно к выходам блока формирования переносов и группы элементов ИЛИ.

Недостатком прототипа являются ограниченные функциональные возможности, поскольку он выполняет только арифметическую операцию сложения и логическую операцию сдвига Р-ичного числа на один эквивалентный двоичный разряд вправо.

Целью изобретения является расширение функциональных возможностей устройства за счет добавления функции криптографического преобразования передаваемой информации.

Поставленная цель достигается тем, что вычислительное устройство, содержащее блок поразрядной арифметики, блок сдвига, блок формирования переносов и группу элементов ИЛИ, причем второй и третий входы блока формирования переносов подключены к первым выходам соответственно блока поразрядной арифметики и блока сдвига, а первый и второй входы группы элементов ИЛИ подключены к вторым выходам соответственно блока поразрядной арифметики и блока сдвига, содержит первый и второй блоки распознавания исходных чисел, элемент ИЛИ на два входа, первый и второй дешифраторы переносов, первый и второй блоки формирования исходных чисел, первый, второй и третий блоки коммутации, шифратор переносов и блок формирования результата по "ключу", причем первые входы блоков распознавания исходных чисел и блока формирования результата по "ключу" подключены к третьему входу устройства, вторые входы первого и второго блоков распознавания исходных чисел подключены соответственно к четвертому и пятому входам устройства, первый и второй входы элемента ИЛИ подключены соответственно к первому и второму входам устройства, входы первого и второго дешифраторов переносов подключены к первым выходам соответственно первого и второго блоков распознавания исходных чисел, первые входы блоков формирования исходных чисел подключены к выходу элемента ИЛИ на два входа, вторые входы первого и второго блоков формирования исходных чисел подключены к выходам соответственно первого и второго дешифраторов переносов, третьи входы первого и второго блоков формирования исходных чисел подключены ко вторым выходам соответственно первого и второго блоков распознавания исходных чисел, первые входы первого и второго блоков коммутации подключены к первому входу устройства, первый вход третьего блока коммутации подключен ко второму входу устройства, второй вход первого блока коммутации подключен к выходу первого блока формирования исходных чисел, вторые входы второго и третьего блоков коммутации подключены к выходу второго блока формирования исходных чисел, первый и второй входы блока поразрядной арифметики подключены к выходам соответственно первого и второго блоков коммутации, а входы группы элементов ИЛИ подключены к выходу третьего блока коммутации, входы шифратора переносов подключены к выходам блока формирования переносов, первый, второй и третий входы блока формирования результата по "ключу" подключены соответственно к третьему входу устройства, выходам шифратора переносов и выходам группы элементов ИЛИ.

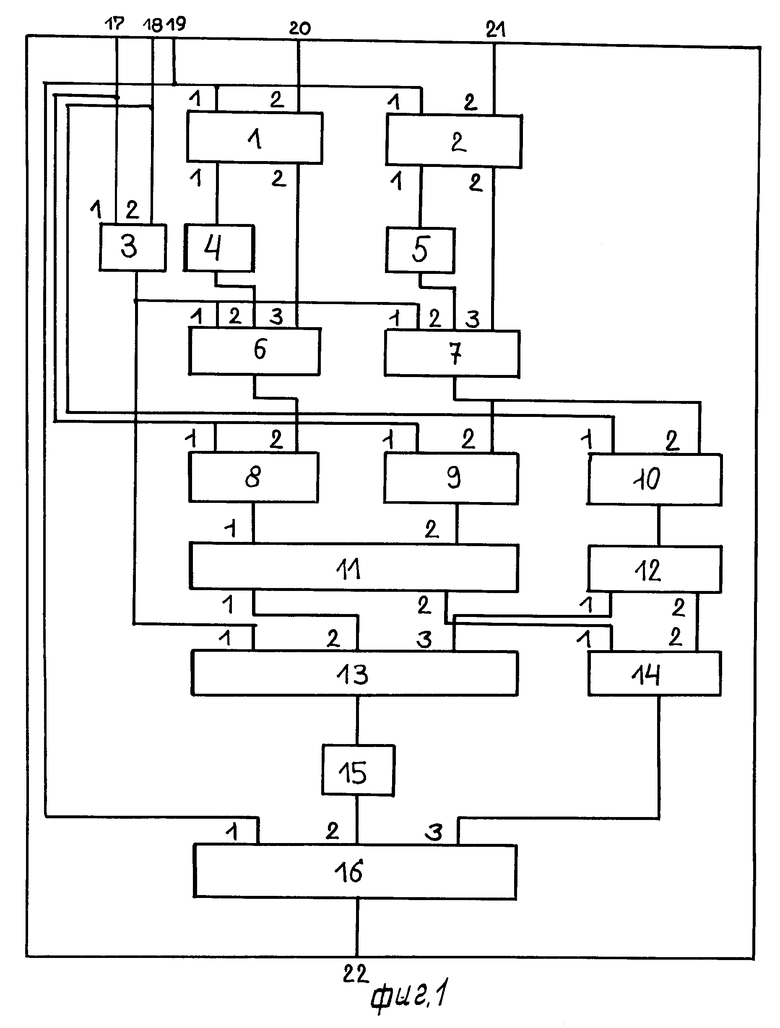

Блок-схема предлагаемого вычислительного устройства представлена на фиг. 1. Устройство содержит первый и второй блоки распознавания исходных чисел соответственно блоки 1 и 2, элемент ИЛИ на два входа блок 3, первый и второй дешифраторы переносов соответственно блоки 4 и 5, первый и второй блоки формирования исходных чисел соответственно блоки 6 и 7, первый, второй и третий блоки коммутации соответственно блоки 8, 9 и 10, блок 11 поразрядной арифметики, блок 12 сдвига, блок 13 формирования переносов, группу 14 элементов ИЛИ, шифратор 15 переносов и блок 16 формирования результата по "ключу".

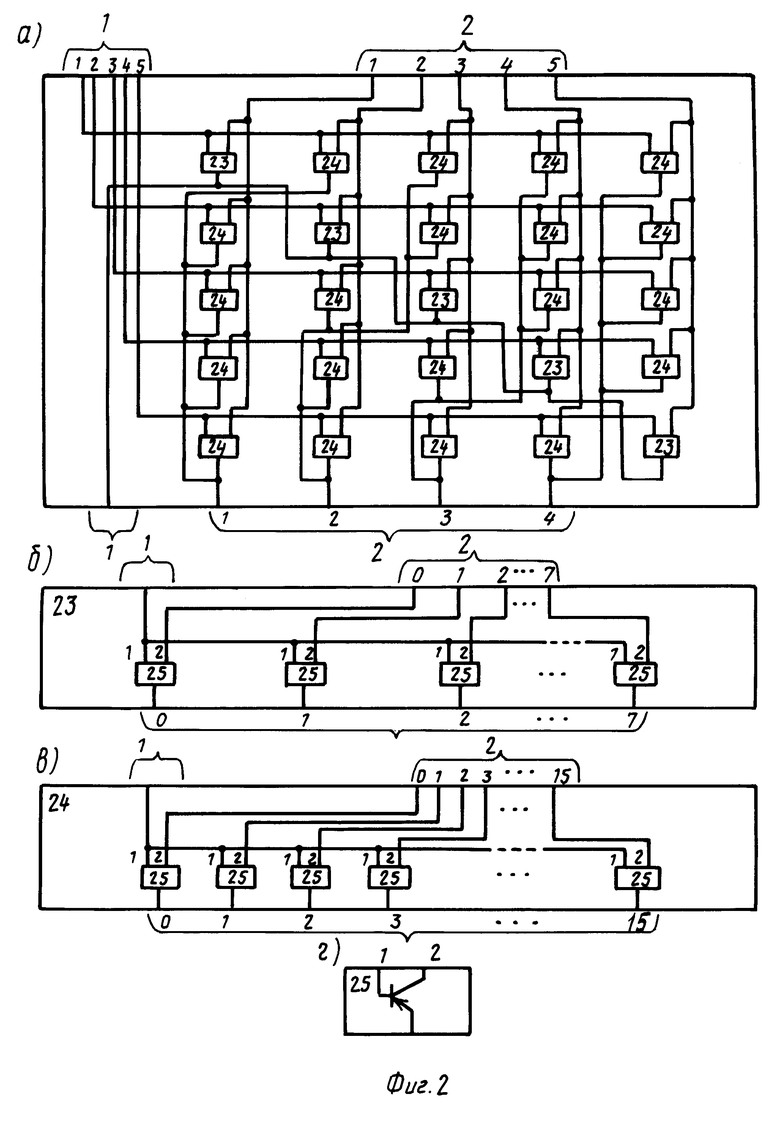

Блок 1 и блок 2 (фиг. 2, а) представляют собой комбинационные схемы, каждая из которых включает nр+1 (где nр разрядность числа, представленного в счислении с основанием Р) блоков 23 (фиг. 2, б) и 5˙np блоков 24 (фиг. 2, в). При этом блоки 23 и 24 содержат соответственно по Р/2 и Р двухвходовых элементов И (фиг. 2, г) каждый. Вход 1 (вход 2) каждого из блоков 23 и 24 подключен к одному из входов группы 1 (группы 2) входы блока 1 либо блока 2, номер которой совпадает с номером строки (столбца) схемы, в которой указанный блок располагается.

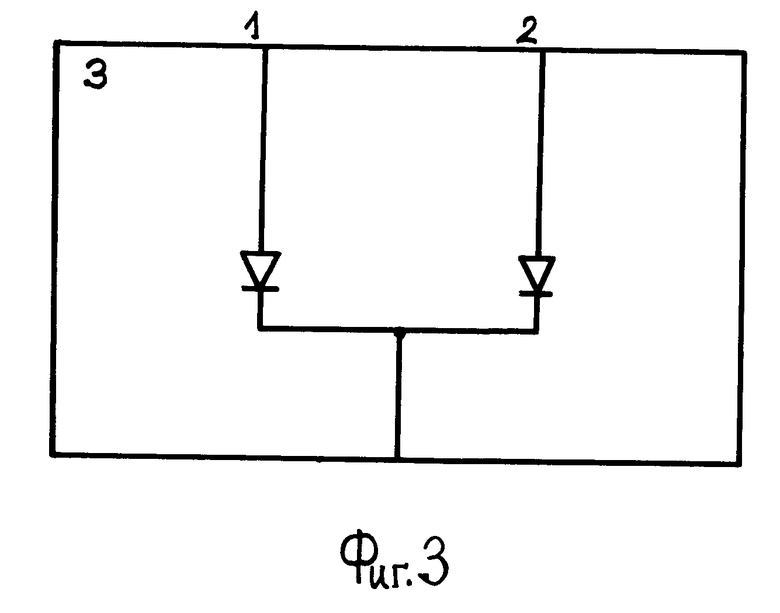

Блок 3 (фиг. 3) представляет собой двухвходовый элемент ИЛИ.

Блок 4 и блок 5 комбинационные схемы. На фиг. 4 они представлены для примера на диодных сборках.

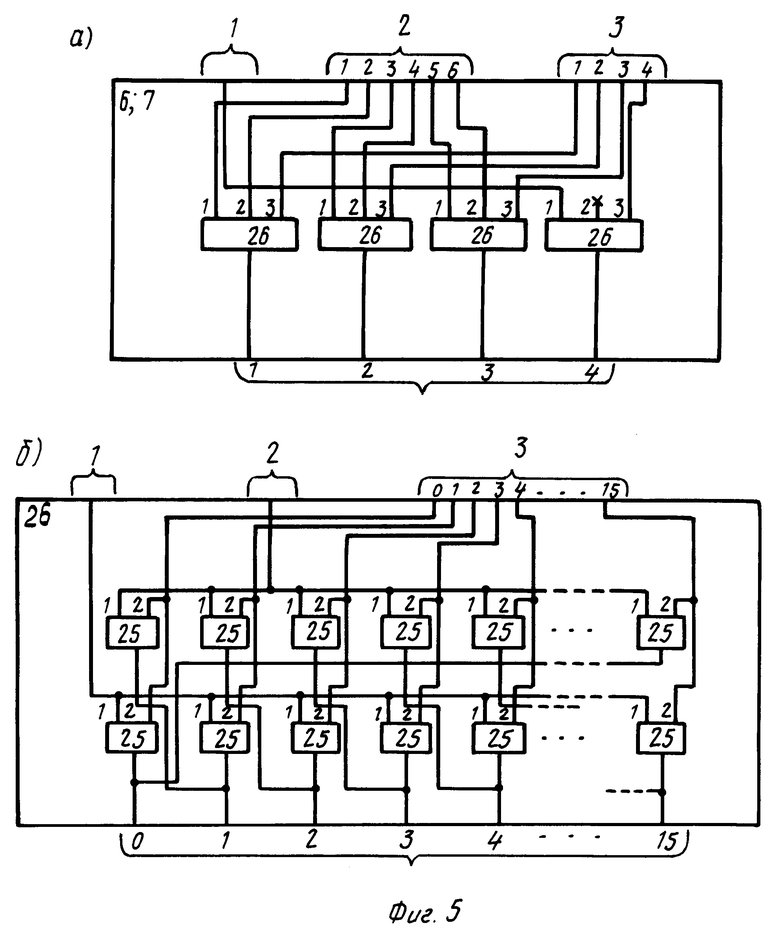

Блок 6 и блок 7 (фиг. 5, а) содержат по группе матриц 26, каждая из которых имеет три входа. При этом первые и вторые входы матриц 26 с порядковыми номерами 1, 2 и 3 подключены к входам второй группы входов блоков 6, 7, а первый вход матрицы 26 с порядковым номером 4 подключен к входу первой группы блоков 6, 7. Третьи входы всех матриц 26 объединены в третью группу входов блока 6, 7.

Матрица 26 (фиг. 5, б) содержит группу двухвходовых элементов И 25. При этом первые входы элементов И 25 с порядковыми номерами 1, 16 подключены к входу 2 блока 26, а первые входы элементов И 25 с порядковыми номерами 17, 32 к входу 1 блока 26. Входы 2 всех элементов 25 объединены в третью группу входов блока 26. Входы элементов 25 с порядковыми номерами 1 и 18, 2 и 19, 15 и 32, 16 и 17 объединены в общие выходные шины.

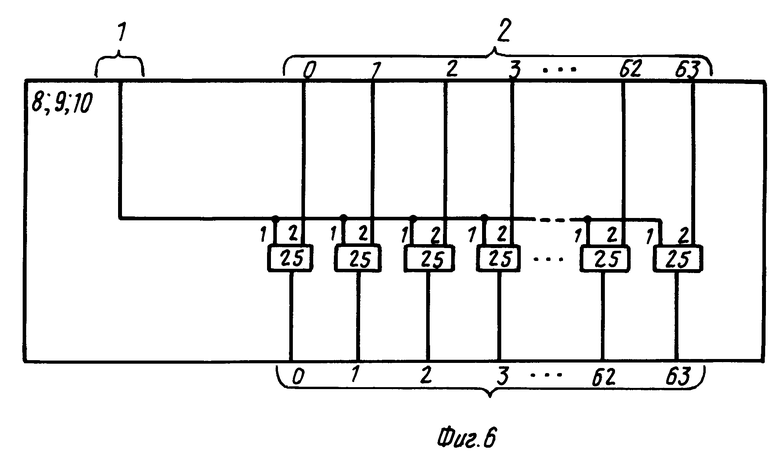

Блоки 8, 9 и 10 (фиг. 6) представляют собой коммутаторы, каждый из которых предназначен для передачи четырехразрядного шестнадцатеричного числа и содержит 64 двухвходовых элемента И 25.

Блоки 11, 12, 13 и 14 идентичны соответственно блокам 1, 2, 3 и 4 устройства прототипа, которые в работе [3] представлены применительно к счислению с основанием Р=4.

Блок 15 (фиг. 7) содержит 24 двухвходовых элемента (25) и представляет собой двухуровневую комбинационную схему.

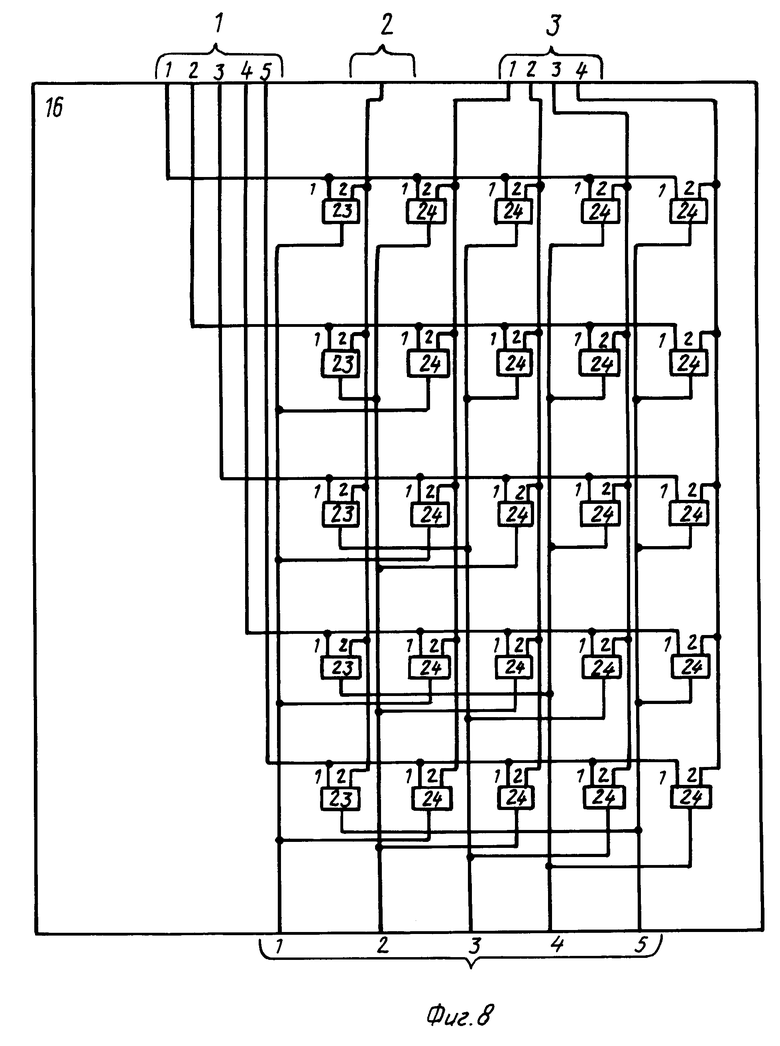

Блок 16 (фиг. 8) содержит 5 блоков 23 и 5.np блоков 24. При этом вход 1 блоков 23 и 24, расположенных в одной строке схемы, подключен к входу группы 1 входов блока 16, номер которого совпадает с порядковым номером строки. Вход 2 блоков 23 подключен к входу 2 блока 16, вход 2 блоков 24 к соответствующим входам группы 3 входов блока 16. Выход блока 23, расположенного в любой из строк схемы, подключен к тому выходу блока 16, номер которого совпадает с порядковым номером строки, в которой он располагается.

Устройство работает следующим образом.

При выполнении операции сложения исходные числа в закодированном виде поступают на шины 20 и 21 устройства и, следовательно, но входы 2 блоков 1 и 2. Одновременно с ними от входа 19 устройства по одной из шин группы 1 входов блоков 1 и 2 поступает ключ сигнал VI. При этом для представления каждой из цифр исходных чисел и ключа используется пространственное (позиционное)представление информации, предполагающее наличие в каждом разряде (для каждого из nр+1 входов группы 2 входов блока 1 и блока 2) наличие Р позиций и одного цифрового сигнала, вес которого определяется номером позиции, на которой этот сигнал в данный момент располагается. Например, наличие цифры 2 либо цифры 1 на входах блоков 23 и 24 предполагает наличие цифрового сигнала на входе, номер которого совпадает с номером представляемой цифры (т.е. на входных шинах с номерами 2 и 1 соответственно группы 2 входов). Наличие цифрового сигнала VI на одной из входных шин с номерами 1, 5 группы 1 входов блока 1 и блока 2 определяет выбор строки (блоков 24 и блока 23), соответствующей истинному значению исходного числа. При этом информация, соответствующая сумме по модулю в каждом разряде исходного числа, поступает на выходные шины 1, 4 группы 2 выходов блока 1 (блока 2), а цифра, соответствующая информации о переносах, подлежащих распространению в соответствующих разрядах исходного числа, на вход 1 рассматриваемого блока. С выходов 1 блока 1 и блока 2 цифра, соответствующая информации о переносах в значении первого и второго исходных чисел, поступает на входы первого и второго дешифраторов переносов блок 4 и блок 5 соответственно. Одновременно на вход 1 блока 3 поступает управляющий сигнал У2, определяющий прохождение информации через блоки 6 и 7, на входах которых получаются истинные значения соответственно первого и второго исходных чисел. При этом на вход 1 блоков 6 и 7 поступает управляющий сигнал У2 с выхода блока 3, на вход 2 значения переносов в соответствующие разряды передаваемого исходного числа, а на вход 3 значения поразрядных сумм каждого из разрядов исходного числа. На вход 1 блока 8 и вход блока 9 управляющий сигнал У2 поступает от входа 17 устройства. На вход 2 блока 8 и вход 2 блока 9 значения первого и второго исходных чисел поступают с выходов соответственно блоков 6 и 7. С выходов блоков 8 и 9 значения первого и второго исходных чисел поступают на первый и второй входы блока 11. С выходов 1 и выходов 2 блока 11 значения поразрядных переносов в соседний старший разряд и сумм по модулю Р (например, Р=16) поступают на входы 2 и 1 соответственно блоков 13 и 14. С выходов блока 13 значения переносов в соседние старшие разряды поступают на вход блока 15, в котором достигается их замена соответствующим кодом (например, Р-ичной цифрой, в рассматриваемом примере Р=16). С выхода блока 14 значения поразрядных сумм результата сложения поступают на вход 3 блока 16, на вход 2 которого поступают значения переносов в ближайшие к рассматриваемым старшие разряды. При этом информация о переноса закодирована Р-ичной (16-ричной) цифрой. На вход 1 блока 16 значение "ключа" (сигнал VI) поступает от входа 19 устройства. На выходе блока 16 появляется число, одна из цифр которого соответствует значению переносов в ближайшие к рассматриваемым старшие разряды, полученные в результате сложения аргументов. При этом место расположения закодированного значения переносов определяется кодом "ключа" VI.

При выполнении операции сдвига Р-ичного числа на один эквивалентный двоичный разряд вправо исходное число поступает на вход 21 устройства и, следовательно, на вход блока 2. Одновременно с ним от входа 19 устройства на одну из шин группы 1 входов блока 2 поступает "ключ" сигнал VI. С выхода 1 блока 2 на вход блока 5 в этом случае поступает информация о переносах, подлежащих учету в исходном числе.

Одновременно на вход 2 блока 3 поступает управляющий сигнал У3, определяющий прохождение входной информации через блок 7, на выходе которого получается истинное значение исходного числа. При этом на вход 1 блока 7 поступает управляющий сигнал У3 с выхода блока 3, на вход 2 значение переносов в соответствующие разряды передаваемого исходного числа, а на вход 3 значения поразрядных сумм каждого из разрядов исходного числа. На вход 1 блока 10 управляющий сигнал У3 поступает от входа 18 устройства. На вход 2 блока 10 значение исходного числа поступает с выхода блока 7. С выхода блока 10 значение исходного числа поступает на вход блока 12, с выходов 1 которого на входы 3 блока 13 поступают сигналы переносов нулей из разрядов с порядковыми номерами 2, 3 и 4 в разрядов с порядковыми номерами 1, 2 и 3 соответственно. Одновременно с выходов 2 блока 12 значения результата сдвига в каждом разряде поступают на входы 2 блока 14. С выходов блока 13 значения переносов нулей в соседние старшие разряды поступают на вход блока 15, в котором достигается их замена соответствующим кодом (например, Р-ичной цифрой; в рассматриваемом примере Р=16). С выходов блока 14 результат сдвига на один эквивалентный двоичный разряд вправо поступает на вход 3 блока 16, на вход 2 которого поступает с выходов блока 15 информация о переносах нулей в ближайшие к рассматриваемым старшие разряды, закодированная Р-ичной цифрой. При этом на вход 1 блока 16 значение "ключа" (сигнал VI) поступает от входа 19 устройства. На выходе блока 16 появляется число, одна из цифр которого соответствует значениям переносов в ближайшие к рассматриваемым старшие разряды. При этом место расположения закодированного значения переносов определяется кодом "ключа" VI.

Таким образом, введение первого и второго блоков распознавания исходных чисел, элемента ИЛИ на два входа, первого и второго дешифраторов переносов, первого и второго блоков формирования исходных чисел, первого, второго и третьего блоков коммутации, шифратора переносов и блока формирования результата по "ключу" позволяет увеличить функциональные возможности предложенного вычислительного устройства за счет добавления функции криптографического преобразования информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1991 |

|

RU2030792C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

| Устройство для умножения | 1981 |

|

SU974370A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ. С целью расширения функциональных возможностей за счет добавления функции криптографического преобразования передаваемой информации оно содержит первый и второй блоки распознавания исходных чисел, элемент ИЛИ на два входа, первый и второй дешифраторы переносов, первый и второй блоки формирования исходных чисел, первый, второй и третий блоки коммутации, шифратор переносов и блок формирования результата по ключу. 8 ил.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок поразрядной арифметики, блок сдвига, блок формирования переносов и группу элементов ИЛИ, причем второй и третий входы блока формирования переносов подключены к первым выходам соответственно блока поразрядной арифметики и блока сдвига, а первый и второй входы группы элементов ИЛИ подключены к вторым выходам соответственно блока поразрядной арифметики и блока сдвига, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет добавления функции криптографического преобразования передаваемой информации, оно содержит первый и второй блоки распознавания исходных чисел, элемент ИЛИ, первый и второй дешифраторы переносов, первый и второй блоки формирования исходных чисел, первый, второй и третий блоки коммутации, шифратор переносов и блок формирования результата по ключу, причем первые входы блоков распознавания исходных чисел и блока формирования результата по ключу подключены к третьему входу устройства, вторые входы первого и второго блоков распознавания исходных чисел подключены соответственно к четвертому и пятому входам устройства, первый и втрой входы элемента ИЛИ соответственно к первому и второму входам устройства, входы первого и второго дешифраторов переносов подключены к первым выходам соответственно первого и второго блоков распознавания исходных чисел, первые входы блоков формирования исходных чисел к выходу элемента ИЛИ, вторые входы к выходам соответственно первого и второго дешифраторов переносов, третьи входы к вторым выходам соответственно первого и второго блоков распознавания исходных чисел, первые входы первого и второго блоков коммутации подключены к первому входу устройства, первый вход третьего блока коммутации к второму входу устройства, второй вход первого блока коммутации к выходу первого блока формирования исходных чисел, вторые входы второго и третьего блоков коммутации к выходу второго блока формирования исходных чисел, первый и второй входы блока поразрядной арифметики подключены к выходам соответственно первого и второго блоков коммутации, а входы блока сдвига к выходу третьего блока коммутации, входы шифратора переносов подключены к выходу блока формирования переносов, первый, второй и третий входы блока формирования результата по ключу подключены соответственно к третьему входу устройства, выходам шифратора переноса и выходам группы элементов ИЛИ.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для распознавания сигналов | 1981 |

|

SU1018133A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-11-10—Публикация

1992-03-31—Подача