Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, работающих в системах счисления с большими основаниями.

Известны устройства, в которых связь между разрядами осуществляется цепью распространения переносов.

Известен параллельный комбинационный сумматор, который содержит n полных одноразрядных сумматоров, входы переносов которых подключены к первым входам элементов И переноса, вторые входы которых соединены с дополнительной входной шиной. Выходы элементов И переноса подключены к первым входам элементов ИЛИ переноса, вторые входы которых (за исключением элемента ИЛИ переноса старшего разряда) соединены с выходом элемента И, первый вход которого соединен со входом переноса младшего разряда, а второй - с выходом элемента НЕ. Ко второму входу элемента ИЛИ переноса старшего разряда подключен выход элемента И. Выходы элемента ИЛИ переноса подключены ко входам переносов старших разрядов [1].

Известен параллельный сумматор с одновременным переносом, который содержит блок формирования поразрядных сумм и поразрядных переносов, в состав которого входят четыре элемента образования поразрядных сумм и поразрядных переносов, блок формирования переносов во все разряды, в состав которого входят три элемента формирования переноса в старший и два последующих разряда соответственно, блок формирования результата, в состав которого входят четыре элемента учета переносов [2].

Наиболее близким к изобретению является вычислительное устройство, описанное в работе [3]. Устройство содержит блок поразрядной арифметики, блок сдвига, блок формирования переносов, группу элементов ИЛИ, блок формирования результата, причем первая и вторая группы входов блока поразрядной арифметики, входы блока сдвига, первые группы входов блока формирования переносов и блока формирования результата подключены ко входам устройства, первая и вторая группы входов группы элементов ИЛИ подключены соответственно ко вторым группам выходов блока поразрядной арифметики и группы элементов ИЛИ, вторая и третья группы входов блока формирования результата подключены соответственно к выходам блока формирования переносов и группы элементов ИЛИ.

Недостатком прототипа являются органичные функциональные возможности, поскольку он выполняет только арифметическую операцию сложения и логическую операцию сдвига р-ичного числа на один эквивалентный двоичный разряд вправо.

Целью изобретения является расширение функциональных возможностей устройства за счет добавления функции криптографического преобразования передаваемой информации.

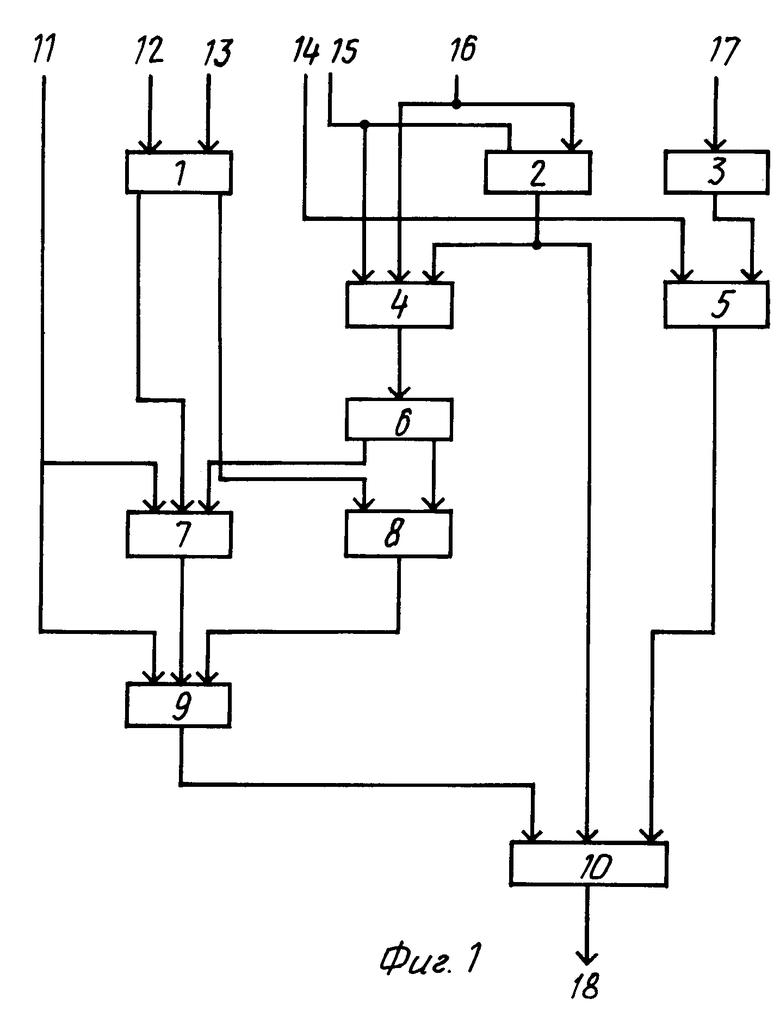

Поставленная цель достигается тем, что вычислительное устройство, содержащее блок поразрядной арифметики, блок сдвига, блок формирования переносов, группу элементов ИЛИ и блок формирования результата, причем первая и вторая группы входов блока поразрядной арифметики подключены соответственно ко второй и третьей группам входов устройства, а первые группы входов блока формирования переносов и блока формирования результата подключены к первой группе входов устройства, первая и вторая группы входов группы элементов ИЛИ подключены соответственно ко вторым группам выходов блока поразрядной арифметики и группы элементов ИЛИ, вторая и третья группы входов блока формирования результата подключены соответственно к выходам блока формирования переносов и группы элементов ИЛИ, содержит блок анализа вариантов сдвига, регистр ключа, первый, второй блоки коммутации и шифратор выходной информации, причем первые и вторые группы входов блока анализа вариантов сдвига и первого блока коммутации подключены соответственно к пятой и шестой группам входов устройства, третья группа входов первого блока коммутации - к выходу блока анализа вариантов сдвига, вход регистра ключей подключен к седьмому входу устройства, первая и вторая группы входов второго блока коммутации соответственно - к четвертой группе входов устройства и выходу регистра ключей, первая, вторая и третья группы входов шифратора выходной информации подключены соответственно к выходам блока формирования результата анализа вариантов сдвига и второго блока коммутации.

Блок-схема предлагаемого вычислительного устройства представлена на фиг. 1. Устройство содержит блок 1 поразрядной арифметики, блок 2 анализа вариантов сдвига, регистр 3 ключа, первый блок 4 коммутации, второй блок 5 коммутации, блок 6 сдвига, блок 7 формирования переносов, группу 8 элементов ИЛИ, блок 9 формирования результата и шифратор 10 выходной информации.

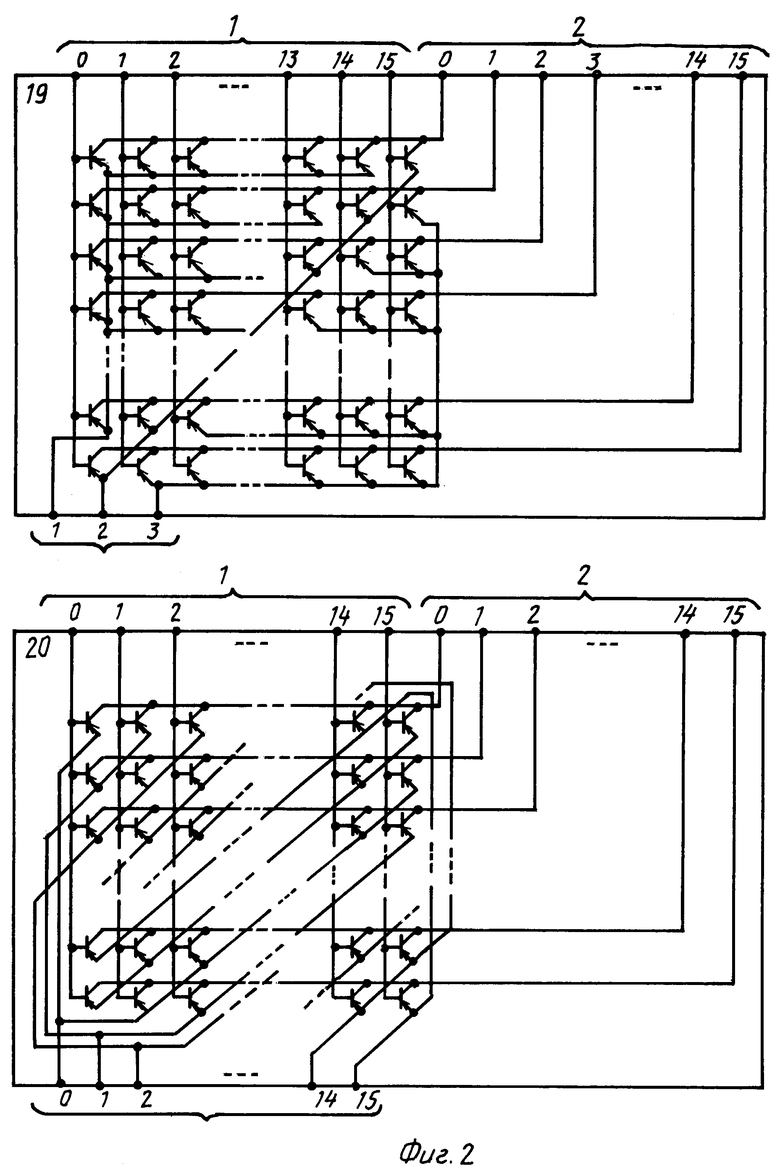

Блок 1 предлагаемого устройства идентичен блоку 1 устройства-прототипа и содержит матрицы 19 переносов в соседний старший разряд при сложении двух р-ичных чисел и матрицы 20 поразрядных сумм, причем первый и второй входы матрицы 19 с порядковым номером i=1,2 и 3 подключены ко входам первой и второй групп блока 1 с порядковым номером i=2,3 и 4 соответственно, а первый и второй входы матрицы 20 с порядковым номером i=1,2,3 и 4 подключены к одноименным входам первой и второй групп блока 1 соответственно. Функциональные схемы матрицы 19 и 20 приведены для примера на фиг. 2 в счислении с основанием р=16.

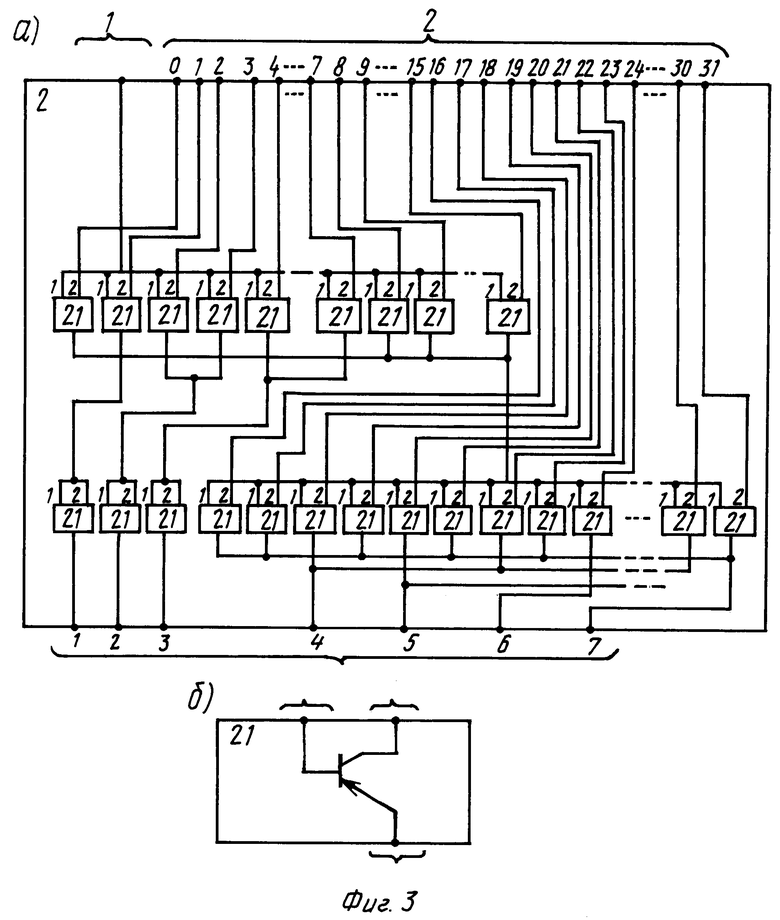

Блок 2 представляет собой комбинационную схему, которая включает две группы двухвходовых элементов (21) И по р двухвходовых элементов И в каждой. При этом первые входы элементов 21 первой группы подключены ко входу 1 блока 2, а вторые входы элементов 21 первой группы с номерами i=0,....,15 подключены ко входам второй группы входов блока 2, номера которых совпадают с номерами подключенных к ним элементов 21. Первые входы элементов 21 второй группы подключены к выходам элементов 21 первой группы с номерами 0,8,. . .,15. Вторые входы элементов 21 второй группы с номерами j=0,...,15 подключены ко входам второй группы входов блока 2 с номерами j+16. Три дополнительных элемента И выполняют функцию элементов задержки и предназначены для согласования во времени появления сигнала на выходах блока 2.

Блок 3 представляет собой регистр, предназначенный для хранения Х2-разрядных двоичных чисел (Х2= npl, где np - разрядность преобразуемых p-ичных чисел и l - число двоичных разрядов, используемое при кодировании цифр в каждом разряде; l > log2p.

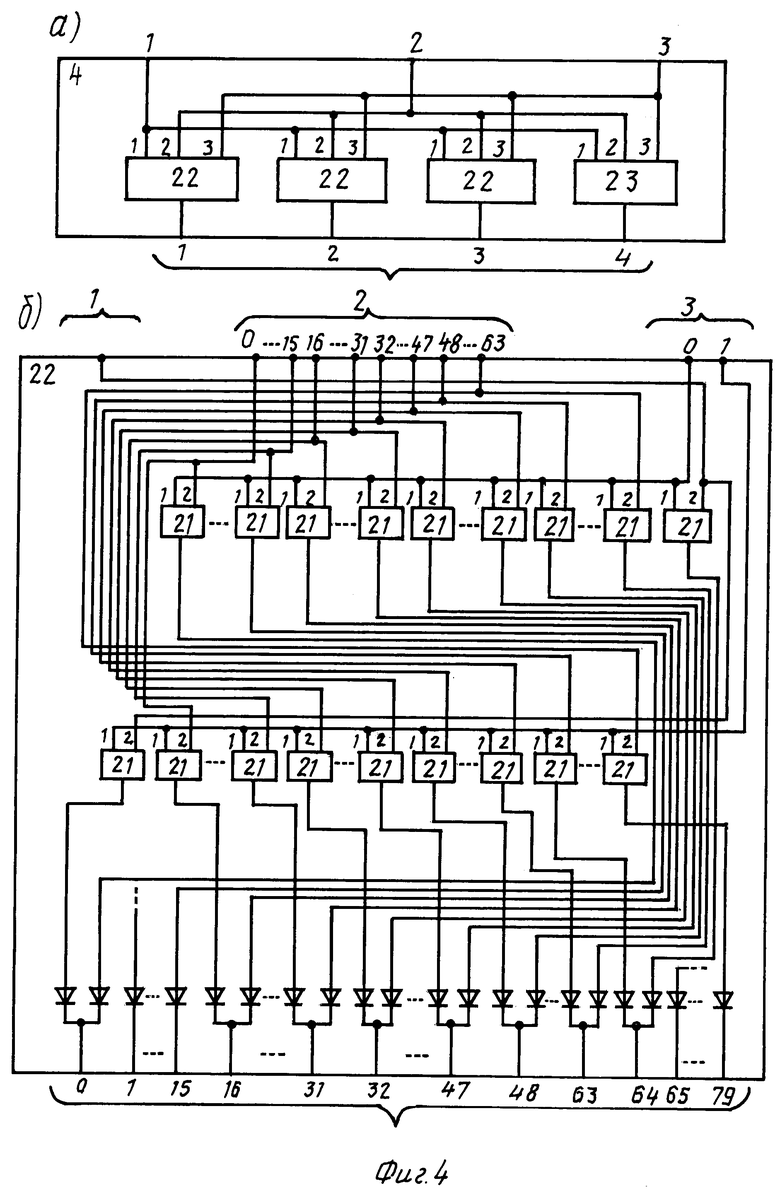

Блок 4 (фиг. 4, а) содержит четыре блока передачи информации. Первый, второй и третий входы каждого из них подключены к одноименным группам входов блока 4. Блок - схема первых трех из этих блоков представлена на фиг. 4, б (блока 22), четвертого - на фиг. 5 (блок 23). При этом блок 22 содержит две группы элементов (21) И на два входа. Входы 1 элементов 21 первой и второй групп подключены соответственно ко входам 0 и 1 третьей группы входов блока 22. Входы 2 элементов 21 первой группы, за исключением последнего, и входы 2 элементов 21 второй группы, за исключением первого, подключены к соответствующим входам второй группы входов блока 22. Вход 2 первого элемента второй группы элементов 21 и вход 2 последнего элемента первой группы элементов 21 подключены ко входу 1 блока 22. Выходы элементов 21 обоих групп через двухвходовые элементы ИЛИ (диодная сборка) в порядке, приведенном на фиг. 4, подключены к выходу блока 22.

Блок 23 (фиг. 5) содержит две группы двухвходовых элементов (21) И. При этом входы 1 элементов 21 первой и второй групп подключены соответственно ко входам 3 и 1 блока 23. Входы 2 элементов 21 первой и второй групп элементов 21 подключены соответственно ко входам второй группы входов блока 23 и выходам элементов 21 первой группы (элементы 21 второй группы выполняют функцию элементов задержки с целью согласования сигналов на выходах блоков 22 и 23).

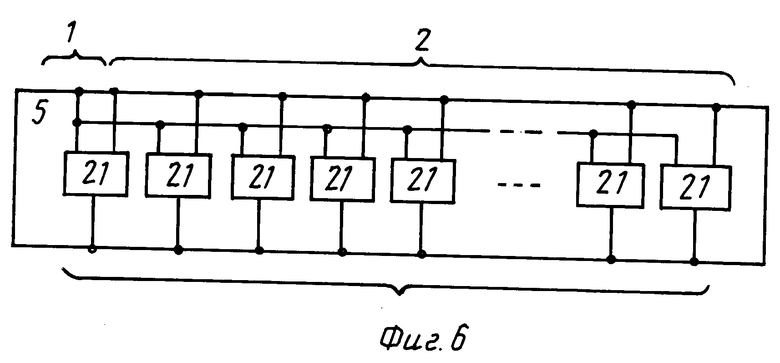

Блок 5 (фиг. 6) представляет собой коммутатор для передачи Х2-разрядных двоичных чисел.

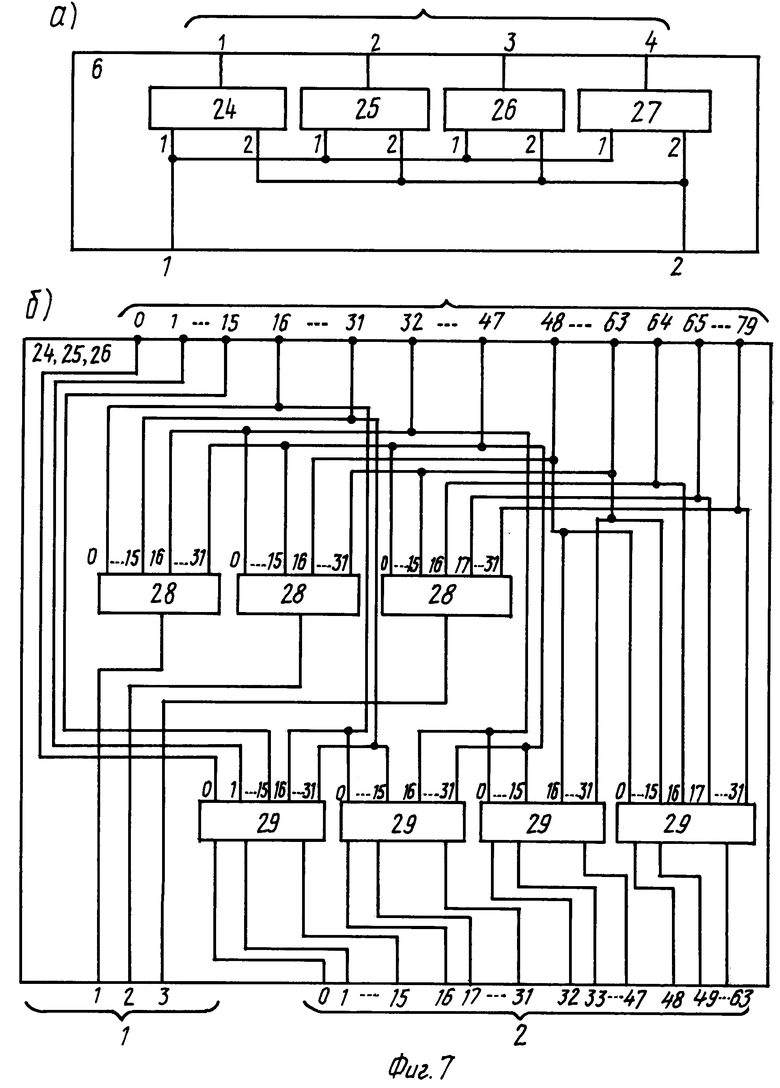

Блок 6 (фиг. 7, а) содержит блоки 24, 25, 26 сдвига передаваемого p-ичного числа соответственно один, два и три эквивалентных двоичных разряда влево (три, два и один эквивалентный двоичный разряд вправо), а также блок 27 элементов задержки цифрового сигнала.

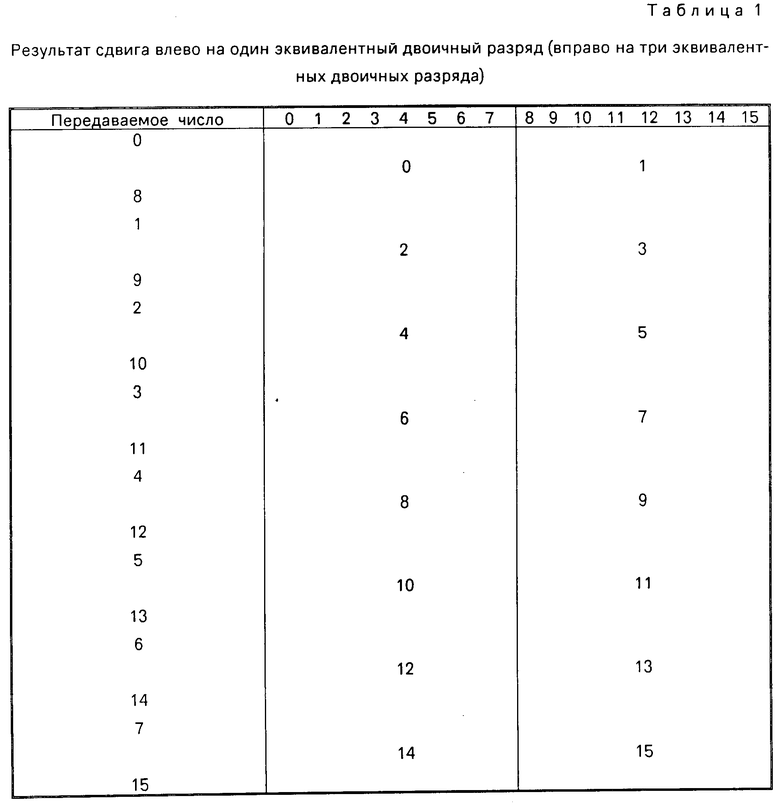

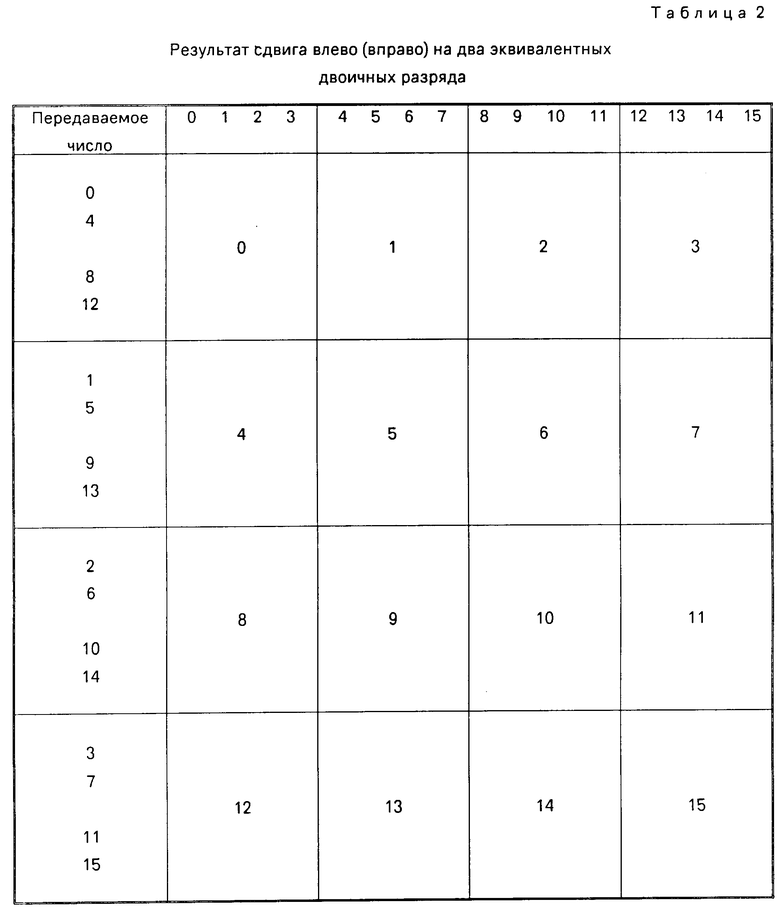

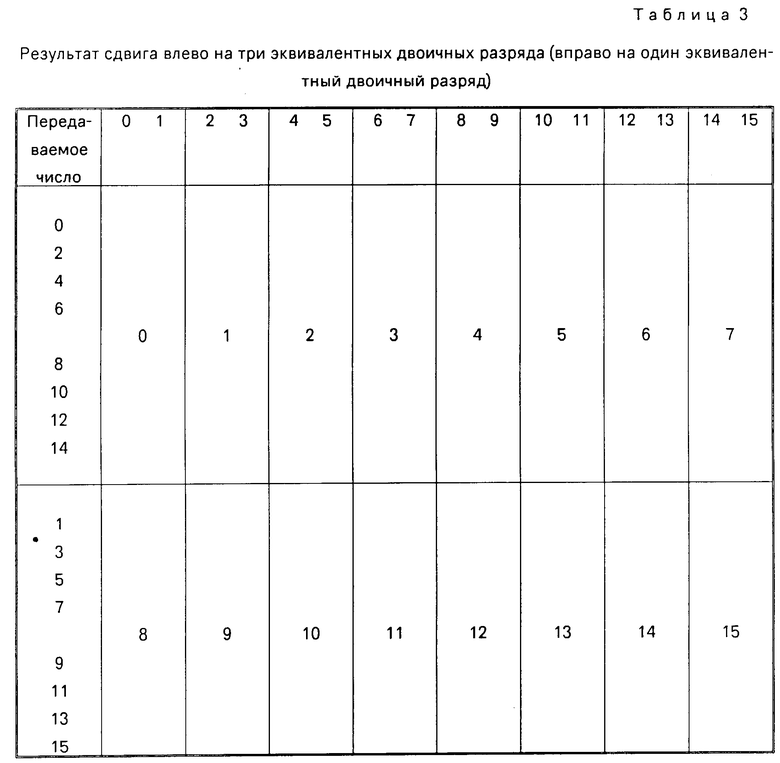

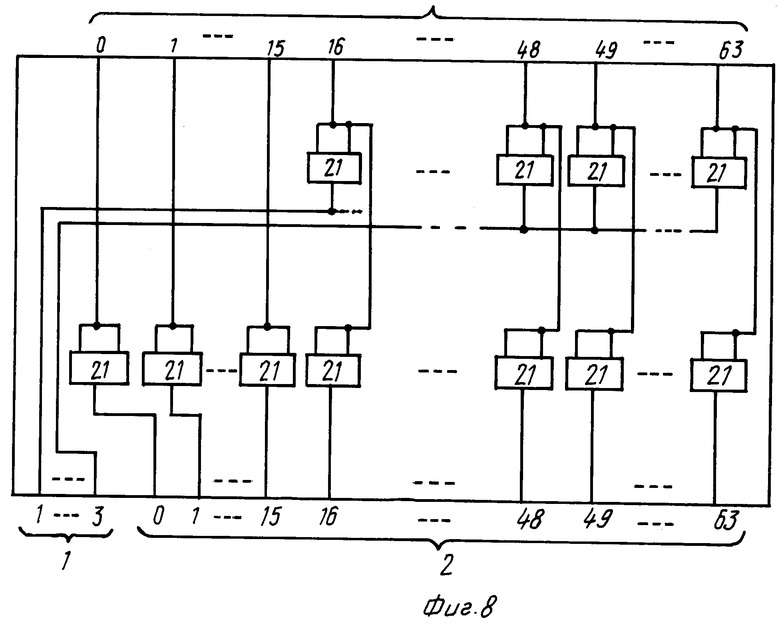

Каждый из блоков - 24, 25 и 26 (фиг. 7, б) содержит блоки 28 памяти переносов нуля в соседний старший разряд при сдвиге передаваемого числа на эквивалентное число двоичных разрядов (в рассматриваемом примере, для p=16 - сдвиг на 1, 2 и 3 эквивалентных двоичных разряда влево или вправо) и блоки 29 эквивалентного двоичного сигнала одного разряда числа. При этом для блоков 24, 25 и 26 каждый из входящих в их состав блоков 29 реализует соответственно табл. 1-3. Выходы 16...31 блока 28 с порядковым номером j=12 объединены с входами 0...15 блока 28 с порядковым номером i+1 соответственно, а входы 16. ..31 блока 29 с порядковым номером j=1,2,3 объединены со входами блока 29 с порядковым номером j+1 соответственно. Блок 27 (фиг. 8) содержит две группы двухвходовых элементов И. При этом выходы элементов 16. . .31; 32....47; 48...63 первой группы объединены в общие выходные шины (по 16 двухвходных элементов И). Элементы второй группы выполняют функцию задержки цифрового сигнала.

Блоки 7, 8, 9 предлагаемого устройства идентичны соответственно блокам 3, 4 и 5 устройства-прототипа (с учетом разрядности устройства и величины p основания используемого счисления).

Блок 10 (фиг. 9) представляет собой матрицу двухвходовых элементов И, включающую np+1 строку. При этом первая строка матрицы содержит 7 групп по 7 двухвходовых элементов И в каждой. Остальные np строк включают 16 групп по 7 двухвходовых элементов И в каждой. Первые входы группы с номером i (i= 0, . . .,6) первой строки подключены к соответствующему входу второй группы входов блока 10. Первые входы группы с номеров j (j=0,...,15) каждой последующей строки (с номером Z=2,...,5) подключены к соответствующим входам первой группы входов блока 10. Вторые входы двухвходовых элементов И всех групп подключены к соответствующим входам третьей группы входов блока 10.

Устройство работает следующим образом.

При выполнении операции сложения исходные числа поступают на входы 12 и 13 устройства и, следовательно, на входы первой и второй групп блока 1 соответственно. При этом числа в каждом разряде представлены в пространственном коде (каждый p-ичный разряд имеет Д позиций и его значение кодируется одним цифровым символом). Одновременно на вход 17 устройства и, следовательно, на вход регистра 3 поступает "ключ" - Х2-разрядное двоичное число, представляющее собой совокупность из p l-разрядных двоичных кодов (различных между собой). Значение цифры в каждом разряде определяется номером позиции, на которой символ в данный момент располагается. С выходов переноса и поразрядной суммы блок 1 (соответственно первая и вторая группы выходов блока 1) значения поразрядных переносов и соседний старший разряд и поразрядных сумм (по модулю р) поступают соответственно на вторую группу входов блока 7 и первую группу входов блока 8. Одновременно на вход 11 устройства и, следовательно, первые входы блоков 7 и 9 поступает управляющий сигнал У1, обеспечивающий прохождение через эти блоки числовой информации. В отмеченном представлении цифр с выходов переноса блока 1 обязательно поступает либо значение переноса "1", либо значение переноса "0". С выходов блоков 7 и 8 значения переносов и поразрядных сумм поступают на входы второй и третьей групп входов блока 9 соответственно. При этом на выходе блока 9 результат в каждом разряде появляется только в том случае, если он безошибочен. Одновременно с появлением информации на выходе блока 9 числовой код "ключ" проходит через коммутатор 5 в результате подачи на его первый вход управляющего сигнала У2. При этом на первый и третий входы блока 10 одновременно поступают как результат сложения пары чисел, так и числовой код "ключа". В результате на выходе блока 10 и, следовательно, выходе 18 устройства появится закодированное значение результата.

Более значительные возможности в плане криптографического преобразования числовой информации схема представляет в случае подачи передаваемого в канал связи числа на вход 16 устройства. Одновременно с ним на вход 15 устройства подается управляющий сигнал У3, который при этом поступает на первые входы блоков 2 и 4. На вторую группу входов блока 2 поступают цифры старшего разряда передаваемого числа и младшего разряда передаваемого числа. При этом на выходе блока 2 появляется информация о возможности масштабирования передаваемого числа за счет сдвига его на 3, 2, 1 эквивалентных двоичных разряда влево (сигнал появляется соответственно на выходах 1, 2, 3 блока 2; см фиг. 3, а) или вправо (сигнал появляется соответственно на выходах 6, 5, 4). В случае отсутствия возможности сдвига числа на эквивалентное число двоичных разрядов влево или вправо на выходе 7 блока 2 появляется информация - цифровой сигнал, наличие которого обусловлено необходимостью передачи числа без внесения масштаба. Пример такой ситуации применительно к случаю сдвига влево - наличие в наиболее значимом разряде 16-ричного числа цифры f, удовлетворяющей условию f≥8. Для сдвига вправо - наличие в младшем разряде нечетной цифры.

Сигналы, предоставляют информацию о наличии (отсутствии) возможности масштабирования передаваемого р-ичного числа за счет сдвига его на один, два, три эквивалентных двоичных разряда влево или вправо с выхода блока 2 поступают на третий вход блока 4. На первый и второй входы блока 4 поступают управляющий сигнал У3 от входа 16 устройства и np-разрядное р-ичное число от входа 16 соответственно.

С выхода блока 4 информация поступает на вход блока 6, исполнительные схемы которого выполняют масштабирование числа за счет его сдвига на один, два, три эквивалентных двоичных разряда вправо (влево) или передают число на выход блока без сдвига в зависимости от результата анализа, выполненного блоком 2. С первой группы выходов блока 6 на входы третьей группы блока 7 поступают сигналы переноса нулей из разрядов с порядковыми номерами 2, 3 и 4 в разряды с порядковыми номерами 1, 2 и 3 соответственно. Одновременно со второй группы выходов блока 6 значения результата сдвига в каждом разряде поступают на входы второй группы блока 8.

Окончательное значение результата сдвига получается на выходе блока 9. При этом в каждом разряде результат появляется на выходе блока 9 только в том случае, если он правильный, т.е. если он представлен на одной позиции данного разряда. Результат преобразования числа с выхода блока 9 поступает на первую группу входов блока 10. На одну из 7 шин второй группы входов блока 10 в этом случае поступает цифровой сигнал, наличие которого соответствует информации о выполненном преобразовании числа, либо передаче его без сдвига. На третью группу входов так же как и в предыдущем случае поступает числовой "ключ". На выходе блока 10 и, следовательно, выходе 18 устройства появляется закодированное число.

Таким образом, введение блока анализа вариантов сдвига, регистра ключа, первого и второго блоков коммутации и шифратора выходной информации позволяет увеличить функциональные возможности предложенного вычислительного устройства за счет добавления функции криптографического преобразования передаваемой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2047896C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Устройство для умножения | 1981 |

|

SU974370A1 |

| Арифметическое устройство | 1975 |

|

SU577526A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| ТРЕХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ ГЕНЕРАТОР | 1988 |

|

SU1568771A1 |

| Устройство для вычисления порядковых статистик последовательности двоичных чисел | 1988 |

|

SU1509936A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, работающих в системах счисления с большими основаниями. Устройство содержит блок поразрядной арифметики, блок анализа вариантов сдвига, регистр ключа, первый блок коммутации, второй блок коммутации, блок сдвига, блок формирования переносов, группу элементов ИЛИ, блок формирования результата и шифратор выходной информации. Введение блока анализа вариантов сдвига, регистра ключа, первого и второго блоков коммутации и шифратора выходной информации позволяет увеличить функциональные возможности предложенного вычислительного устройства за счет добавления функции криптографирования преобразования передаваемой информации. 9 ил., 3 табл.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок поразрядной арифметики, блок сдвига, блок формирования переносов, группу элементов ИЛИ и блок формирования результата, причем первая и вторая группы входов блока поразрядной арифметики подключены соответственно к второй и третьей группам входов устройства, а первые группы входов блока формирования переносов и блока формирования результата подключены к первой группе входов устройства, первая и вторая группы входов группы элементов ИЛИ подключены соответственно к вторым группам выходов блока поразрядной арифметики и группы элементов ИЛИ, вторая и третья группы входов блока формирования результата подключены соответственно к выходам блока формирования переносов и группы элементов ИЛИ, отличающееся тем, что устройство содержит блок анализа вариантов сдвига, регистр ключей, первый и второй блоки коммутации и шифратор выходной информации, причем первые и вторые группы входов блока анализа вариантов сдвига и первого блока коммутации подключены соответственно к пятой и шестой группам входов устройства, третья группа входов первого блока коммутации - к выходу блока анализа вариантов сдвига, вход регистра ключей - к седьмому входу устройства, первая и вторая группы входов второго блока коммутации - соответственно к четвертой группе входов устройства и выходу регистра ключей, первая - третья группы входов шифратора выходной информации подключены соответственно к выходам блока формирования результата, блока анализа вариантов сдвига и второго блока коммутации.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-03-10—Публикация

1991-07-01—Подача