1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, работающих как в поЗИ1Д1ОННЫХ системах счисления, так и в непозиционных системах остаточных классов.

Известно устройство для выполнения арифметических и логических операций. Это устройство содержит прямоугольную матрицу из логических ячеек и управляющих ячеек - по одной на каждом из столбцов матрицы. Каждая управляющая ячейка состоит из двух каскадов, может находиться в состоянии 1 либо О и служит для управления всеми операциями, выполняемыми соответствующим столбцом. Каждая ячейка матрицы, также состоящая из двух каскадов, связана с соответствующей управляющей ячейкой и вырабатывает выходные сигналы в зависимости от трех входных сигналов. Каждый столбец матрицы может быть выбран с целью выполнения соответствующей арифметической или логической операции.

Известно также устройство, которое предназначено для сложения, вычитания, умножения, деления, возведе1шя в степень, извлечения корня и перекодлрования многоразрядных двоичных чисел.

Устройство содержит блоки сложе}шя и вычитания с шунтирующим управлением. Каждый блок имеет два входа операндов, вход переноса (занятия еданицы из десятка при вычитании), а также выход суммы или разности.

Все эти устройства выполняют ограниченный набор операций. Кроме того, они не позволяют строить вычнс1штель1 ые машины, которые могут работать как в позиционной системе счисления, так и в инерционной системе счисления остаточных классов.

Наиболее близким к изобретению по своей технической сущности является матричное вычислительное устройство, содержащее блоки расстановки операндов и сравнения операндов, входы которых подключены к двум входам устройства, и матрицу памяти. Это устройство имеет большое количество аппаратуры, что вызывает больише затраты, значительную часть которых составляет мафица памяти, содержащая Р(Р-1)/2. двухвходовых элементов И при основании системы

СЧИСЛСШ1Я Р.

Целью изобретения является сокращение оборудования устройства.

Достигается это тем, что устройство содержит блоки распознавания, коммутации, формирования

управляю.чщх СИГНШ10В, вторичной расстановки оиерандон и определения совпадения входных сигналов, причем вход первого блока раснознаваиия подключен к выходу блока расстановки опершщов, первый и второй первого блока коммутации подключены соответственно к выходам блока расстановки операндов и первого блока распознавания, входы второго и третьего блоков распознавания подключены соответственно к первому и второму выходам первого блока коммутации, первый и второй входы второго блока коммутации соединены соответственно с первым выходом первого блока коммутации и первым выходом блока формирования управляющих сигналов, входы которого соединены соответственно с выходами второго и третьего блоков распознавания, первые входы блока вторичной расстановки операндов и блока определения совпадения входных сигналов соединены с вторым выходом первого блока коммутации, вторые входы - с выходом второго блока Коммутации; выход блока вторичной расстановки операндов через матрицу памяти соединен с первым входом третьего блока коммутации, второй и третий входы которого подключены соответственно к выходу блока определения совпадения входных сигналов и к второму выходу блока формирования управляющих сигналов, первый и второй входы четвертого блока коммутации подключены соответственно к выходам т}: етьего блока коммутации и первого блока распознавания, выходы четвертого блока коммутации и блока сравнения операндов сс-единены с соответствующими выходами устройства.

Блоки распознавания и блок формирования управляющих сигналов вырабатывают управляющие сигналы в зависимости от того, к какой из частей таблицы, отображаемой матрицей памяти, осуществляется обращение; блоки коммутации необходамы для подключения входов и выходов матрицы памяти к входам и выходам матричного вычислительного устройства соотвотственло по сигналам, вырабатываемым блоками распознавания и блоком формирования управляющих сигналов; блок вторичной расстановки операндов и блок совпаденля входных сигналов необходимы 11ля исключения избыточных элементов матрицы памяти. Это позволяет использовать каждый днухвходовый элемент И матрицы памяти для определения группы н общем случае различных значений.

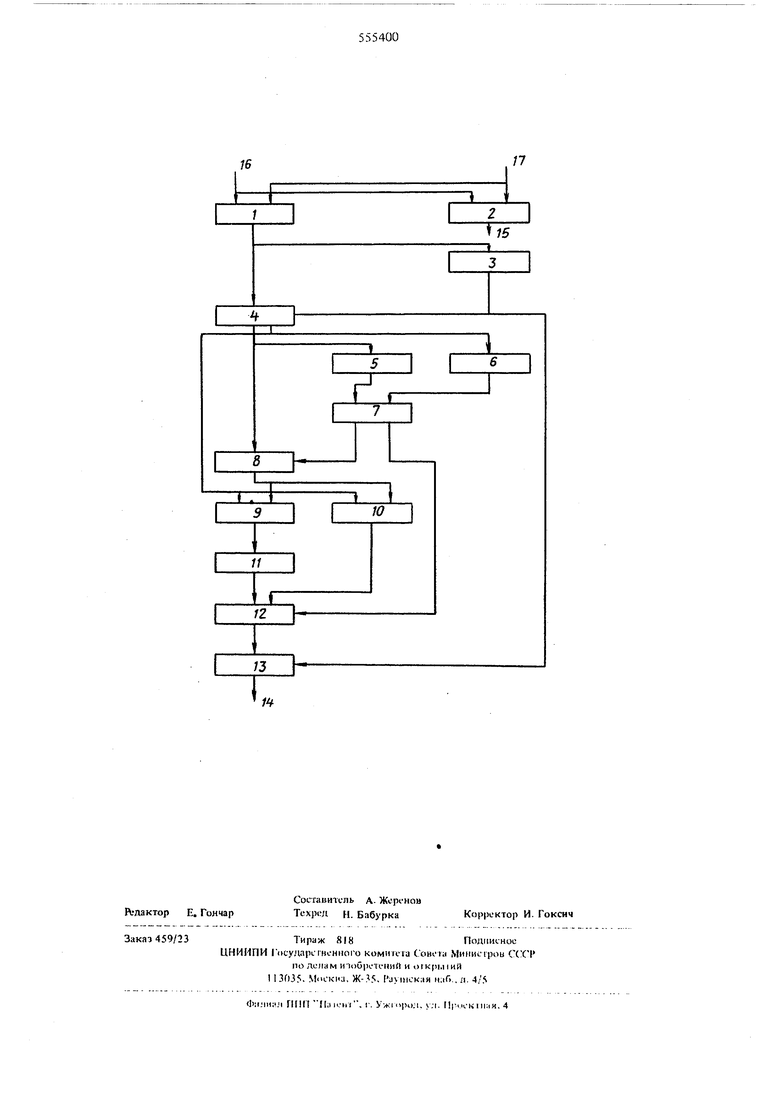

На чертеже представлена блок-схема матричного вычислительно о устройства.

Предлагаемая блок-схема содержит блок 1 расстановки операндов, блок 2 сраннения операндов, блок 3 распознавапия, блок 4 коммутации, блоки 5, 6 распознавания, блок 7 формирования управляющих сигиилов, блок 8 коммутации, блок 9 вторичной расстановки операндов, блок 10 определони}; совпадения входных сиг-} алов. матрица I I памяти, блоки 12 п 13 коммугацяи, В1)ходь 14, 15 и входы 6, 17 устройства.

Блок 3 имеет число входов, равное выбранному основанию системы счисления, и реализуется с помощью элементов И, ИЛИ.

Блок 4 представляет собой матрицу элементов

И и содержит число вертикальных щин, равное выбращюму основанию, и две горизонтальные щины. Входы элементов И, расположенных в одной строке ( в одном столбце), подключены соответственно к одной горизонтальной (вертикальной

шине). Блоки 5, 7 реализуются с использованием элементов И, ИЛИ. Блок 6 представляет собой многовходовую схему ИЛИ. Блок 8 представляет собой матрицу элементов И, горизонтальные щины которой подключены соответственно к выходам

блока 7, а вертикальными щинами блока 8 являются те же выходы блока 4, которые являются входными для блока 5.

Блок 9 представляет собой набор двухвходовых элементов ИЛИ, блок 10 - набор двухвходовых элементов И.

Блок 12 представляет собой матрицу элементов И, вертикальные щины которой подсоединены к выходам матрицы 11 и блока 10, а горизонтальные П11ШЫ подсоединены соответственно к выходам

блока.

Блок 13 представляет собой матрицу элементов И, вертикальные щины которой подсоедщюны к выходам блока 12, а горизонтальные - к выходам блока 3.

Матричное вычислительное устройство работает

следуюндим образом. Операнды с входов 16, 17 устройства поступают па входы блоков 1 и 2. Если операнды равны, то сигнал поступает на выход 15 устройства но выходу блока 2, номер которого

равен величине любого из операндов.

Если операнды не равны, то в блоке 1 возбуждаются дна выхода, номера которых совпадают с величинами операпдов соответственно. Сигналы поступают на входы блоков 3, 4. В блоке 3 вырабатывается управляющий сигнал на одном из выходов, в блоке 4 осун1ествляется нередача каждого из двух сигначов, к одному из двух выходов, в зависимости от того, на какой из управляющих входов поступает сигнал от блока 3.

Для четн(лх (нечетных) значений основания с

выходов 4 сигналы, соотнетстиующие операндам, поступают на одноименные иходы блоков 5, 8 или на соогве1ствующие входы блоков 6,9, 10. С выходов блоков 5 и 6 cHrnajnii поступают на

вход блока 7, которьпТ вырабатывает упраиляющие сигналы на соотпетствуюнгнх выходах.

В блоке 8 осуществляется перод; ча сигналов, 1юступаюп1их от любого из выходов блока 4 к одному из длух выходов, в зависимости от того, на

какой из управляющих входов поступает сигнал из блока 7.

С выходои блока Н сигналы поступают на соответствую1Н1 о входы блоков 9 и 10.

Выходные сигналы блока 9 noc-iyiiaioi на входы

м;,т1)1;цы 11, пыходпыс сигналы которо и блока 10

поступают на вход блока 12. Одновременно по Одному из управляющих входов блока 12 поступает сигнал с выхода блока 7. С выхода блока 12 сигнал поступает на вход блока j 3.

Одновременно по одному из управляющих входов блока 13 поступает сигнал с соответствующего выхода блока 3. При этом, на выходе блока 13 появляется сигнал, соответствующий результату операции. Минимальный положительный эффект от внедрения изобретения по сравнению с

известным устройством наблюдается при основании больщем 30. Экономический эффект от внедрения устройства тем больше, чем больше величина основания.

Формула изобретения

Матричное вычислительное устройство, содержащее блоки расстановки операндов и сравнения операндов, входы которых подключены к двух входам устройства, и матрицу памяти, отличающееся тем, что, с целью сокращения оборудования, оно содержит блоки распознавания, коммутации, формирования управляющих сигналов, вторичной расстановки операндов и определения совпадения входных сигналов, причем вход первого блока распознавания подключен к выходу блока

расстановки операндов, первый и второй входы, первого блока коммутащ1и подключень соответственно к выходам блока расстановки операндов и первого блока распознавания, входы второго и третьего блоков распознавания подключены соответственно к первому и второму выходам первого блока коммутации, первый и второй входы второго блока коммутации соединены соответственно с первым выходом первого блока коммутации и первым выходом блока формирования управляюОщих сигналов, входы которого соединены соответственно с выходами второго и третьего блоков распознавания, первые входы вторичной расстановки операндов и блока определения совпадения входных сигналов соединены с вторым выходом

16 первого блока коммутации, вторые входы - с выходом второго блока коммутации, выход блока вторичной расстановки операндов через матрицу памяти соединен с первым входом третьего блока коммутации, второй и третий входы которого

0 подключены соответственно к выходу блока определения совпадения входных сигналов и к второму выходу блока формирования управляющих сигналов , первый и второй входы четвертого блока коммутации подключены соответственно к выходам третьего блока коммутации и первого блока распознавания, выходы четвертого блока коммутации и блока сравнения операндов соединены с соответствующими выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Матричный сумматор-умножитель | 1978 |

|

SU767759A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Матричное устройство для сложения | 1979 |

|

SU883896A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИТУАЦИЙ | 2000 |

|

RU2195703C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

Авторы

Даты

1977-04-25—Публикация

1975-06-09—Подача