...1

Изобретение относится к области вычислительной техники и может быть использовано в цифрсдаых вычислительных машинах, работающих как в позиционных системах счисления, так и в непозицирнных системах остаточных классов.

Известен матричный сумматор - умножитель, в котором операнды поступают на входы матрицы конъюнктивных эпемен тов в таком же порядке, в котором они . поступают на входы данного устройства, т. ё. независимо от того, какой из операндов больше и какой меньше.

Известное устройство содержит три матрицы логических элементов И и две группы элементов ИЛ И, выходы элементов И каждой матрицы, формируемых одну и ту же функцию, объединены в одну выходную шину матрицы, входы элементов И, расположенных в одной Строке и в одном столбце матрицы, подсоединены соответственно к одной горизонтальной и одной вертикальной входной шине

матрицы, вертикальные и горизонтальные входные шины первой матрицы элементов И подсоединены соответственно к выход- ным шинам второй и третьей матриц адементов И fl |.

Известен также матричный сумматорумножитель, содержащий конъюнктивные

, элементы групп сложения и умножения

, 1-го числа, конъюнктивные элементы групп сложения и умножения 2-го числа,

10 группы дизъюнктивных элементов 1-го и 2-го числа, матрицу конъюнктивных элементов, выходную группу конъюнктивных и дизъюнктивных элементов, причем каждая йз входных шин матрицы соеди15нена группу дизъюнктивных элемен тов 1-го и 2-го числа и через конъюнктивные элементы групп сложения и умножения с родами 1-го или 2-го числа

.сумматора-умножителя; выходы матрицы

20 подключены к входам группы конъюнктивных и дизъюнктивных элементов, с которой непосредственно соединены также нулевые входы 1-го и 2-го числа, конъюнктивные элементы групп сложения 1-го и 2-го числа соединены с шиной сигнала сложения, а конъюнктивные элементы группы умножения 1-го и 2-го числа - с шиной сигнала умножения, шины сигналов сложения и умножения соединены гак же с выходной группой конъюнктивных и

дизъюнктивны С элементов 2|.

К недостаткам известных устройств

lj, 2 j относятся значительный расход оборудования и ограниченные функциональные возможности - ограниченное число выполняемых операций.

Наиболее близким по технической сущности -к изобретению является матричный сумматор-умножитель, содержащий блок расстановки операндов, блок равенства операндов, матрицу элементов И, блок элементов ИЛИ операции сложения, блок элементов ИЛИ операции умножения. Входные шины блока расстановки операндов и блока равенства операндов являются входными шинами устройства. Выходы блока расстановки операндов соединены со входами матрицы элементов И, выходы блока равенства операндов и матрицы элементов И - со входами блока элементов ИЛИ сложения и блока элементов ИЛИ умножения З.

Недостатком этого матричного сумматора-умножителя является то, что набор выполняемых им операций ограничивается арифметическими операциями сложения и умножения. Это исключает возможность использовать известное устройство для выполнения функции контроля ошибки,в каждом из операндов...

Цель изобретения - расширение функциональных возможностей устройства путем введения операции контроля вход- .ных операндов.

Поставленная цель достигается тем, что в матричный сумматор-умножитель, содержащий блок расстановки операндов, .блок равенства операндов, матрицу элементов И, причем выходы блока расстановки операндов соединены со входами матрицы элементов И, введены первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый и пятый блоки коммутации. При этом первый управляющий вход сумматора-умножителя соединен с первыми входами первого и второго элементов ИЛИ, второй управляющий вход сумматора-умножителя - со вторым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ третий управляющий вход сумматора- гмножителя - со вторыми входами второго и третьего элементов ИЛИ, выходы которых подключены соответственно к уп. равляющим входам первого, и второго блоков коммутации. Информационные входы первого и второго блоков коммутации являются соответственно входами операн. тов сумматора-умножителя. Выходы первого блока коммутации соединены с первыми

Q группами входов блоков расстановки операндов и равенства операндов, выходы второго блока коммутации - со вторыми группами входов блоков расстановки операндов и равенства операндов, а выходы

J блока равенства операндов - с первыми входами третьего и четвертого блоков коммутации. Выходы матрицы элементов И подключены к вторым входам третьего и четвёртого блоков коммутации и к

0 первому входу пятого блока коммутации. Третий управляющий вход сумматора-умножителя соединен с управляющими входами третьего и четвертого блоков ком- . мутации, выход первого элемента ИЛИ

5 связан с управляющим вход1ом пятого блока коммутации, выходы третьего, четвертого и пятого блоков коммутации являются соответственно выходами результатов умножения, сложения и койтрсотя сум0 матора-умножителя...

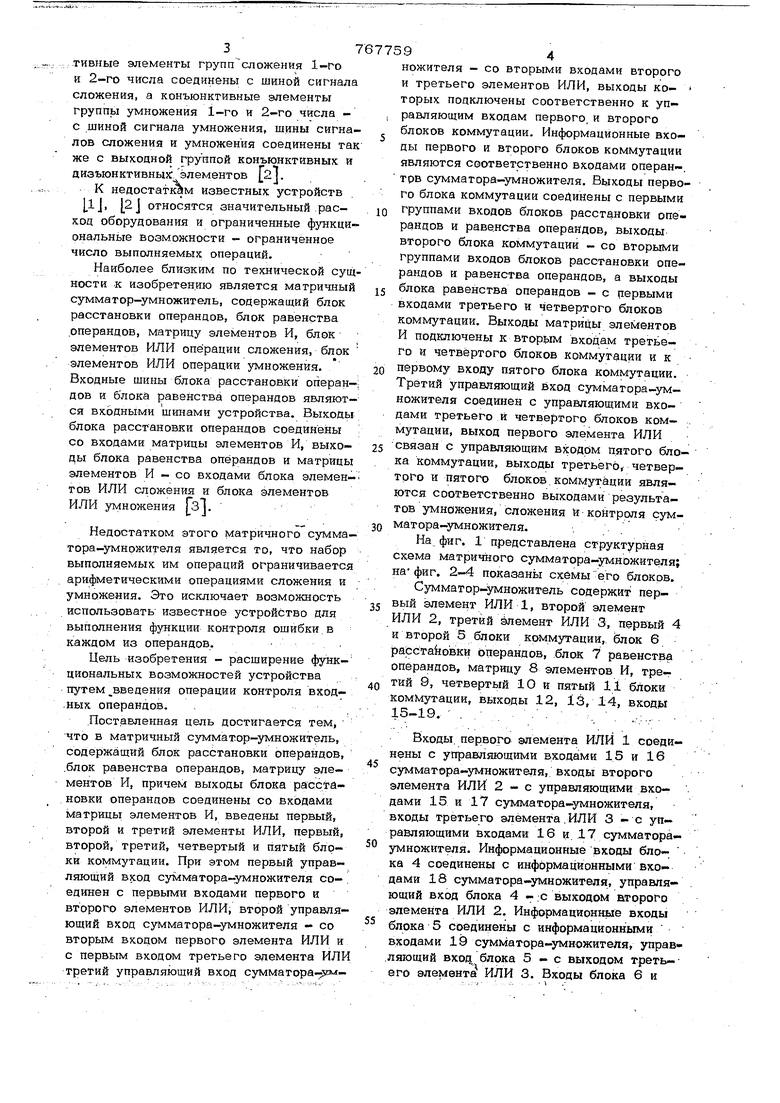

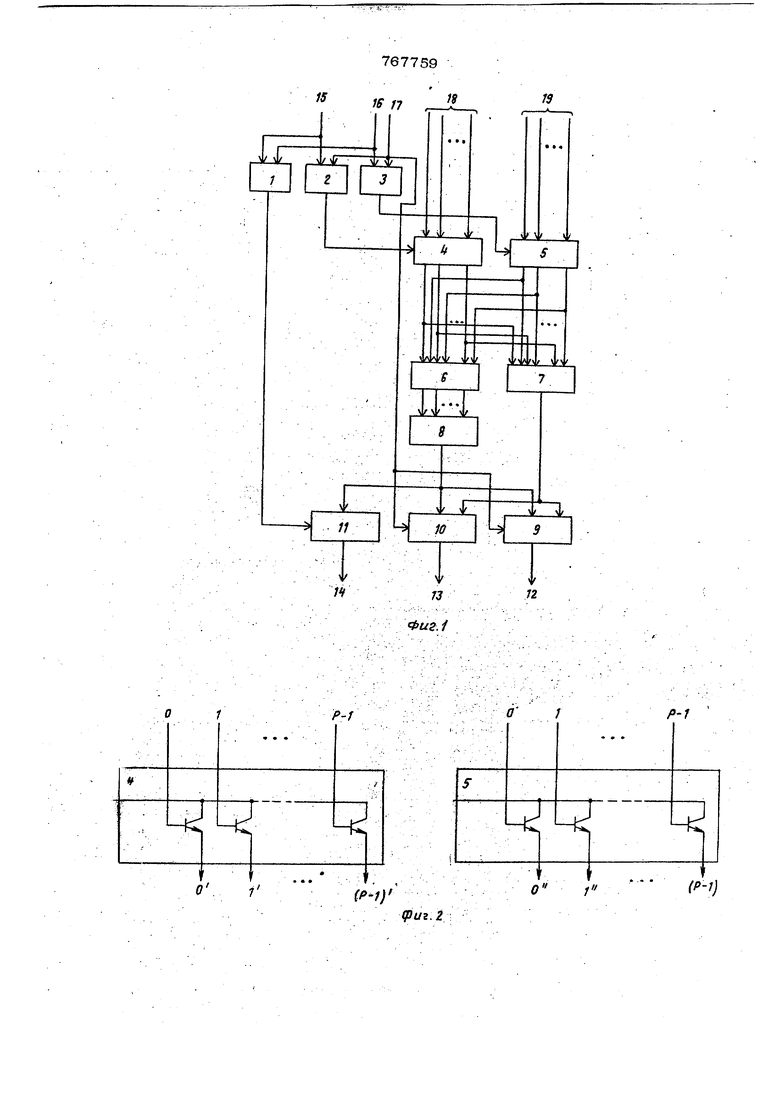

На фиг. 1 представлена структурная схема матрич аого сумматора-умножителя; на- фиг. 2-4 показаны схемы его блоков. Сумматор-умножитель содержит пер5 вь1й элемент ИЛИ 1, второй элемент

ИЛИ 2, третий Элемент ИЛИ 3, первый 4 и второй 5 блоки коммутации, ёлок 6 paccTakoJBKH операндов, блок 7 равенства операндов, матрицу 8 элементов И, третий 9, четвертый 10 и пятый 11 блоки коммутации, выходы 12, 13, 14, 15-19. ...... ..:.. . .

бходы. первого элемента ИЛИ 1 соединены с управляющими входами 15 и 16 сумматора-умножителя, входы второго элемента ИЛИ 2-е управляющими вхо- дами 15 и 17 сумматора-умножителя, входы третьего элемента.ИЛИ 3-е управляющими входами 16 и. 17 сумматора-

умножителя. Информационные входы блока 4 соединены с информационными входами 18 сумматора-умножителя, управляющий вход блока 4 - :с выходом второго элемента ИЛИ 2. Информационные входы

блока 5 соединены с информационными

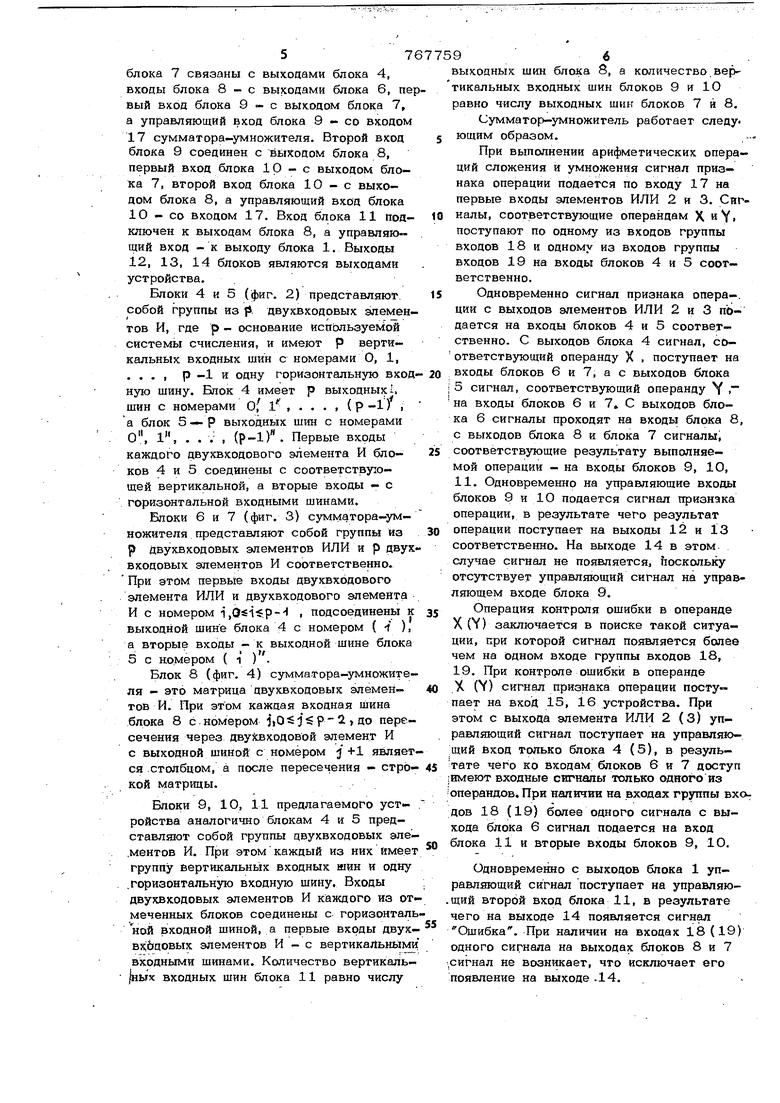

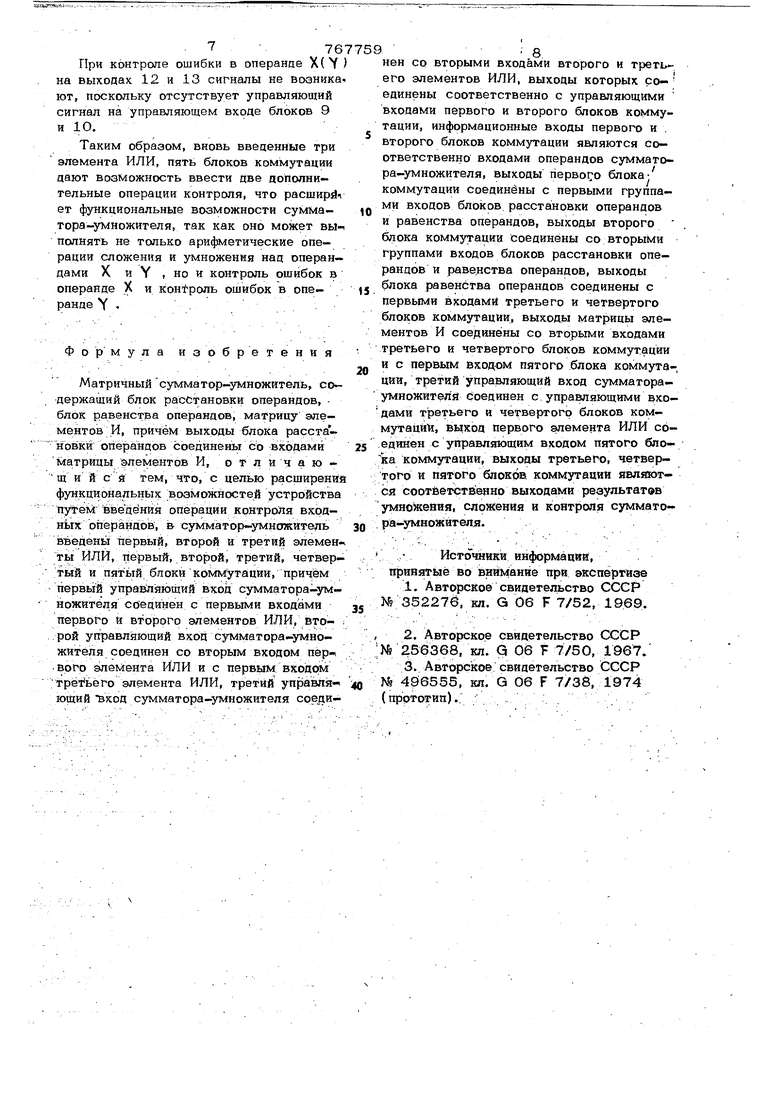

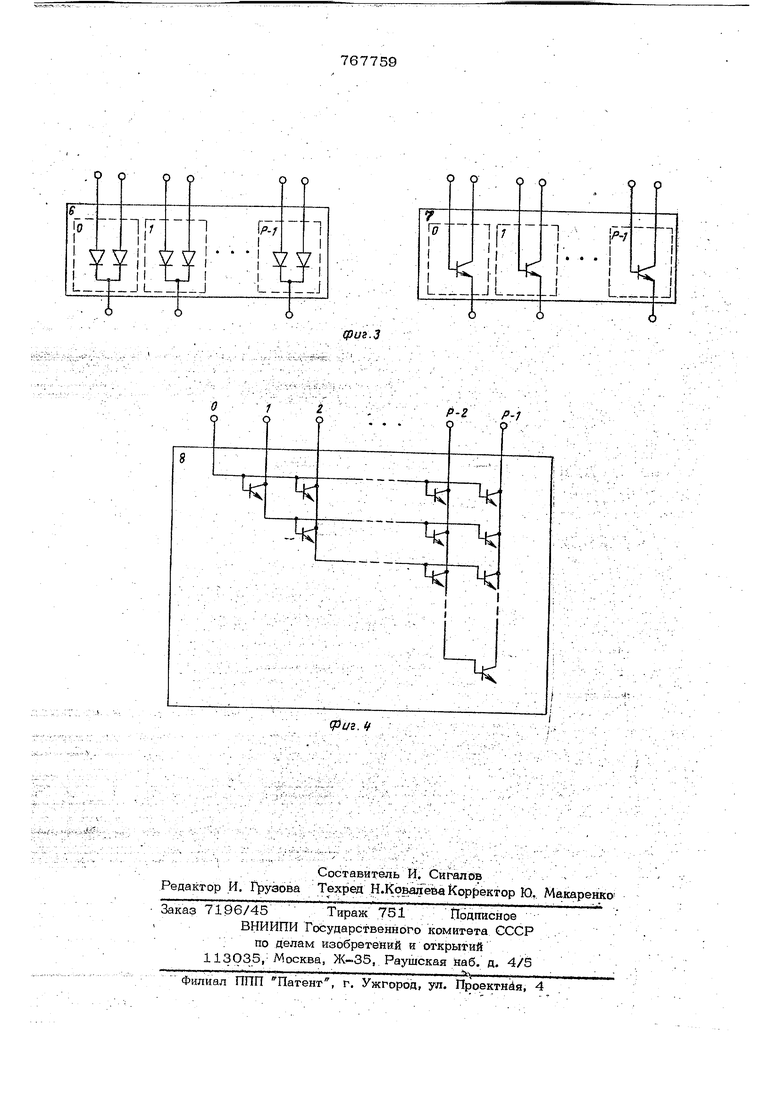

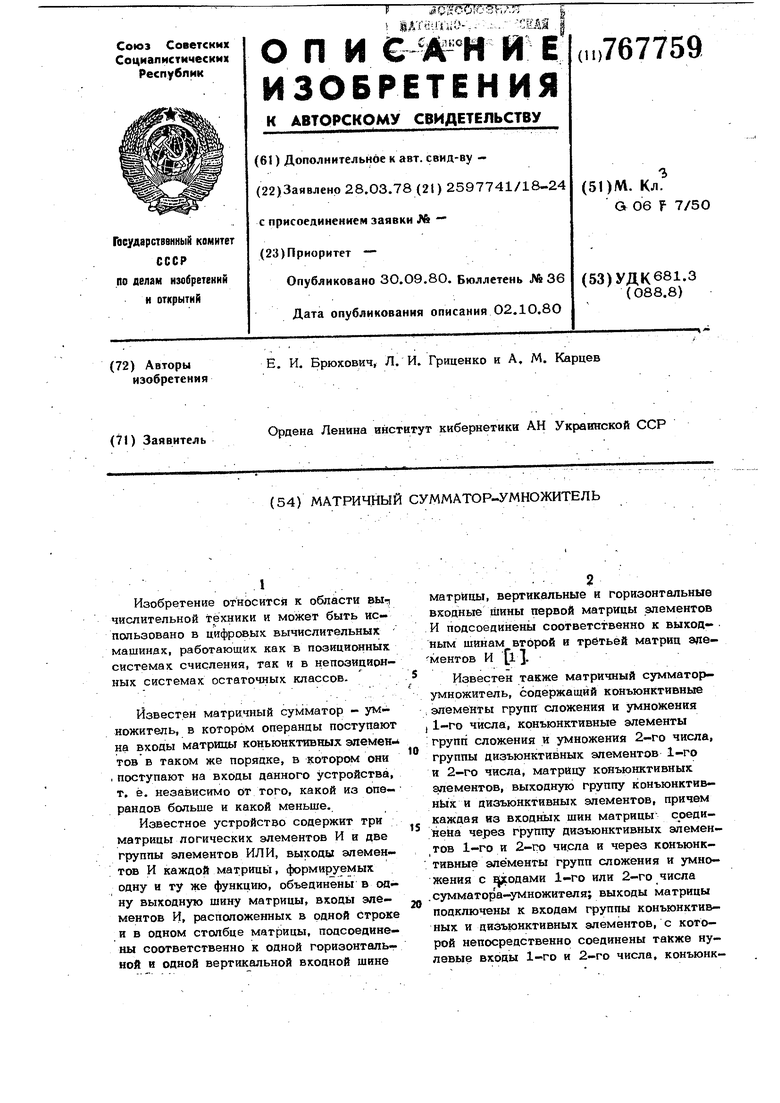

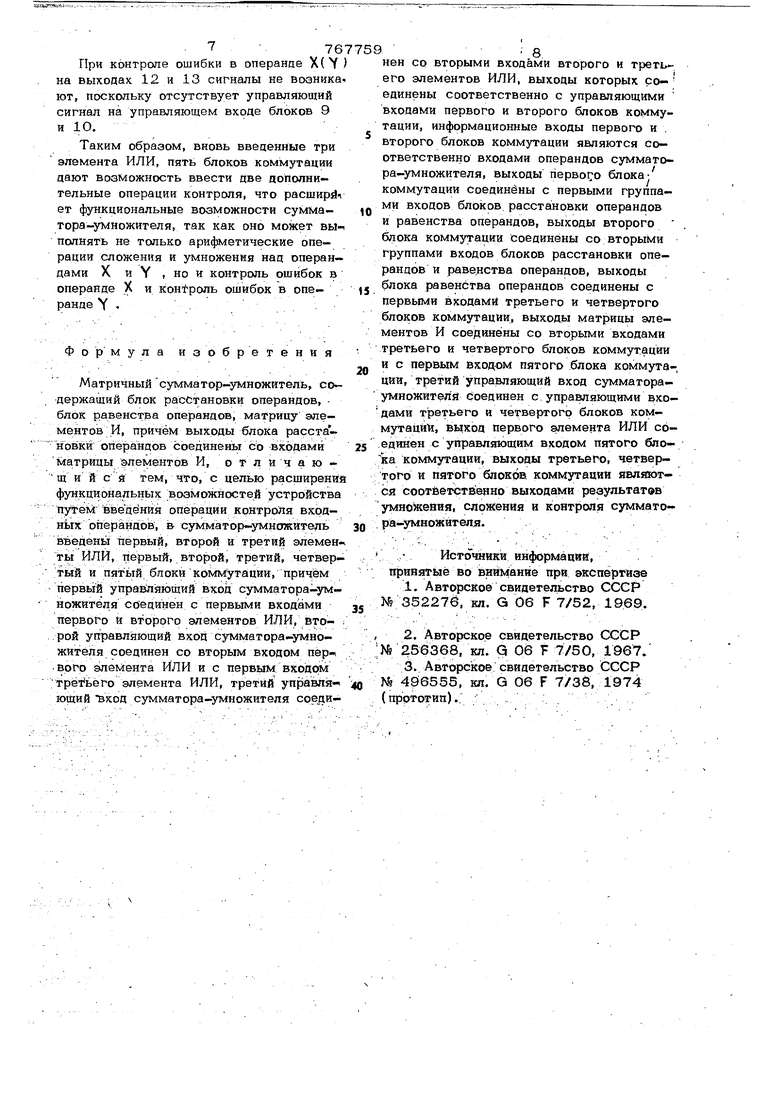

входами 19 сумматора-умножителя, управ.ляющий вход блока 5 - с выходом треть-его элемента ИЛИ 3. Входы блока 6 и 57 блока 7 связаны с выходами блока 4, входы блока 8-0 выходами блока б, пе вый вход блока 9 - с выходом блока 7, а управляющий вход блока 9 - со входом 17 сумматора-умножителя. Второй вход блока 9 соединен с выходом блока 8, первый вход блока 10 - с выходом блока 7, второй вход блока 10 - с выходом блока 8, а управляющий вход блока 10 - со входом 17. Вход блока 11 подключен к выходам блока 8, а управляю- щий вход - к выходу блока 1. Выходы 12, 13, 14 блоков являются выходами устройства. Блоки 4 и 5 (фиг. 2) представляют собой группы из р. двухвходрвых элементов И, где р - основание используемой системы счисления, и имеют р вертикальных входных шин с номерами О, 1, р -1 и одну горизонтальную вход ную шину. Блок 4 имеет р выходных шин с номерами 0, l ,...,( Р -17 , а блок 5 - Р выходных шин с номерами о, 1, . . V , (P-I). Первые входы каждого двухвходового элемента И блоков 4 и 5 соединены с соответствующей вертикальной, а вторые входы - с горизонтальной входными шинами. Блоки 6 и 7 (фиг. 3) сумматора-умножителя представляют собой группы из р двухвходовых элементов ИЛИ и р двух входовых элементов И соответственно. При этом первые входы двухвходового элемента ИЛИ и двухвходового элемента И с номером i,Osi.p-H , подсоединены к выходной шине блока 4 с номером ( -f ), а вторые входы - к выходной шина блока 5 с номером ( 1 ). Блок 8 (фиг. 4) сумматора-умножителя - это матрица двухвходовых элементов И. При этом каждая входная шина блока 8 с номером i,0 « j р - 2t до пересечения через двуйвходовой элемент И с выходной шиной с номером j+1. являет ся столбцом, а после пересечения - строкой матрицы Блоки 9, 10, 11 предлагаемого устройства аналогично блокам 4 и 5 представляют собой группы двухвходовых але.ментов И. При этомкаждый из них имеет группу вертикальных входных шин и одну .горизонтальную входную шину. Входы двухвходовых элементов И каждого из от меченных блоков соединены с горизонталь ной входной шиной, а первые входы двухвх Ьцовых элементов И - с вертикальными входными шинами. Количество вертикаль ых входных шин блока 11 равно числу 96 выходнык шин блока 8, а количество,вертикальных входных шин блоков 9 и 10 равно числу выходных шик блоков 7 н 8. Сумматор-умножитель работает следу. ющим образом. При выполнении арифметических операций сложения и умножения сигнал признака операции подается по входу 17 на первые входы элементов ИЛИ 2 и 3. Сигналы, соответствующие операндам X иУ поступают по одному из входов группы входов 18 и одному из входов группы входов 19 на входы блоков 4 и 5 соответственно. Одновременно сигнал признака опера-, ции с выходов элементов ИЛИ 2 и 3 подается на входы блоков 4 и 5 соответственно. С выходов блока 4 сигнал, соответствующий операнду X , поступает на входы блоков 6 и 7, а с выходов блока 5 сигнал, соответствующий операнду Y . на входы блоков 6 и 7, С выходов блока 6 сигналы проходят на входы блока 8, с выходов блока 8 и блока 7 сигналы, соответствующие результату выполняемой операции - на входы блоков 9, 10, 11. Одновременно на управляющие входы блоков 9 и 1О подается сигнал тфизнака операции, в результате чего результат операции поступает на выходы 12 и 13 соответственно. На выходе 14 в этом случае сигнал не появляется, йоскольку отсутствует управляющий сигнал на управляющем входе блока 9. Операция контроля ошибки в операнде X (V) заключается в поиске такой ситуации, при которой сигнал появляется более чем на Одном входе группы входов 18, 19. При контроле ошибки в операнде Д (Y) сигнал признака операции поступает на вход 15, 16 устройства. При этом с выхода элемента ИЛИ 2 (3) управляющий сигнал поступает на управляющий вход только блока 4 (5), в резуль тате чего ко входам блоков 6 и 7 доступ имеют входные сигналы только одного из перандов. При наличии на входах группы входов 18 (19) более одного сигнала с выхода блока 6 сигнал подается на вход блока 11 и вторые входы блоков 9, 10. Одновременно с выходов блока 1 управляющий сигнал поступает на управляющий второй вход блока 11, в результате чего на выходе 14 появляется сигнал Ошибка. При наличии на входах 18 (19) одного сигнала на выходах блоков 8 и 7 сигнал не возникает, что исключает его появление на выходе .14. 76 При контроле ошибки в операнде Х( на выходах 12 и 13 сигналы не возника ют, поскольку отсутствует управляющий сигнал на управляющем входе блоков 9 и 10. Таким образом, вновь введенные три элемента ИЛИ, пять блоков коммутации цают возможность ввести две дополнительные операции контроля, что расширив ет функциональные возможности сумма гора-умножителя, так как оно может выполнять не только арифметические операции сложения и умножения над операндами X и Y , но и контроль ошибок в операнде X и KOHtроль ошибок в операнде Y ... Формула изобретения Матричныйсумматор-умножитель, содержащий блок расстановки операндов, блок равенства операндов, матрицу элементов И, причём выходы блока расстановкй операндов соединены сЪ входами матрицы элементов И, отличаю - щ и и с я тем, что, с целью расширений функциональных возможностей устройства путей ввецёния операции контроля вхрднЬгх операндов, & сумматор-умножитель введены первый, второй и третий элементы ИЛИ, первый,. второй, третий, четвертый и пятый, блоки коммутации, первый управляющий вход сумма тора-умножител.я соединен с первыми входами первого и второго элементов ИЛИ, вто.рой управляющий вход сумматора-умножителя соединен со вторым входом nep-i врго элемента ИЛИ и с первым входом третьего элемента ИЛИ, третий управляюздий ВХОД сумматора-умножителя сое ди8нен со вторыми входами второго и третьего элементов ИЛИ, выходы которых со- единены соответственно с управляющими входами первого и второго блоков коммутации, информационные входы первого и , второго блоков коммутации являются соответственно входами операндов сумматора-умножителя, выходы riepBot o блока коммутации соединены с первыми группами входов блоков расста новки операндов и равенства операндов, выходы второго блока коммутации соединены со вторыми группами входов блоков расстановки операндов и равенства операндов, выходы блока равенства операндов соединены с первыми входами третьего и четвертого блоков коммутации, выходы матрицы элементов И соединены со вторыми входами третьего и четвертого блоков коммутации и с первым входом пятого блока коммутации, третий управляющий вход сумматораумножигелй соединен с. управляющими входами третьего и четвертого блоков коммутаций, выход первого элемента ИЛИ соединен с управляющим входом пятого коммутации, выходы третьего, четвертого и пятого блоков, коммутации являются соотбетстверно выходами результатов умножения, сложения и контроля сумматора-умножителя. Источники информации, прин51ТЫё во внимание при дкспёртизе 1. Авторское свидетельство СССР М 352276, кл. G 06 F 7/52, 1969. 2. Авторское свидетельство СССР 256368, кл. Q 06 F 7/50, 1967/ 3. Авторское свидетельство СССР № 496555, кл. Q 06 F 7/3S, 1974 (прототип).

15

fS

75

f П

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Матричное вычислительное устройство | 1974 |

|

SU496555A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Матричное вычислительное устройство | 1975 |

|

SU555400A1 |

| Матричное устройство для сложения | 1979 |

|

SU883896A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| СУММАТОР-УМНОЖИТЕЛЬ | 1969 |

|

SU256368A1 |

| Вычислительное устройство | 1980 |

|

SU1008731A1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

/

О1

p-f

UJ

о

72

a 1

p-1

(p-1)

0 1

()

(puz 2

(Риг. if

Авторы

Даты

1980-09-30—Публикация

1978-03-28—Подача