вторая группа входов } -го (i -1,..., И|И- разрядность операндов блока памяти переносов нуля в старший разряд псздключена к первой группе входов (1+1)-гоблока памяти переносов нуля в .с. разряд, к второй группе входов ( блока эквивалентного двоичного сдвига, к первой группе входов (1+2)-го блока эквивалентного двоичного сдвига и к(+2)-R ч группе входов блока сдвига, вторые

rpynnfti входов (и-1)-го блока памяти переносов нуля в старший разряд и И-го блока эквивалентного двоичного сдвига подключены к.(п+1)й группе входов блока сдвига, выходы блоков памяти переносов нуля в старший раэм ряд образуют группу выходов переноса блока сдвига, выходы блоков эквивалентного двоичного сдвига образуют группу выходов результата блока сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1991 |

|

RU2030792C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2047896C1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Процессор | 1977 |

|

SU691858A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Арифметическое устройство | 1975 |

|

SU577526A1 |

1. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТЮ, содержащее блок поразрядной арифметики, блок формирования переносов и блок формирования результата, каждый .разряд которого содержит две группы Многовходовых элементов И, причем первые входы многовходовых элементов И первой группы подключены к первой группе входов блока формирования результата,, первые входы Многовходовых элементов- И второй группы пojD ключeны-к второй группе входов блока формиров,ания результата, остсшьные одноименные входы одноименных многовходовых элементов И первой и второй групп подключены к соответствующим входам третьей группы входов блока формирования результата, выход i-го многовходового элемента И первой группы соединен с выходом (i-1/-го многовходового элемента И второй группы и с (i-lJ-M выходом разряда блока формирования результата, выход Ьоследнего многовходового эле- : мента И первой группы соединен с выходом первого многовходового элемента И второй группы и с первым выходом разряда блока формирования ре эультата, первая и вторая группы . входов блока поразрядной арифметики подключены соответственно к шинам первого и второго операндов устррйства, группа выводов переноса пораэ- ,Рядной арифметиКи,подключена к первой группе входов блока формирова- i . ия переносов, вторая группа входов которого подключена к шинеуправления устройства, выходы блока формирования переносов подключены к соответствующим входам второй группы ... входов блока формирования результата, выходы разрядов которого подключены к шине результата устройства отличающееся тем, что, ,с целью расширения функциональных I возможностей-устройства за счет вы. iполнения логической операции сдвига, а lOHO содержит блок сдвига и группу :элементов ИЛИ, причем входы блока 1(0 сдвига подключены к шине сдвига устройства, группа выходов переноса блоп (ка сдвига подключена к третьей груп-пе входов блока формирования пере,носов, группа выходов (результата : блока сдвига подключена к первым входам соответствующих элементов ИЛИ группы, вторые входы которых подключены к соответствуквдим выходам блока пораз рядной арифметики, а выходы элементов ИЛИ подключены к соответствукадим . входам третьей группы блока формиро- ЮО вания результата. 2. Устройство по П.1, о тли ч аю щ е е с я тем, что блок сдвига р содержит в каждом разряде блок памя- Лл ти переносов нуля в старший разряд .и блок эквивалентного двоичного сдвига, причем первая группа входов перч вого блока эквивалентного двоичного сдвига, подключена к первой группе входов блока сдвига, первая группа входов первого блока памяти переносов/ нуля в разряд подключена к iвторой группе входов первого блока :эквивалентного двоичного сдвига, к первой группе входов второго блока эквивалентного двоичного сдвига и - IK.второй группе входов блока сдвига.

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, работающих в системах счисления с большими основаниями.

Известны устройства, в которых связь между разрядами осуществляется цеп1 распространения переносов.

Известно суммирующее устройство, содержащее регистры чисел, регистр суммы, первую тактовую шину, блок выбора и преобразования операндов, кодовые шины двух операндов, блок формирования условий возникновения и распространения переносов для каждого разряда, вторую тактовую шину, блок формирования условий возникновения и распространения переносов для групп разрядов, состоящий из нескольких последовательно переключающихся ступеней, каждая из которых содержит узел формирования основных условий и узел формирования дополшительных условий, причем первая сту|пень представлена регистрами, а вторая и все последующие - комбинационной логикой 1.

Известен параллельный комбинационный сумматор,- который содержит ц полных одноразрядных су|«4аторов, выходы переносов которых подключены к . первым входам элементов И переноса, вторые входы которых соединены с дополнительной входной шиной. Выходы элементов И переноса подключены к первым входам элементов ИЛИ переноса, вторые входы которых заисключе; нием элемента ИЛИ переноса старшего разряда) соединены с выходом элемента И, первый вход которого соединен со входом переноса младшего разряда, а второй - с выходом элемента НЕ. Ко второму входу элемента ИЛИ переноса старшего разряда подключен выход элемента И. Выходы элементов ИЛИ переноса подключены ко входам переносов старших разрядов t2j.

Наиболее близким к изобретению является параллельный сумматор с одновременнь 1 переносом, который содержит блок формирован 1я поразрядных i сумм и поразрядных переносов в состав которого входят четыре элемента

образования поразрядных сумм и поразрядных переносов, блок формирования

переносов во все разряды, в состав

:которого входят три элемвнта формиO рования переноса в старший и два последующих разряда соответственно блок формирования результата, в состав которого входят четыре элемента учета переносов ЗД.

с Недостатком прототипа являются ограниченные функциональные возможности , поскольку при поступлении на его входы одного числа он не представляет возможности сдвига этого

числа на один двоичный разряд вправо.

Цель изобретения - расширение функциональных возможностей устройст-. ва путем добавления логическдй операции сдвиг числа на один двоичный

разряд вправо.

Поставленная цель достигается тем, что вычислительное устройство, содержащее блок поразрядной арифметики, блок формирования переносов и блок

формирования результата, каждый разряд которого содержит две группы многовходовых элементов И, причем первые входы многовходовых элементов И первой группы подключены к первой

группе входов блока формирования результата, первые входы многовходовых элемейтов И второй группы подключены к второй группе входов формирования результата, остальные одноименные входы одноименных многовходовых элементов И первой и второй .групп подключены к соответствующим входам третьей группы входов блока формирования результата, выход i-ro мно- i говходового элемента И первой группы

соединен с выходом (-f многовходрвого элемента И второй группы и

c( выходом разряда блока формирования результата, выход последнего многовходового элемента И первой группы соединен с выходом перво О многовходового элемента И второй группы и с первым выходом разряда блока формирования результата, перва и вторая группы входов блока разрядной поразрядной арифметики под- ьключены соответственно к шинам первого и второго операндов устройства, группа выходов переноса блока поразрядной арифметики подключена к первой группе входов блока Формирования переносов, вторая группа входов которого подключена к шине управления устройства, выходы блока формирования переносов подключены к соответствующим входам второй группы входов блока формирования результата, выходы разрядов которого подключены к шй не результата устройства, содержит блок сдвига и группу элементов ИЛИ, причем входы блока сдвига подключены к шине сдвига устройства, группа входов Переноса блока сдвига подключена к третьей группе входов блока формйрования переносов, группа выходов результата блока сдвига подключена к первым входам соответствующих элементов ИЛИ группы/вторые входы которых подключены к соответствующим выходам блока поразрядной арифметики, а выходы элементов ИЛИ подключены к соответствующим входам третьей группы блока формирования результата

Кроме того, блок сдвига содержит в каждом разряде блок памяти переносов нуля в старший разряд и блок эквивгшентного .двоичного сдвига, причем первая группа входов первого блока эквивалентного двоичного сдвига подключена к первой группе входов блока сдвига, первая группа входов первого блока памяти переносов нуля в старший разряд подключена к второй группе входов первого блока эквива- ; лентного двоичного сдвига, к первой rpyrine. входов второго блока эквивалентного двоичного сдвига и к второй группе входов блока сдвига, вторая группа входов 1-го(1,..., И , где h - разрядность операндов блока памяти переносов нуля в старший разряд подключена к первой группе входов(-i-l)-го блока памяти переносов нуля в старший разряд, к второй группе входов Сi+l)-го блока эквивалентного двоичного сдвига, к первой группе входов (4+2)-го блока эквивалентногодвоичного сдвига и к (i +2)-И группе входов блока сдвига, вторые, группы входов (и -1)-го блока памяти переносов нуля в старший разряд и Г)-го блока эквивалентного двоичного сдвига подключены к (и +11-Й группе входов блока сдвига, выходы, блоков памяти переносов нуля в старший разряд.

образуют группу выходов переноса бло ка сдвига, выходы блоков эквивалентного двоичного сдвига образуют группу выходов результата блока сдвига.

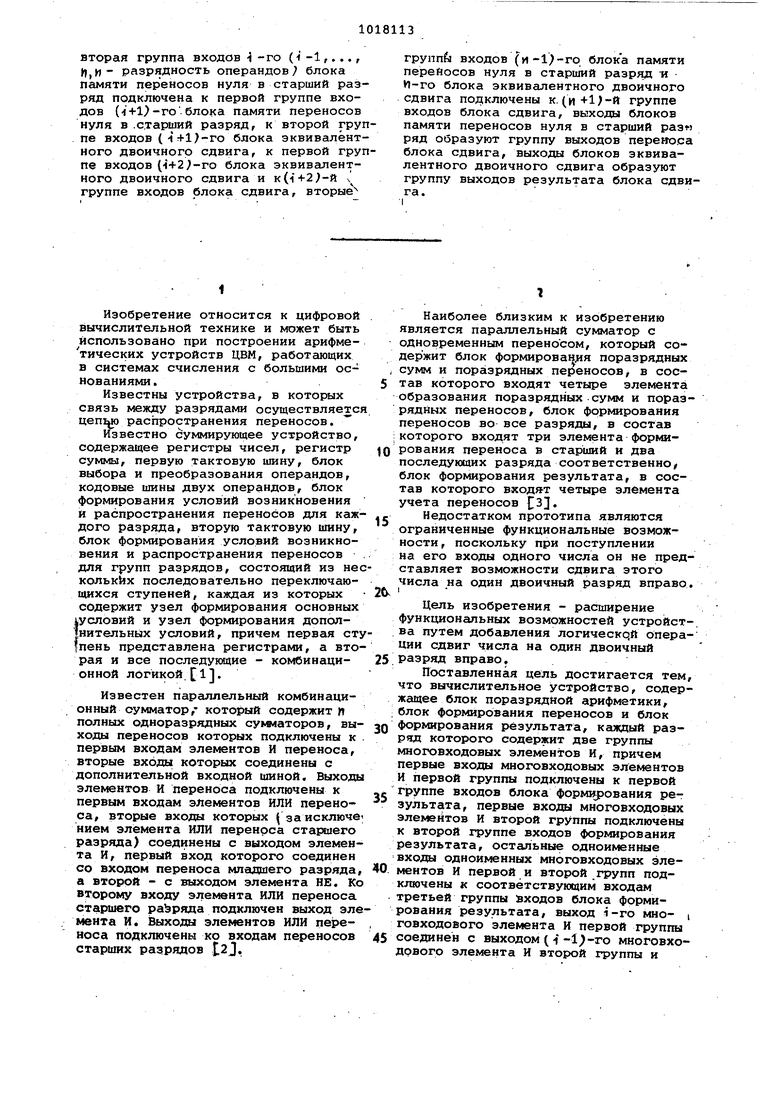

На фиг;1 представлена 6лр 7схема ; предложенного вычислительного устрой:ства на фнг.2 - 11 реализация устройст ; ва на примере для разрядности И,г4 и системн счисления с основанием . Устройство содержит блок 1 порази рядной арифметики, блок 2 сдвига, блок 3 формирования переносов, группу 4 элементов ИЛИ, блок 5 формирования результата.

Входы второй группы блока 3 и первой группы блока 5 подключены к шине б управления устройства. Входы второй и третьей групп блока 5 подключены к соответствующим выходам блрков 3 и 4 соответственно. Входы первой и второй групп блока 4 подклй чены к соответствующим выходам ре,зультата сдвига блока 2 и поразрядных сумм блока 1 соответственно.Входы первой и третьей групп блока 3 подключены к первым выхода/л переноса блоков 1 и 2 соответственно. .Входы первой и второй групп бЯока- 1 и .-вход блока 2 подключены к шинам первого, второго операндов и сдвига устройстjBa 7., 8 и 9 соответствено. Выход блока 5 подключен к выходу 10 результата устройства.

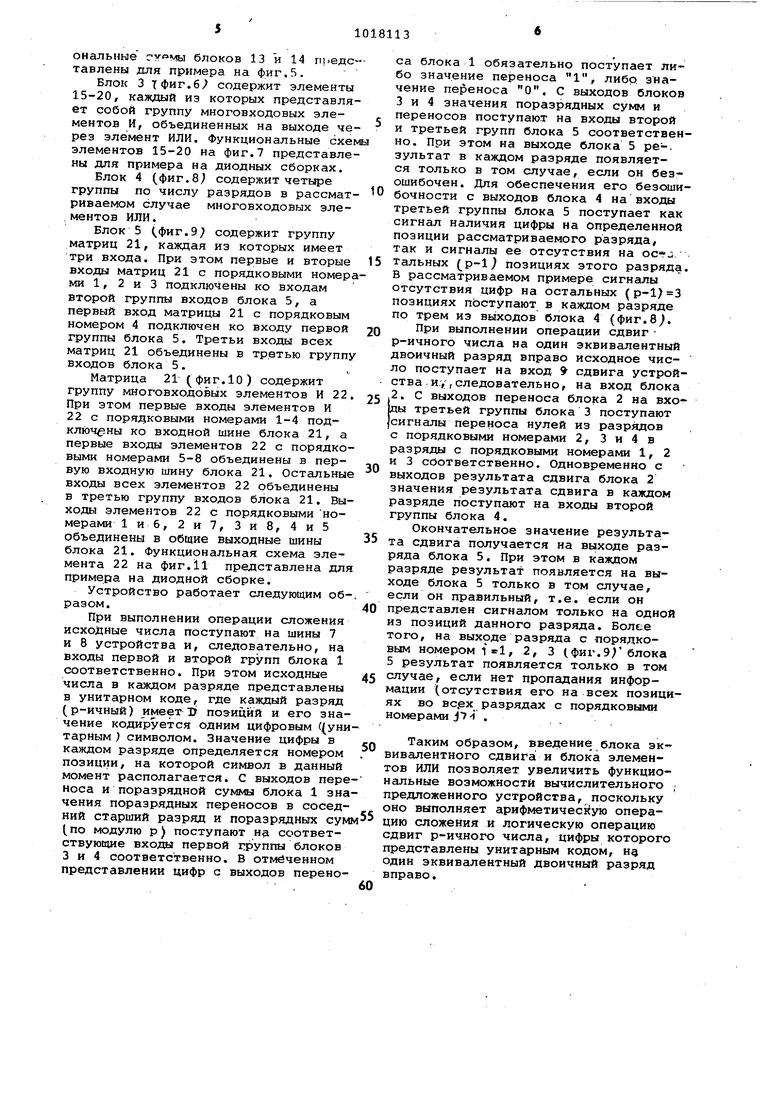

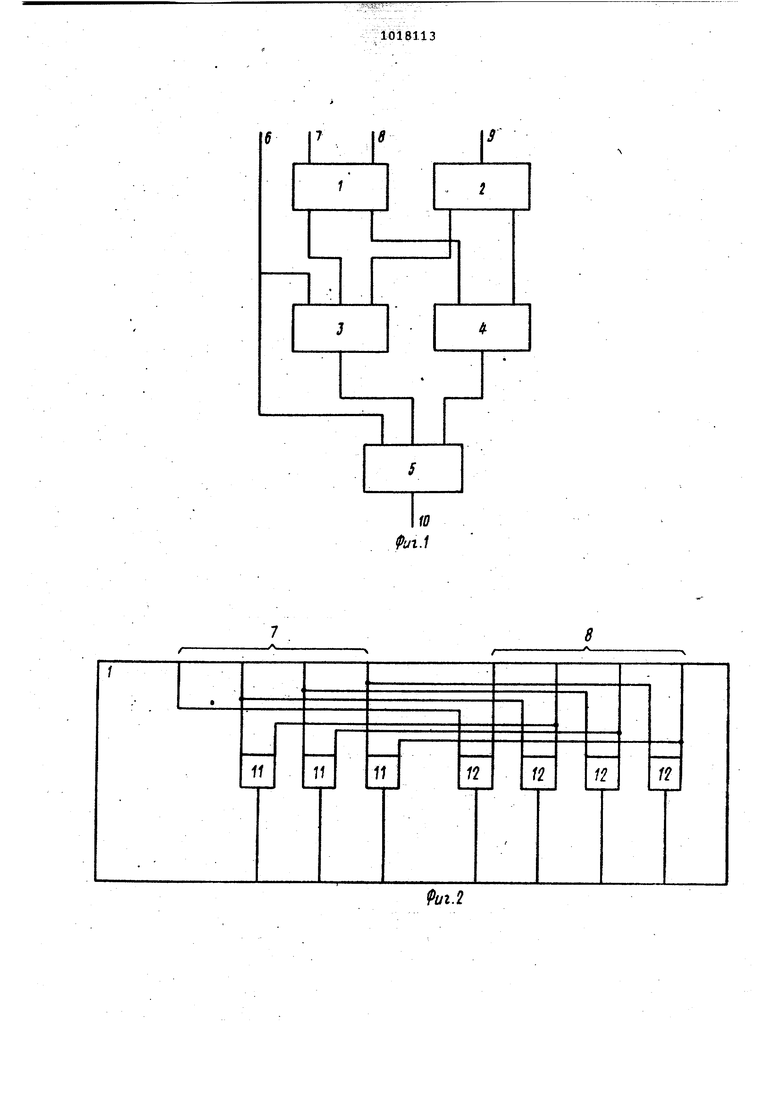

Блок 1 (фиг.2) содержит матрицы 11 переносов в соседний старший разряд при сложении двух р-ичных чисел и матриц 12 поразрядных сумм причем первый и второй матрицы 11 с порядковым номером 1 1,2 и 3 подключены ко входам первой и второй групй блока 1 с порядковым номером , 3 ;и4 соответственно,а первый и второй входы матрицы 12с порядковым номеромЧ«1, 2, 3 и 4 подключены к одноименным входам первой и второй групп блока 1 соответственно, функциональные схемы матриц 11 и 12 представлены для примера на Фи.г.3.

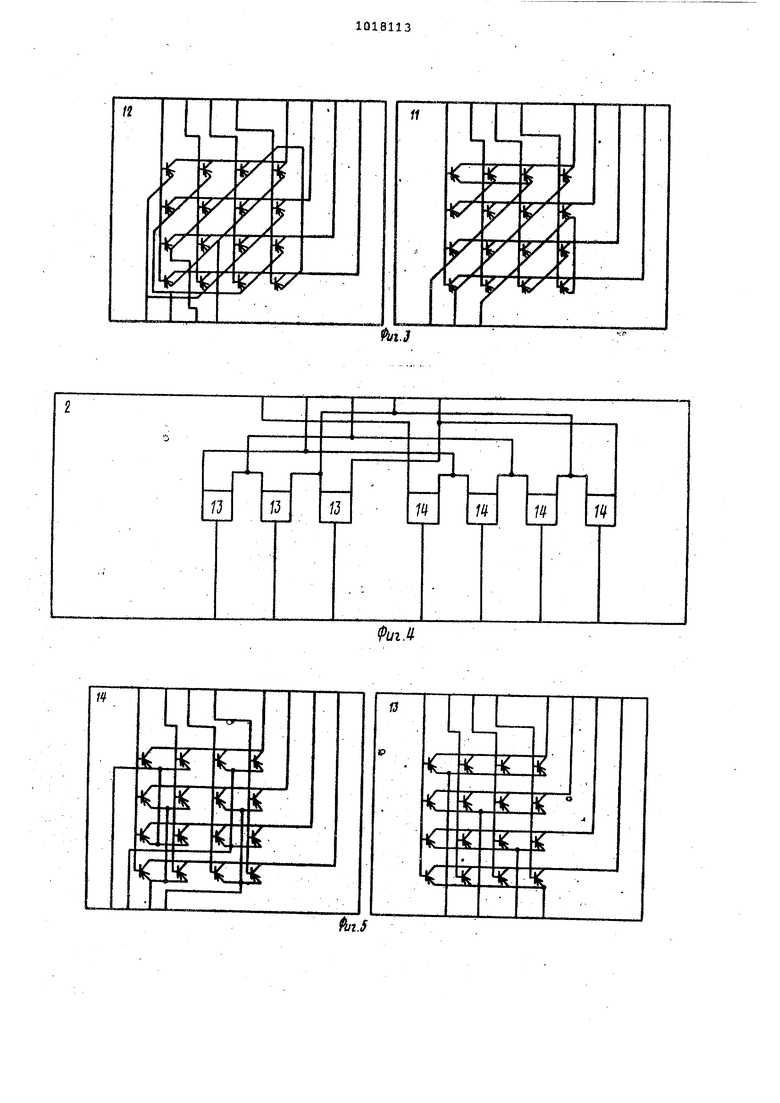

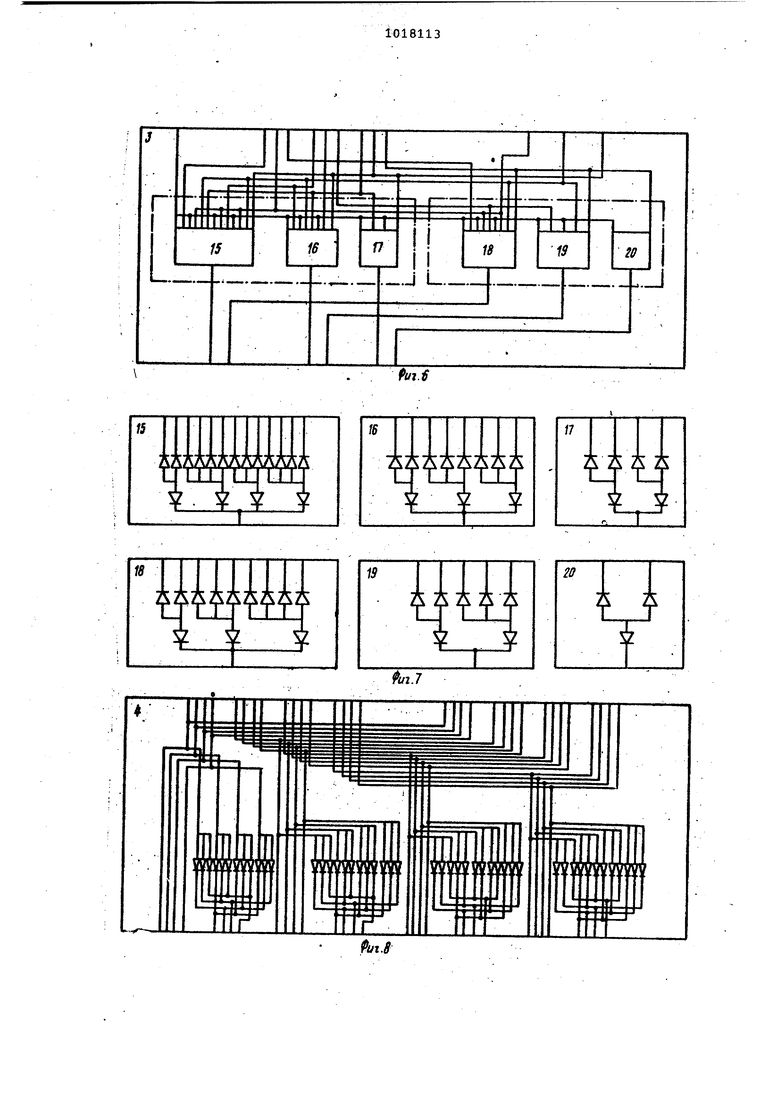

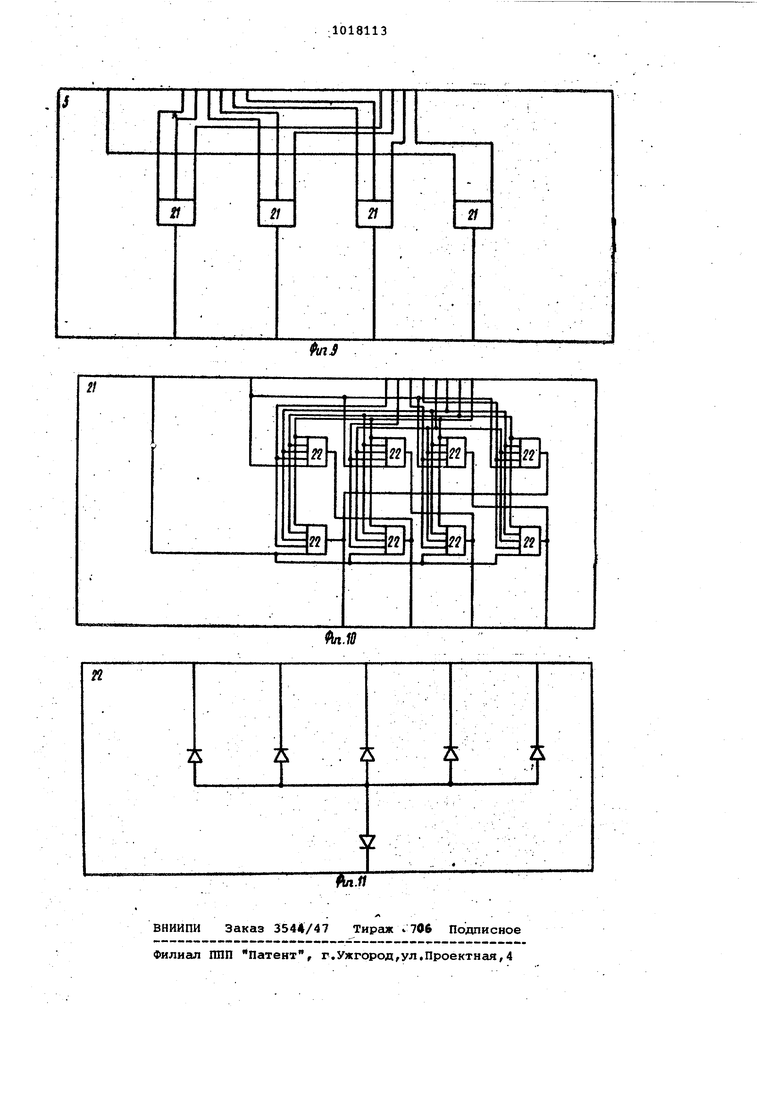

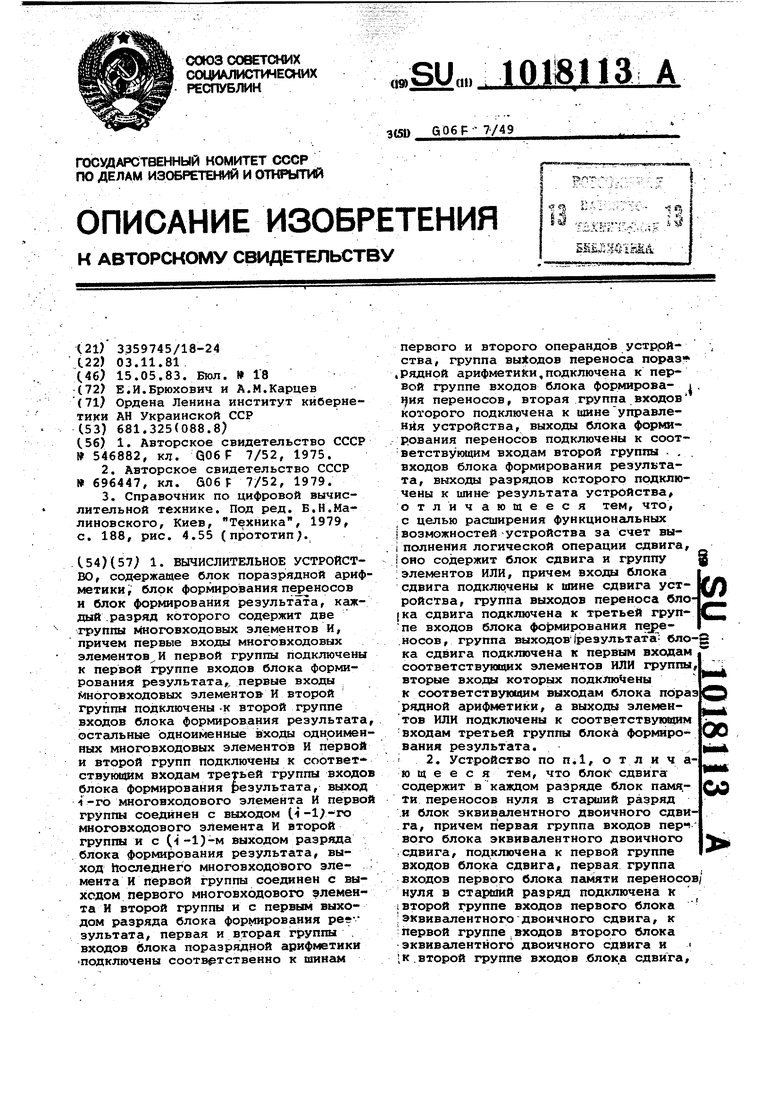

Блок 2 (фиг.4) содержит, блоки 13 памяти переносов нуля в соседний старший разряд при выполнении операцин Сдвиг на эквивалентное число двоичных разрядов ( в рассматриваемом примере - сдвиг на один двоичный разряд вправо числа, представленного в системе счисления с основанием ) и блоки 14 эквивалентного двоич кого сдвига одного разряда р-ичного числа, причем вторая группа входов блока 13 с порядковым iHoMepoMl-l, 2 объединена с первой группой входов блока 13 с порядковым номером 1-И соответственно, а вторая группа вхо:ДОВ- 1блока 14 с порядковым номером j 1, 2, 3 объединена с первой группой входов блЬка 14 с порядковым номером -j+l соответственно. Функциональные блоков 13 и 14 ni-едставлены для примера на фиг.5. Блок 3 ТФиг.6у содержит элементы 15-20, каждый из которых представляет собой группу многовходовых элементов И, объединенных на выходе через элемент ИЛИ. Функциональные схем элементов 15-20 на фиг.7 представлены для примера на диодных сборках. Блок 4 (фиг.8; содержит четыре группы по числу разрядов в рассмат риваемом случае многовходовых элементов ИЛИ. Блок 5 (фиг.97 содержит группу матриц 21, каждая из которых имеет три входа. При этом первые и вторые входы матриц 21 с порядковыми номера ми 1 , 2 и 3 подключены ко входам второй группы входов блока 5, а первый вход матрицы 21 с порядковым номером 4 подключен ко входу первой группы блока 5. Третьи входы всех матриц 21 объединены в третью группу входов блока 5. Матрица 21 (фиг.10) содержит группу многовходовых элементов И 22 При этом первые входы элементов И 22 с порядковыми номерами 1-4 подключены ко входной шине блока 21, а первые входы элементов 22 с порядковыми номерами 5-8 объединены в первую входную шину блока 21. Остальные входы всех элементов 22 объединены в третью группу входов блока 21. Выходы элементов 22 с порядковыми номерами 1иб, 2и7, Зи8, 4и5 объединены в общие выходные шины блока 21. Функциональная схема элемента 22 на фиг.11 представлена для примера на диодной сборке. Устройство работает следующим образом. При выполнении операции сложения исходные числа поступают на шины 7 и 8 устройства и, следовательно, на входы первой и второй групп блока 1 соответственно. При этом исходные числа в каждом разряде представлены в унитарном коде, где каждый разряд (р-ичный) имеет 1 позиций и его значение кодируется одним цифровым ((уни тарным ) символом. Значение цифры в Каждом разряде определяется номером позиции, на которой символ в данный момент располагается. С выходов пере носа и поразрядной суммы блока 1 зна чения поразрядных переносов в соседний старший разряд и поразрядных сум (по модулю р) поступают на соответствующие входы первой группы блоков 3 и 4 соответственно. В отмеченном представлении цифр с выходов перено са блока 1 обязательно поступает либо значение переноса 1, либр значение переноса О. С выходов блоков 3 и 4 значения поразрядных сумм и переносов поступают на входы второй и третьей групп блока 5 соответственно. При этом на выходе блока 5 ре-, зультат в каждом разряде появляется только в том случае, если он безошибочен. Для обеспечения его безошибочности с выходов блока 4 на входы третьей группы блока 5 поступает как сигнал наличия цифры на определенной позиции рассматриваемого разряда, так и сигналы ее отсутствия на тальных (р-1 позициях этого разряда. В рассматриваемом примере сигналы отсутствия цифр на остальных ( позициях поступают в каждом разряде по трем из выходов блока 4 (фиг.8. При выполнении операции сдвиг р-ичного числа на один эквивалентный двоичный разряд вправо исходное число поступает на вход 9 сдвига устройства и, следовательно, на вход блока ,2. С выходов переноса блока 2 на вхощы третьей группы блока 3 поступают {сигналы переноса нулей из разрядов с порядковыми номерами 2, 3 и 4 в разряды с порядковыми номерами 1, 2 и 3 соответственно. Одновременно с выходов результата сдвига блока 2 значения результата сдвига в кгикдом разряде поступают на входы второй группы блока 4. Окончательное значение результата сдвига получается на выходе разряда блока 5. При этом в каждом разряде результат появляется на выходе блока 5 только в том случае, если он правильный, т.е. если он представлен сигналом только на одной из позиций данного разряда. Более того, на выходе разряда с порядковым номером , 2, 3 (фиг.9)блока 5 результат появляется только в том случае, если нет пропадания информации (отсутствия его на всех позициях во вс.ех разрядах с порядковыми номерами , Таким образом, введение блока эквивалентного сдвига и блока элементов ИЛИ позволяет увеличить функциональные возможности вычислительного , предложенного устройства, поскольку оно выполняет арифметическую операцию сложения и логическую операцию сдвиг р-ичного числа, цифры которого представлены унитарным кодом, нд один эквивалентный двоичный разряд вправо.

11

tf

iD

иг.1

12

n

12

12

13

15

/J

/

1

w

/

f

A Д i i i

т

,

Авторы

Даты

1983-05-15—Публикация

1981-11-03—Подача