Изобретение относится к электросвязи и может использоваться при передаче дискретной информации, а также в системах связи с импульсно-кодовой модуляцией.

Известен баланстный кодер, содержащий распределитель четных и нечетных импульсов, вход которого является входом устройства, первый выход подключен к входу запоминающего устройства четных импульсов, а второй выход - к входу запоминающего устройства нечетных импульсов, причем выход запоминающего устройства четных импульсов подключен к входу блока управления полярностью четных импульсов, а выход запоминающего устройства нечетных импульсов соединен с входом блока управления полярностью нечетных импульсов, выходы которых подключены к первому и второму входам блока формирования выходной импульсной последовательности, выход которого подключен к входу блока стробирования циклового импульса, выход которого является выходом устройства, при этом первый выход распределителя четных и нечетных импульсов подключен к входу первого интегратора четных импульсов, а второй выход pаспределителя четных и нечетных импульсов подключен к входу первого интегратора нечетных импульсов, выходы первых интеграторов подключены соответственно к входам вторых интеграторов четных и нечетных импульсов и одновременно выходы первых интеграторов четных и нечетных импульсов подключены к первым входам блоков сравнения полярностей сумм соответственно четных и нечетных импульсов, выход второго интегратора четных импульсов соединен с вторым входом блока сравнения полярностей сумм четных импульсов, а выход блока сравнения полярностей сумм четных импульсов подключен к управляющему входу второго интегратора четных импульсов и одновременно к управляющему входу блока управления полярностью четных импульсов и к первому входу блока формирования циклового импульса, аналогично выход второго интегратора нечетных импульсов соединен с вторым входом блока сравнения полярностей сумм нечетных импульсов, а выход блока сравнения полярностей сумм нечетных импульсов подключен к управляющему входу второго интегратора нечетных импульсов и одновременно к управляющему входу блока управления полярностью нечетных импульсов и к второму входу блока формирования циклового импульса, выход которого подключен к второму входу блока стробирования циклового импульса.

Недостатки известного балансного кодируюущего устройства состоят в недостаточной балансировке постоянной составляющей и в наличии существенного остатка мощности сигнала на полутактовой частоте.

Цель изобретения состоит в повышении точности балансировок постоянной составляющей и в уменьшении мощности сигнала на полутактовой частоте.

Цель достигается тем, что в балансное кодирующее устройство, содержащее распределитель четных и нечетных импульсов, вход которого является входом устройства, первый выход соединен с первым входом первого интегратора четных импульсов и первым входом блока памяти четных импульсов, выход которого соединен с первым входом блока управления полярностью четных импульсов, блок памяти нечетных импульсов, выход которого соединен с первым входом блока управления полярностью нечетных импульсов, первый интегратор нечетных импульсов, второй интегратор нечетных импульсов, выход которого соединен с первым входом первого блока сравнения, выход которого соединен с первым входом второго интегратора нечетных импульсов и первым входом формирователя циклового импульса, выход которого соединен с первым входом блока стробирования циклового импульса, второй интегратор четных импульсов, выход которого соединен с первым входом второго блока сравнения, выход которого соединен с первым входом второго интегратора четных импульсов и вторым входом формирователя циклового импульса, формирователь выходной последовательности импульсов, выход которого соединен с вторым входом блока стробирования циклового импульса, выход которого является выходом устройства, и блок управления, введены коммутаторы нечетных импульсов, коммутаторы четных импульсов, элемент задержки на один такт, элемент задержки нечетных импульсов и элемент задержки четных импульсов, при этом второй выход распределителя четных и нечетных импульсов соединен через элемент задержки на один такт с первым входом блока памяти нечетных импульсов и первым входом первого интегратора нечетных импульсов, выход которого соединен с первым входом первого коммутатора нечетных импульсов, выход которого соединен с вторыми входами первого блока сравнения и второго интегратора нечетных импульсов, выход первого интегратора четных импульсов соединен с первым входом первого коммутатора четных импульсов, выход которого соединен с вторыми входами второго блока сравнения и второго интегратора четных импульсов, выход блока управления полярностью нечетных импульсов соединен непосредственно и через элемент задержки нечетных импульсов соответственно с первым и вторым входами второго коммутатора нечетных импульсов, выход которого соединен с первым входом формирователя выходной последовательности импульсов, выход блока управления полярностью четных импульсов соединен непосредственно и через элемент эадержки четных импульсов соответственно с первым и вторым входами второго коммутатора четных импульсов, выход которого соединен с вторым входом формирователя выходной последовательности импульсов, вторые входы первого коммутатора нечетных импульсов и первого коммутатора четных импульсов подключены к первому выходу формирователя циклового импульса, второй и третий выходы которого соединены с вторыми входами соответственно блока управления полярностью нечетных импульсов и блока управления полярностью четных импульсов, первый выход блока управления соединен с вторым входом распределения четных и нечетных импульсов, второй выход блока управления соединен с вторыми входами блока памяти нечетных импульсов, блока памяти четных импульсов, первого интегратора нечетных импульсов и первого интегратора четных импульсов, третий и четвертый выходы блока управления соединены с третьими входами соответственно первого коммутатора четных импульсов и первого коммутатора нечетных импульсов, пятый выход блока управления соединен с третьими входами второго коммутатора нечетных импульсов и второго коммутатора четных импульсов, шестой выход блока управления соединен с третьими входами второго интегратора четных импульсов, второго интегратора нечетных импульсов и формирователя циклового импульса, седьмой выход блока управления соединен с третьим входом блока стробирования циклового импульса.

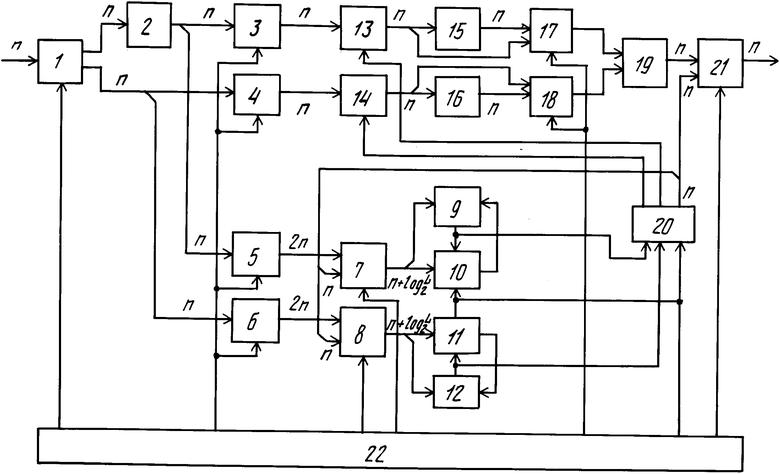

На чертеже приведена структурная электрическая схема предлагаемого кодирующего устройства, где 1 - распределитель четных и нечетных импульсов, 2 - элемент задержки на один тактовый интервал, 3 - запоминающее устройство нечетных импульсов, 4 - запоминающее устройство четных импульсов, 5 - первый интегратор нечетных импульсов, 6 - первый интегратор четных импульсов, 7 - коммутатор нечетных импульсов, 8 - коммутатор четных импульсов, 9 - блок сравнения полярностей сумм нечетных импульсов, 10 - второй интегратор нечетных импульсов, 11 - второй интегратор четных импульсов, 12 - блок сравнения полярностей сумм четных импульсов, 13 - блок управления полярностью нечетных импульсов, 14 - блок управления полярностью четных импульсов. 15 - элемент задержки нечетных импульсов, 16 - элемент задержки четных импульсов, 17 - коммутатор нечетных импульсов, 18 - коммутатор четных импульсов, 19 - формирователь выходной импульсной последовательности, 20 - блок формирования циклового импульса, 21 - блок стробирования циклового импульса, 22 - устройство управления.

Кодирующее устройство работает следующим образом.

Входные данные в виде последовательности многоуровневых импульсов, представленных n-разрядными двоичными числами, следуют друг за другом с интервалом времени Т секунд и разделяются в распределителе 1 четных и нечетных импульсов под управлением команд от устройства 22 управления на две подпоследовательности четных и нечетных по порядку следования импульсов с тактом 2Т секунд, причем подпоследовательность нечетных номеров импульсов задерживается в элементе 2 задержки на время Т секунд для обеспечения синхронной смены состояний с подпоследовательностью четных номеров импульсов. Обе подпоследовательности задерживаются на I тактов по 2 Т секунд в запоминающих устройствах 3, 4, представляющих собой блоки памяти, каждый из которых содержит по I последовательно включенных n-разрядных регистров сдвига с параллельным переносом, управляемых тактовыми импульсами с периодом следования 2Т секунд от устройства 22 управления. Одновременно с задержкой на I тактов вычисляются в первых интеграторах четных импульсов 5 и нечетных импульсов 6 суммы информационных блоков из I двоичных чисел каждой из двух подпоследовательностей. Работой устройств 3, 4 и интеграторов 5, 6 управляет устройство 22 управления так, что перед суммированием чисел двух очередных информационных блоков из I чисел четной и нечетной подпоследовательностей производится обнуление первых интеграторов 5 и 6, а по окончании суммирования на выходах устройств 3 и 4 появляются первые числа задержанных подпоследовательностей, сумма которых вычислялась в интеграторах 5 и 6. Суммы I n-разрядных двоичных чисел в интеграторах 5 и 6 представляются (n + log2 L)-разрядными двоичными числами, и в момент завершения суммирования через коммутаторы 7 и 8 по командам от устройства 22 управления обе суммы подаются на вторые интеграторы четных 10 и нечетных 11 подпоследовательностей, в которых вычисляются полные кодовые суммы четных и нечетных импульсов, причем интеграторы 10 и 11 работают как в режиме сложения, так и в режиме вычитания чисел. При вычислении кодовой суммы содержимого интеграторов 10 и 11 с содержимым интеграторов 5 и 6, поступающим к интеграторам 10 и 11 через коммутаторы 7 и 8 соответственно, предварительно определяется вид операции - сложение или вычитание, выполняемой над числами, хранящимися в интеграторах 10 и 11, и числами, поступающими от коммутаторов 7 и 8, для чего в блоке 9 сравнения производится сравнение знака полной кодовой суммы, накопленной в интеграторе 10 со знаком числа, поступившего от коммутатора 7, и в блоке 12 сравнения производится соответственно сравнение знаков чисел на выходах интегратора 11 и коммутатора 8. Сигналы с выходов блоков 9 и 12 определяют виды операций - сложение или вычитание, выполняемых в интеграторах 10 и 11, и подаются в блок 20, в котором по команде от устройства 22 управления формируется цикловой импульс в виде n-разрядного двоичного числа и команды управления блоками 13 и 14 управления полярностью через которые проходят задержанные импульсы с выходов устройств 3 и 4. Если числа на выходах интегратора 10 и коммутатора 7 совпадают по знаку, то интегратор 10 соответствующей командой от блока 9 устанавливается в режим вычитания, и по команде от устройства 22 управления в интеграторе 10 происходит вычитание из полной кодовой суммы, накопленной в интеграторе 10, числа, поступившего от коммутатора 7, а в блоке 20 формируется управляющий сигнал, который устанавливает блок 13 управления полярностью нечетных импульсов в режим инвертирования (смены знака) I ранее задержанных импульсов в устройстве 3. Если числа на выходах интегратора 10 и коммутатора 7 не совпадают по знаку, то интегратор 10 по команде от блока 9 устанавливается в режим сложения, по командам от устройства 22 осуществляется операция сложения накопленной в интеграторе 10 суммы с числом, поступившим от коммутатора 7, и блок 13 управления полярностью устанавливается в режим пропускания без инвертирования знаков подпоследовательности из I чисел, задержанных в устройстве 3. Подобным образом происходит выполнение операции сложения или вычитания в интеграторе 11, определяемой результатами сравнения знаков чисел в блоке 12, и операции инвертирования или неинвертирования в блоке 14 знаков подпоследовательности чисел, задержанных в устройстве 4. Сформированный в блоке 20 цикловой импульс в виде n-разрядного двоичного числа подается на коммутаторы 7 и 8 и на блок 21 стробирования циклового импульса, который выполняет вставку циклового импульса в выходную последовательность. Коммутаторы 7 и 8 управляются командами от устройства 22, и в момент готовности значения циклового импульса коммутаторы 7 и 8 переключаются на пропускание значения циклового импульса на входы интеграторов 10 и 11, в которых производится поочередное суммирование их содержимого с цикловым импульсом в зависимости от номера информационного блока из 21 входных импульсов, поступивших на вход устройства. Для нечетного номера блока из 21 входных импульсов суммирование циклового импульса выполняется в интеграторе 11, а для четного - в интеграторе 10. Суммирование выполняется по командам от устройства 22 управления. Двоичные n-разрядные числа, проходящие через блоки 13 и 14, подаются на коммутаторы 17 и 18 непосредственно и через элементы задержки 15 и 16 на Т секунд. Коммутаторы 16 и 18 управляются по командам от устройства 22 так, что при нечетном номере информационного блока из 21 входных импульсов через коммутатор 17 от блока 13 импульсы проходят, минуя элемент 15 задержки, а через коммутатор 18 импульсы от блока 14 проходят через элемент 16 задержки. Этим обеспечивается естественный порядок следования (сначала нечетный, а потом четный, т.е. 1, 2, 3, 4,...,I - 1, I) номеров импульсов на формирователь 19 выходной импульсной последовательности, в котором соединяются импульсы четных и нечетных подпоследовательностей. При четном номере блока из 21 входных импульсов коммутатор 17 переключается на выход элемента 15, при этом на формирователь 19 импульсы от блока 13 проходят через элемент 15 задержки и коммутатор 17, а коммутатор 18 переключается непосредственно на выход блока 14, от которого импульсы поступают через коммутатор 18 на формирователь 19 выходной импульсной последовательности. Тем самым изменяется естественный порядок следования номеров импульсов на формирователь 19 (сначала четный, а потом нечетный, т.е. 2, 1, 4, 3, 6, 5,..., I, I-1). Формирователь 19 выходной импульсной последовательности по командам от устройства 22 управления поочередно подает импульсы от коммутаторов 17 и 18 а блок 21 стробирования циклового импульса, который по командам от устройства 22 управления сначала выполняет стробирование циклового импульса и передачу его на выход устройства, а затем стробирует 21 импульс от формирователя 19. При этом в блоке 21 осуществляется стробирование циклового импульса и информационных импульсов данных от формирователя 19 со скоростью в (21+I)/21 раз выше скорости входных данных. Увеличение скорости необходимо, чтобы за время действия блока из 21 входных импульсов на выходе кодера действовал блок из 21+ I выходных импульсов с учетом добавления циклового.

Устройство 22 управления обеспечивает синхронизацию работы блоков кодера и представляет собой логическую схему со многими выходами, на которых действуют импульсы команд, которые управляются циклическим счетчиком команд, тактируемым встроенным генератором тактовых импульсов.

Таким образом осуществляется балансное кодирование последовательности выходных данных, при котором достигаются нулевые спектральные плотности на нулевой частоте и на частоте, равной половине тактовой частоты выходных данных кодера. Это достигнуто ценой незначительного увеличения скорости и соответственно ширины энергетического спектра данных на выходе кодера в (21 + I)/21 раз по сравнению со скоростью и шириной спектра сигнала данных на входе кодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ КОМПОСТЕР ПИЛОТ-СИГНАЛА | 1990 |

|

RU2011296C1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1990 |

|

RU2010425C1 |

| Способ передачи и приема дискретных сигналов | 1984 |

|

SU1223394A1 |

| Детектор двухчастотных сигналов относительной фазовой модуляции | 1985 |

|

SU1298947A1 |

| Многоканальное устройство для предварительной обработки данных геофизических исследований | 1983 |

|

SU1097993A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| СПОСОБ ПЕРЕДАЧИ СИГНАЛОВ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1991 |

|

RU2024206C1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

| ДВУХПРОВОДНАЯ ДУПЛЕКСНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ | 1991 |

|

RU2037966C1 |

| Устройство для контроля периода колебания | 1982 |

|

SU1099288A1 |

Изобретение относится к электросвязи и может использоваться при передаче дискретной информации, а также в системах связи с ИКМ. Цель - повышение точности балансировки постоянной составляющей и уменьшение величины мощности сигнала на полутактовой частоте. Входная последовательность многоуровневых импульсов разделяется в блоках 1,2 на две синхронные подпоследовательности четных и нечетных по порядку следования импульсов, которые задерживаются в устройствах 3,4 на 16 тактов. На протяжении 16 тактов каждой подпоследовательности сумма двух последовательностей 16 четных и нечетных импульсов вычисляется отдельно в интеграторах 5,6. Полная кодовая сумма четных и нечетных импульсов вычисляется отдельно в главных интеграторах 10,11, причем они могут работать как в режиме сложения, так и вычитания. Если накопленные суммы в интеграторах 5,10 и 6,11 совпадают по знаку, то подпоследовательности в блоках 13,14 инвертируются и главные интеграторы 10,11 работают в режиме вычитания. Если накопленные суммы интеграторах 5, 10 и 6,11 имеют разные знаки, то инвертирования в блоках 13,14 не происходит и главные интеграторы 10,11 работают в режиме сложения. Для передачи информации об инвертировании или неинвертировании данной группы из 32 импульсов формируется цикловый импульс в блоке 20. При объединении подпоследовательностей четных и нечетных импульсов в блоке 21 с цикловым импульсов в четных группах импульсы следуют в естественном порядке, а в четных группах четные и нечетные импульсы меняются местами посредством коммунаторов, 17,18 элементов 15,16 задержки и формирователя 19. Синхронизацию и управление работой блоков кодера обеспечивает устройство 22 управления. 1 ил.

БАЛАНСНОЕ КОДИРУЮЩЕЕ УСТРОЙСТВО, содержащее распределитель четных и нечетных импульсов, вход которого является входом устройства, первый выход соединен с первым входом первого интегратора четных импульсов и первым входом блока памяти четных импульсов, выход которого соединен с первым входом блока управления полярностью четных импульсов, блок памяти нечетных импульсов, выход которого соединен с первым входом блока управления полярностью нечетных импульсов, первый интегратор нечетных импульсов, второй интегратор нечетных импульсов, выход которого соединен с первым входом первого блока сравнения, выход которого соединен с первым входом второго интегратора нечетных импульсов и первым входом формирователя циклового импульса, выход которого соединен с первым входом блока стробирования циклового импульса, второй интегратор четных импульсов, выход которого соединен с первым входом второго блока сравнения, выход которого соединен с первым входом второго интегратора четных импульсов и вторым входом формирователя циклового импульса, формирователь выходной последовательности импульсов, выход которого соединен с вторым входом блока стробирования циклового импульса, выход которого является выходом устройства, и блок управления, отличающееся тем, что, с целью повышения точности устройства, в него введены коммутаторы нечетных импульсов, коммутаторы четных импульсов, элемент задержки на один такт, элемент задержки нечетных импульсов и элемент задержки четных импульсов, второй выход распределителя четных и нечетных импульсов соединен через элемент задержки на один такт с первым входом блока памяти нечетных импульсов и первым входом первого интегратора нечетных импульсов, выход которого соединен с первым входом первого коммутатора нечетных импульсов, выход которого соединен с вторыми входами первого блока сравнения и второго интегратора нечетных импульсов, выход первого интегратора четных импульсов соединен с первым входом первого коммутатора четных импульсов, выход которого соединен с вторыми входами второго блока сравнения и второго интегратора четных импульсов, выход блока управления полярностью нечетных импульсов соединен непосредственно и через элемент задержки нечетных импульсов соответственно с первым и вторым входами второго коммутатора нечетных импульсов, выход которого соединен с первым входом формирователя выходной последовательности импульсов, выход блока управления полярностью четных импульсов соединен непосредственно и через элемент задержки четных импульсов соответственно с первым и вторым входами второго коммутатора четных импульсов, выход которого соединен с вторым входом формирователя выходной последовательности импульсов, вторые входы первого коммутатора нечетных импульсов и первого коммутатора четных импульсов подключены к первому выходу формирователя циклового импульса, второй и третий выходы которого соединены с вторыми входами соответственно блока управления полярностью нечетных импульсов и блока управления полярностью четных импульсов, первый выход блока управления соединен с вторым входом распределителя четных и нечетных импульсов, второй выход блока управления - с вторыми входами блока памяти нечетных импульсов, блока памяти четных импульсов, первого интегратора нечетных импульсов и первого интегратора четных импульсов, третий и четвертый выходы блока управления - с третьими входами соответственно первого коммутатора четных импульсов и первого коммутатора нечетных импульсов, пятый выход блока управления - с третьими входами второго коммутатора нечетных импульсов и второго коммутатора четных импульсов, шестой выход блока управления - с третьими входами второго интегратора четных импульсов, второго интегратора нечетных импульсов и формирователя циклового импульса, седьмой выход блока управления - с третьим входом блока стробирования циклового импульса.

| Review of Electrical Communication Laboratories vol, 22, N 11, 12, 1974, pp.963-970. |

Авторы

Даты

1994-06-30—Публикация

1990-12-10—Подача