Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операций умножения и деления чисел.

Известны матричные устройства для умножения и деления, построенные из ячеек нескольких типов [1].

Недостатками этих устройств являются большое количество аппаратуры, неоднородность структуры из-за нерегулярности связей между ячейками и применение ячеек нескольких типов.

Наиболее близким по технической сущности к изобретению является матричное устройство для умножения и деления, содержащее матрицу ячеек из k строк и m столбцов, группы из k элементов ИЛИ, первую группу из k-1 элементов И, вторую группу из k-1 элементов И, третью группу из m элементов И и дополнительную строку из k ячеек, причем первый и второй выходы i-й ячейки строк с первой по k-ю (i = 1,...,m-1) соединены с первым и вторым входами (i+1)-й ячейки этой же строки соответственно, третий выход (i+1)-й ячейки строк с первой по k-ю соединен с третьим входом i-й ячейки этой же строки, четвертый выход j-й ячейки (j = 1,...,k-1) столбцов с второго по m-й соединен с четвертым входом (j+1)-й ячейки столбцов с первого по (m-1)-й соответственно, пятый выход j-й ячейки столбцов с первого по m-й соединен с пятым входом (j+1)-й ячейки этого же столбца, пятый вход ячеек с первой по m-ю первой строки соединен с соответствующим разрядом первого информационного входа устройства, первый выход ячеек с первой по k-ю m-го столбца соединен с третьим входом этой же ячейки, четвертый выход ячеек с первой по m-ю k-й строки соединен с соответствующим разрядом первого выхода устройства, первый вход режима работы устройства соединен с первыми входами элементов И первой, второй и третьей групп, с первыми входами элементов ИЛИ группы и с первым входом первой ячейки первого столбца, вторые входы элементов ИЛИ группы соединены с соответствующими разрядами второго информационного входа устройства, вторые входы элементов И второй и третьей групп соединены с соответствующими разрядами третьего информационного входа устройства, выходы элементов ИЛИ с первого по k-й группы соединены с вторыми входами ячеек с первой по k-ю первого столбца соответственно, выходы элементов И с первого по m-й третьей группы соединены с четвертыми входами ячеек с первой по m-ю первой строки соответственно, выходы элементов И с первого по (k-1)-й второй группы соединены с четвертыми входами ячеек с второй по k-ю m-го столбца соответственно, выходы элементов И с первого по (k-1)-й первой группы соединены с первыми входами ячеек с второй по k-ю первого столбца соответственно, третий выход ячеек с первой по (k-1)-ю первого столбца соединен с четвертым входом ячеек с второй по k-ю дополнительной строки соответственно и с вторым входом элементов И с первого по (k-1)-й первой группы соответственно, третий выход k-й ячейки первого столбца соединен с четвертым входом k-й ячейки дополнительной строки, четвертый выход ячеек с первой по (k-1)-ю первого столбца соединен с пятым входом ячеек с второй по k-ю дополнительной строки соответственно, первый и второй выходы j-й ячейки дополнительной строки соединены с первым и вторым входами (j+1)-й ячейки этой же строки соответственно, третий выход (j+1)-й ячейки дополнительной строки соединен с третьим входом j-й ячейки этой же строки, первый выход k-й ячейки дополнительной строки соединен с третьим входом этой же ячейки, первый вход первой ячейки дополнительной строки соединен с пятым входом этой же ячейки и входом уровня логического "0" устройства, второй вход режима работы устройства соединен с вторым входом первой ячейки дополнительной строки, четвертый выход ячеек с первой по k-ю дополнительной строки соединен с выходами соответствующих разрядов второго выхода устройства [2].

Кроме этого, ячейка матричного устройства для умножения и деления содержит одноразрядный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем первый вход ячейки соединен с ее первым выходом и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом элемента И, первый вход которого соединен с вторым входом ячейки и вторым ее выходом, третий вход которой соединен с входом переноса одноразрядного сумматора, первый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход переноса одноразрядного сумматора соединен с третьим выходом ячейки, четвертый вход которой соединен с вторым входом одноразрядного сумматора, выход которого соединен с четвертым выходом ячейки, пятый вход которой соединен с ее пятым выходом и вторым входом элемента И.

Недостатком этого устройства является большое количество аппаратуры из-за нерационального использования (особенно при делении чисел) ячеек дополнительной строки.

Целью изобретения является сокращение аппаратурных затрат.

Цель достигается тем, что в матричное устройство для умножения и деления, содержащее матрицу ячеек первого типа из k строк и m столбцов, причем первый и второй выходы i-й ячейки первого типа (i = 1,...,m-1) строк с первой по k-ю соединены с первым и вторым входами (i+1)-й ячейки первого типа этой же строки соответственно, третий выход (i+1)-й ячейки первого типа строк с первой по k-ю соединен с третьим входом i-й ячейки первого типа этой же строки, четвертый выход j-й ячейки первого типа (j = 1,...k-1) столбцов с второго по m-й соединен с четвертым входом (j+1)-й ячейки первого типа столбцов с первого по (m-1)-й соответственно, пятый выход j-й ячейки первого типа столбцов с первого по m-й соединен с пятым входом (j+1)-й ячейки первого типа этого же столбца, пятый вход ячеек первого типа с первого по m-ю первой строки соединен с соответствующим разрядом первого информационного входа устройства, первый выход ячеек первого типа с первой по k-ю m-го столбца соединен с третьим входом этой же ячейки, четвертый выход ячеек первого типа с первой по m-ю k-й строки соединен с соответствующим разрядом первого выхода устройства, введены k ячеек второго типа, причем первый и второй выходы ячеек второго типа с первой по k-ю соединены соответственно с первым и вторым входами ячеек первого типа с первой по k-ю первого столбца соответственно, третий выход первой ячейки второго типа соединен с выходом переполнения устройства, первый вход первой ячейки второго типа соединен с входом уровня логической "1" устройства, второй вход ячеек второго типа с первой по k-ю соединен с соответствующим разрядом второго информационного входа устройства, третий вход ячеек второго типа с первой по k-ю соединен с третьим выходом ячеек первого типа с первой по k-ю первого столбца соответственно, четвертый вход ячеек второго типа с второй по k-ю соединен с четвертым выходом ячеек первого типа с первой по (k-1)-ю первого столбца соответственно, пятый выход ячеек второго типа с первой по (k-1)-ю соединен с пятым входом ячеек второго типа с второй по k-ю соответственно, третий выход ячеек второго типа с второй по k-ю соединен с шестым входом ячеек второго типа с первой по (k-1)-ю соответственно, шестой вход k-й ячейки второго типа соединен с входом логического "0" устройства, четвертый выход ячеек второго типа с первой по (k-1)-ю соединен с первым входом ячеек второго типа с второй по k-ю соответственно и с выходами соответствующих разрядов второго выхода устройства, пятый вход первой ячейки второго типа соединен с входом режима работы устройства, четвертый выход k-й ячейки второго типа соединен с выходом младшего разряда второго выхода устройства, четвертый вход каждой ячейки первого типа первой строки и m-го столбца соединен с входом соответствующего разряда третьего информационного входа устройства, четвертый вход первой ячейки второго типа соединен с входом старшего разряда третьего информационного входа устройства.

Цель достигается также тем, что ячейка второго типа содержит одноразрядный сумматор, два элемента И, два элемента ИЛИ, элемент 2И-2ИЛИ и элемент НЕ, причем первый вход ячейки соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ и с первым выходом ячейки, второй вход которой соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым выходом ячейки, третий вход которой соединен с входом переноса одноразрядного сумматора, первый вход которого соединен с четвертым входом ячейки, третий выход которой соединен с выходом второго элемента И, первый вход которого соединен с выходом элемента НЕ и первым входом элемента 2И-2ИЛИ, второй вход которого соединен с выходом суммы одноразрядного сумматора, выход переноса которого соединен с вторым входом элемента И и с третьим входом элемента 2И-2ИЛИ, выход которого соединен с четвертым выходом ячейки, пятый вход которой соединен с четвертым входом элемента 2И-2ИЛИ, с вторым входом второго элемента ИЛИ, с вторым входом первого элемента И, с входом элемента НЕ и с пятым выходом ячейки, шестой вход которой соединен с вторым входом пеpвого элемента ИЛИ, выход которого соединен с вторым входом одноразрядного сумматора.

Предлагаемое матричное устройство для умножения и деления содержит такие отличительные черты, как k ячеек второго типа с соответствующими связями, которые отсутствуют во всех аналогах и благодаря которым достигается положительный эффект - сокращение аппаратурных затрат.

Введение k ячеек второго типа, которые при выполнении операции умножения преобразуют двухрядный код старшей части произведения в однорядный, а при выполнении операции деления используются как знаковые ячейки в каждом ряду, позволяет сократить аппаратурные затраты.

Таким образом, так как в предлагаемом техническом решении имеются отличительные признаки, отсутствующие во всех аналогах и благодаря которым достигается положительный эффект, то техническое решение соответствует критерию "существенные отличия".

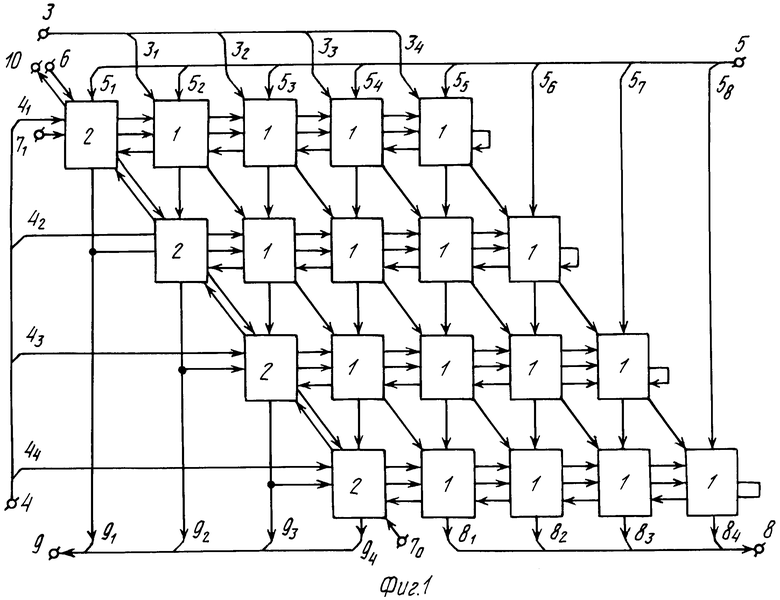

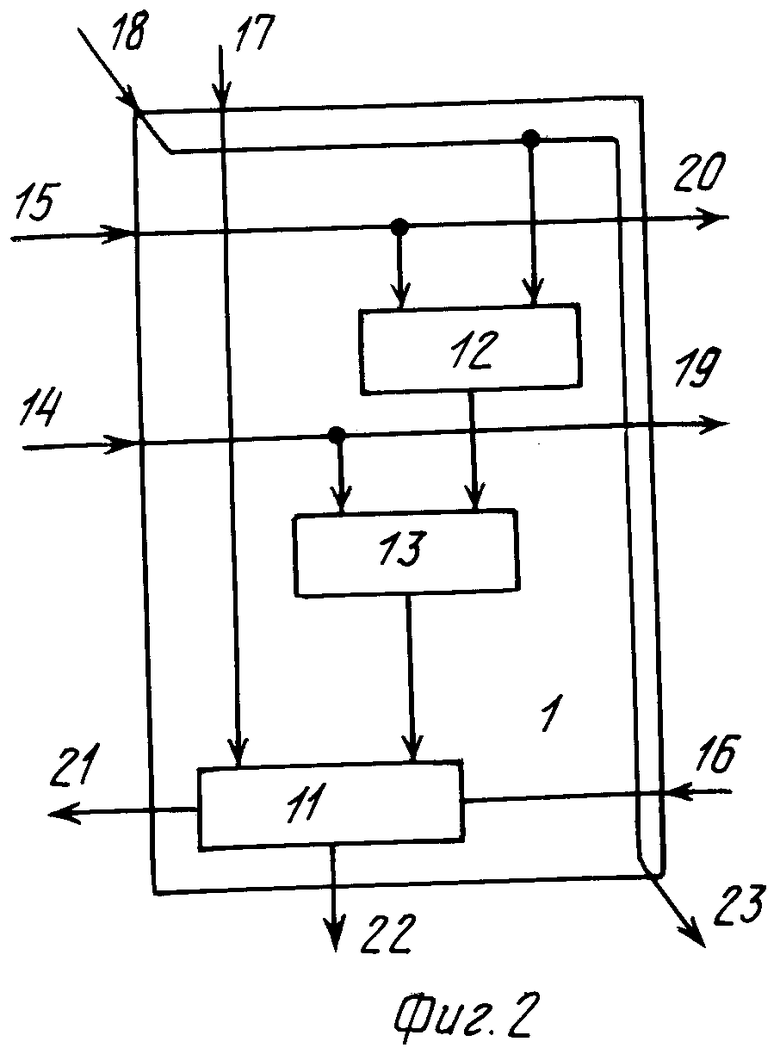

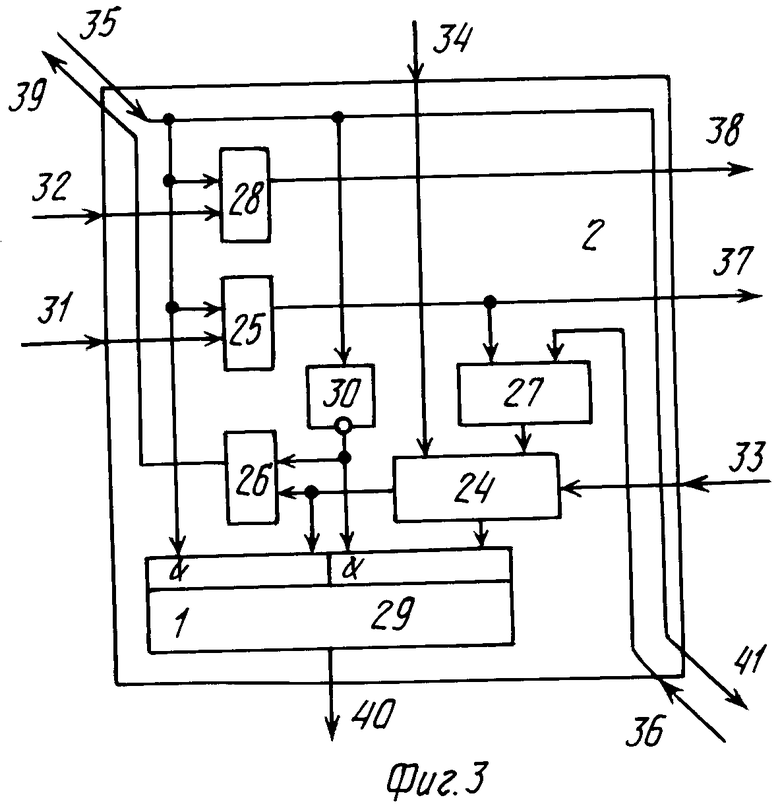

На фиг.1 приведена структурная схема матричного устройства для умножения и деления для конкретного случая m = 4 и k = 4; на фиг.2 - функциональная схема ячейки первого типа матричного устройства для умножения и деления; на фиг. 3 - функциональная схема ячейки второго типа матричного устройства для умножения и деления.

Матричное устройство для умножения и деления (фиг.1) содержит матрицу ячеек 1 первого типа из четырех строк и четырех столбцов и четыре ячейки 2 второго типа, первый 3, второй 4 и третий 5 информационные входы устройства, вход 6 режима работы устройства, входы 70 и 71 уровня логического "0" и уровня логической "1" устройства соответственно, первый 8 и второй 9 выходы устройства и выход 10 переполнения устройства.

Первый и второй выходы i-й ячейки первого типа строк с первой по четвертую (i = 1, 2, 3) соединены с первым и вторым входами (i+1)-й ячейки первого типа этой же строки соответственно, третий выход (i+1)-й ячейки первого типа строк с первой по четвертую соединен с третьим входом i-й ячейки первого типа этой же строки, четвертый выход j-й ячейки первого типа (j = 1, 2, 3) столбцов с второго по m-й соединен с четвертым входом (j+1)-й ячейки первого типа столбцов с первого по третий соответственно, пятый выход j-й ячейки первого типа столбцов с первого по четвертый соединен с пятым входом (j+1)-й ячейки первого типа этого же столбца, пятый вход ячеек первого типа с первой по четвертую первой строки соединен с соответствующим разрядом 31-34 первого информационного входа 3 устройства, первый выход ячеек первого типа с первой по четвертую четвертого столбца соединен с третьим входом этой же ячейки, четвертый выход ячеек первого типа с первой по четвертую четвертой строки соединен с соответствующим разрядом 81-84 первого выхода 8 устройства. Первый и второй выходы ячеек второго типа с первой по четвертую соединены соответственно с первым и вторым входами ячеек первого типа с первой по четвертую первого столбца соответственно, третий выход первой ячейки втрого типа соединен с выходом 10 переполнения устройства, первый вход первой ячейки второго типа соединен с входом 71 уровня логической "1" устройства, второй вход ячеек второго типа с первой по четвертую соединен с соответствующим разрядом 41-44 второго информационного входа 4 устройства, третий вход ячеек второго типа с первой по четвертую соединен с третьим выходом ячеек первого типа с первой по четвертую первого столбца соответственно, четвертый вход ячеек второго типа с второй по четвертую соединен с четвертым выходом ячеек первого типа с первой по третью первого столбца соответственно, пятый выход ячеек второго типа с первой по третью соединен с пятым входом ячеек второго типа с второй по четвертую соответственно, третий выход ячеек второго типа с второй по четвертую соединен с шестым входом ячеек второго типа с первой по третью соответственно, шестой вход четвертой ячейки второго типа соединен с входом 70 логического "0" устройства, четвертый выход ячеек второго типа с первой по третью соединен с первым входом ячеек второго типа с второй по четвертую соответственно с и выходами соответствующих разрядов 91-93второго выхода 9 устройства, пятый вход первой ячейки второго типа соединен с входом 6 режима работы устройства, четвертый выход четвертой ячейки второго типа соединен с выходом младшего разряда 94 второго выхода 9 устройства. Четвертый вход ячейки первого типа первой строки и четвертого столбца соединен с входом соответствующего разряда 52-56третьего информационного входа 5 устройства, четвертый вход первой ячейки второго типа соединен с входом старшего разряда 51 третьего информационного входа 5 устройства.

Ячейка первого типа (фиг.2) содержит одноразрядный сумматор 11, элемент И 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, входы 14-18 с первого по пятый соответственно и выходы 19-23 с первого по пятый соответственно.

Ячейка второго типа (фиг.3) содержит одноразрядный сумматор 24, первый 25 и второй 26 элементы И, первый 27 и второй 28 элементы ИЛИ, элемент 2И-2ИЛИ 29, элемент НЕ 30, входы 31-36 с первого по шестой соответственно и выходы 37-41 с первого по пятый соответственно.

Ячейка 1 предназначена для выполнения разрядных операций в составе матричного устройства для умножения и деления. Так, при выполнении операции умножения в ячейке 1 осуществляются умножение разряда множителя, поступающего по входу 15 ячейки 1, на разряд множимого, поступающий по входу 18 ячейки 1, и подсуммирование полученного разряда частичного произведения, транзитом проходящего через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 (так как на входе 14 ячейки 1 установлен уровень логического "0"), на одноразрядном сумматоре 11 к разряду суммы частичного произведения, поступающему по входу 17 ячейки 1, с учетом переноса, поступающего по входу 16 ячейки 1 из ячейки, обрабатывающей соседний младший разряд. Результат суммирования поступает в виде значения суммы и переноса на выходы 22 и 21 ячейки 1 соответственно. При выполнении операции деления (используется метод деления без восстановления остатка) в ячейке 1 осуществляется определение разряда нового остатка. Этот разряд получается путем прибавления разряда делителя, поступающего по входу 18 ячейки 1, транзитом проходящего через элемент И 12 (так как на входе 15 ячейки 1 установлен уровень логической "1") и проинвертированного на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 13 (если на входе 14 ячейки 1 установлен уровень логической "1", в противном случае разряд делителя не преобразовывается), к разряду предыдущего остатка, поступающему по входу 16 ячейки 1, на одноразрядном сумматоре 11 с учетом переноса, поступающего по входу 16 ячейки 1 из ячейки, обрабатывающей соседний младший разряд. Результат этого суммирования поступает в виде значения суммы и переноса на выходы 22 и 21 ячейки 1 соответственно.

Ячейка 2 предназначена для формиpования управляющих сигналов для ячеек 1, а также выполнения операций над старшими разрядами в составе матричного устройства для умножения и деления. Так, при выполнении операции умножения ячейка 2 предназначена для формирования на ее выходе 37 уровня логического "0" для передачи на выход 38 ячейки 2 разряда множителя, поступающего на ее вход 32, для приведения переносов в старшей части произведения, сформиpованной в двухрядном коде в виде разрядов сумм и переносов по входам 34 и 33 ячеек 2. Результат приведения переносов в каждой ячейке 2 поступает в виде значения суммы и переноса на ее выходы 40 и 39 соответственно. При выполнении операции деления ячейка 2 предназначена для формирования на ее выходе 40 разряда частного, равного значению переноса одноразрядного сумматора 24 ячейки 2, на выходе 37 ячейки 2 разряда частного, полученного на предыдущей строке матрицы (либо уровня логической "1" для первой строки), на выходе 38 ячейки 2 - уровня логической "1".

Для определенности работу матричного устройства для умножения и деления рассмотрим на примере реализации устройства, приведенном на фиг.1 для m = 4 и k = 4.

При умножении (на входе 6 режима работы устройства установлен уровень логического "0") на вход 3 поступает четырехразрядное множимое Х1Х2Х3Х4, на вход 4 - четырехразрядный множитель Y1Y2Y3Y4, а на вход 5 можно подать восьмиразрядное слагаемое ZoZ1Z2Z3Z4Z5Z6Z7. Умножение выполняется, начиная

со старших разрядов множителя, при этом на первой строке ячеек 1 выполняется умножение множимого Х1Х2Х3Х4 на старший разряд множителя Y1 и производится сложение получившегося частичного произведения с разрядами Z1Z2Z3Z4, на второй строке ячеек 1 выполняется умножение множимого Х1Х2Х3Х4 на разряд множителя Y2 и производится сложение получившегося частичного произведения с результатом сложения, поступающим с выходов сумм ячеек 1 с второй по четвертую первой строки и разрядом Z5, на третьей строке ячеек 1 выполняется умножение множимого Х1Х2Х3Х4 на разряд множителя Y3 и производится сложение получившегося частичного произведения с результатом сложения, поступающим с выходов сумм ячеек 1 с второй по четвертую второй строки и разрядом Z6, на четвертой строке ячеек 1 выполняется умножение множимого X1Х2Х3Х4 на разряд множителя Y4 и производится сложение получившегося частичного произведения с результатом сложения, поступающим с выходов сумм ячеек 1 с второй по четвертую третьей строки, и разрядом Z7, на ячейках 2 производится приведение переносов в старшей части произведения, сформированной в двухрядном коде и поступающей в виде сумм и переносов с выходов 22 и 21 ячеек 1 первого столбца с учетом разряда Zо. В результате на выходах 10, 9 и 8 формируется произведение

P = X1X2X3X4 * Y1Y2Y3Y4 +

+ ZoZ1Z2Z3Z4Z5Z6Z7, четыре младших разряда которого поступают на выход 8 с выходов 22 ячеек 1 четвертой строки, четыре старших разряда - на выход 9 с выходов 40 ячеек 2, а сигнал переполнения - на выход 10 переполнения устройства.

При делении (на входе 6 режима работы устройства установлен уровень логической "1") на вход 3 поступает четырехразрядный делитель 0, Х1Х2Х3Х4, на вход 5 - восьмиразрядное делимое Zo, Z1Z2Z3Z4Z5Z6Z7. Предполагается, что делитель является нормализованной положительной дробью, а делимое меньше или равно удвоенному делителю.

Так как на входе 7 устройства присутствует уровень логической "1", то в первой строке ячеек 1 и в первой ячейке 2 из делимого вычитается делитель (в устройстве вычитание делителя из делимого или очередного остатка заменяется сложением с дополнительным кодом делителя). На выходе 40 первой ячейки 2 формируется старший разряд частного, а на выходах 22 ячеек 1 первой строки - разряды очередного остатка, который поступает на входы 17 ячеек 1 второй строки и к которому прибавляется прямой или дополнительный код делителя в зависимости от значения сигнала на выходе 40 первой ячейки 2. Если сигнал на выходе 40 равен единице, то прибавляется дополнительный код делителя, в противном случае - прямой.

На выходе 40 второй ячейки 2 формируется второй разряд частного, а на выходах 22 ячеек 1 второй строки - разряды очередного остатка, и т.д. В итоге на выходах 40 ячеек 2 с первой по четвертую формируются четыре разряда частного, а на выходах 22 ячеек 1 четвертой строки - четыре разряда остатка, причем знаковый разряд остатка формиpуется на выходе 40 четвертой ячейки 2, при это положительному остатку соответствует уровень логической "1", а отрицательному - уровень логического "0".

Произведем сравнение предлагаемого и известного устройств по аппаратурным затратам.

Для выполнения деления восьмиразрядного делимого на четырехразрядный делитель в известном устройстве требуется 24 ячейки первого типа (матрица 6*4 ячеек первого типа) и 16 элементов типа И, ИЛИ. В предлагаемом устройстве для этого случая требуется 16 ячеек первого типа и четыре ячейки второго типа (см. фиг.1). Так как ячейка второго типа по аппаратурным затратам соответствует ячейке первого типа плюс четыре элемента типа И, ИЛИ, НЕ, то в предлагаемом устройстве требуется количество аппаратуры, равное аппаратуре 20-и ячеек первого типа и 16-и элементов типа И, ИЛИ, НЕ. Следовательно, для построения предлагаемого устройства требуется меньше аппаратуры, чем для известного на величину, равную количеству аппаратуры четырех ячеек первого типа.

Для выполнения умножения четырехразрядного множимого на четырехразрядный множитель в известном и предлагаемом устройствах требуется равное количество аппаратуры. Отметим, что в известном устройстве на аппаратуре, необходимой для выполнения умножения четырехразрядного множимого на четырехразрядный множитель, можно выполнить деление только семиразрядного делимого на трехразрядный делитель, а в предлагаемом (при тех же условиях) - выполнить деление восьмиразрядного делимого на четырехразрядный делитель. Таким образом, в предлагаемом матричном устройстве для умножения и деления сокращаются аппаратурные затраты.

Технико-экономическое преимущество предлагаемого матричного устройства для умножения и деления по сравнению с устройством-прототипом заключается в сокращении аппаратурных затрат примерно на 16%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операций умножения и деления чисел. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит матрицу ячеек двух типов. Введение ячеек второго типа с соответствующими связями обеспечивает положительный эффект, заключающийся в сокращении аппаратурных затрат. 1 з.п. ф-лы, 3 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1024910A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1991-07-03—Подача