Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Целью изобретения является повышение быстродействия устройства.

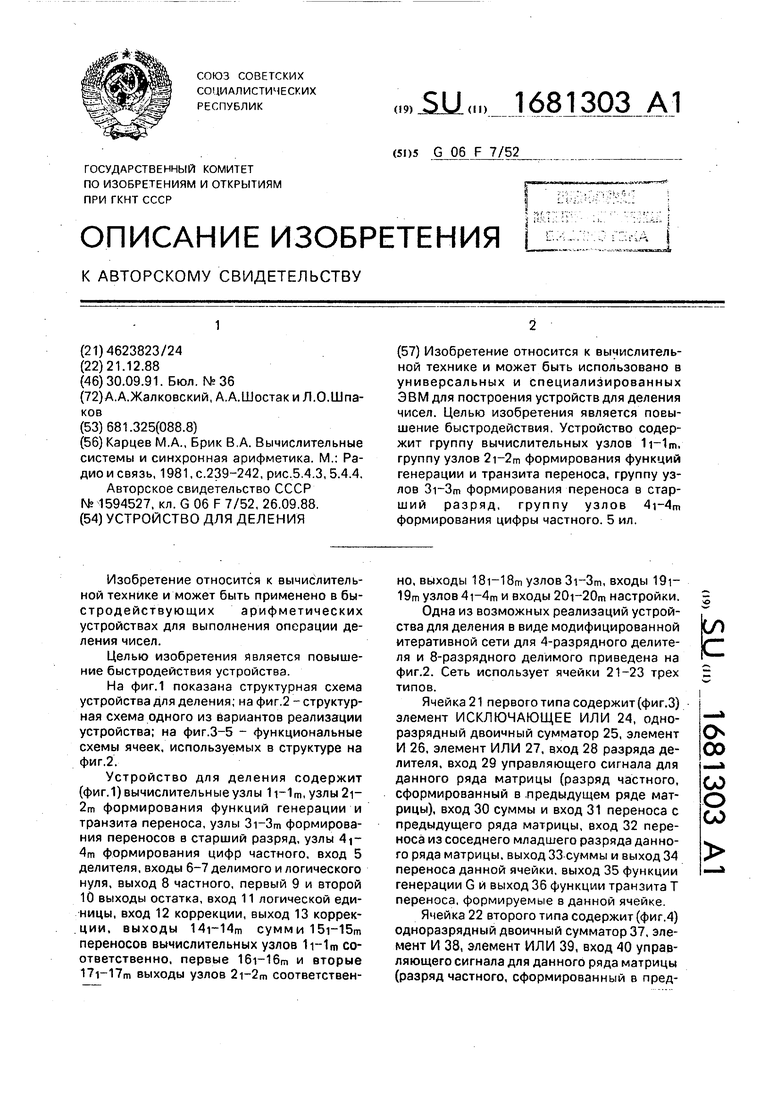

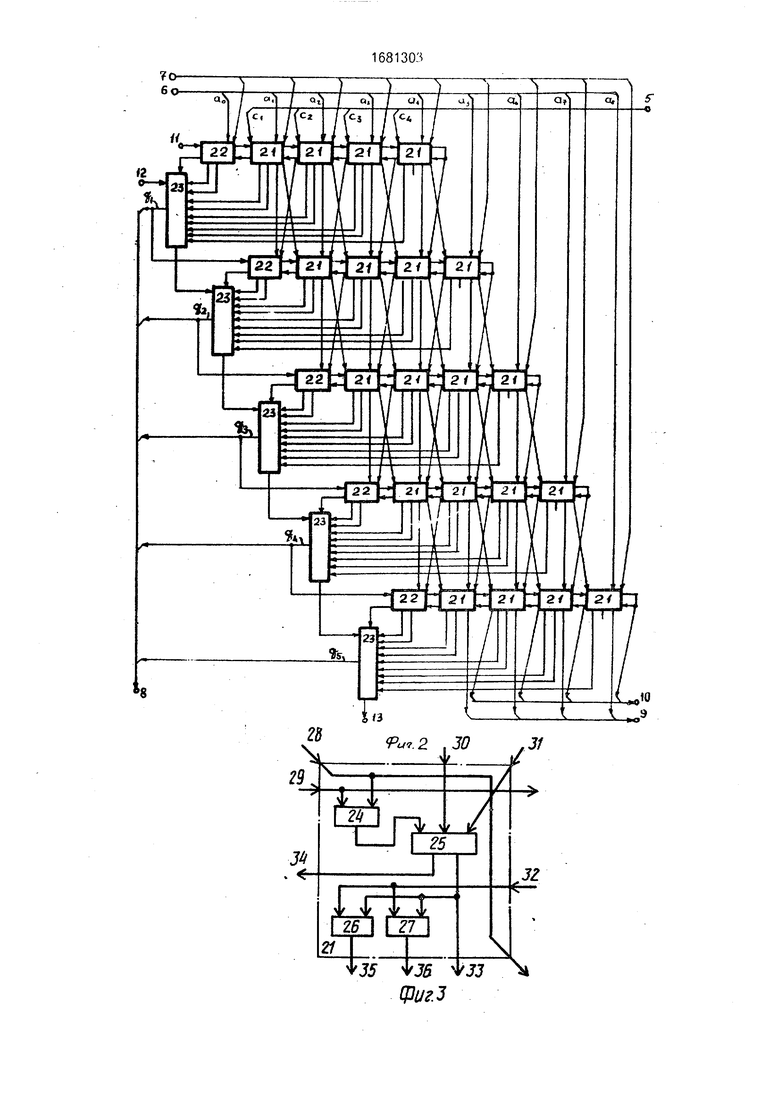

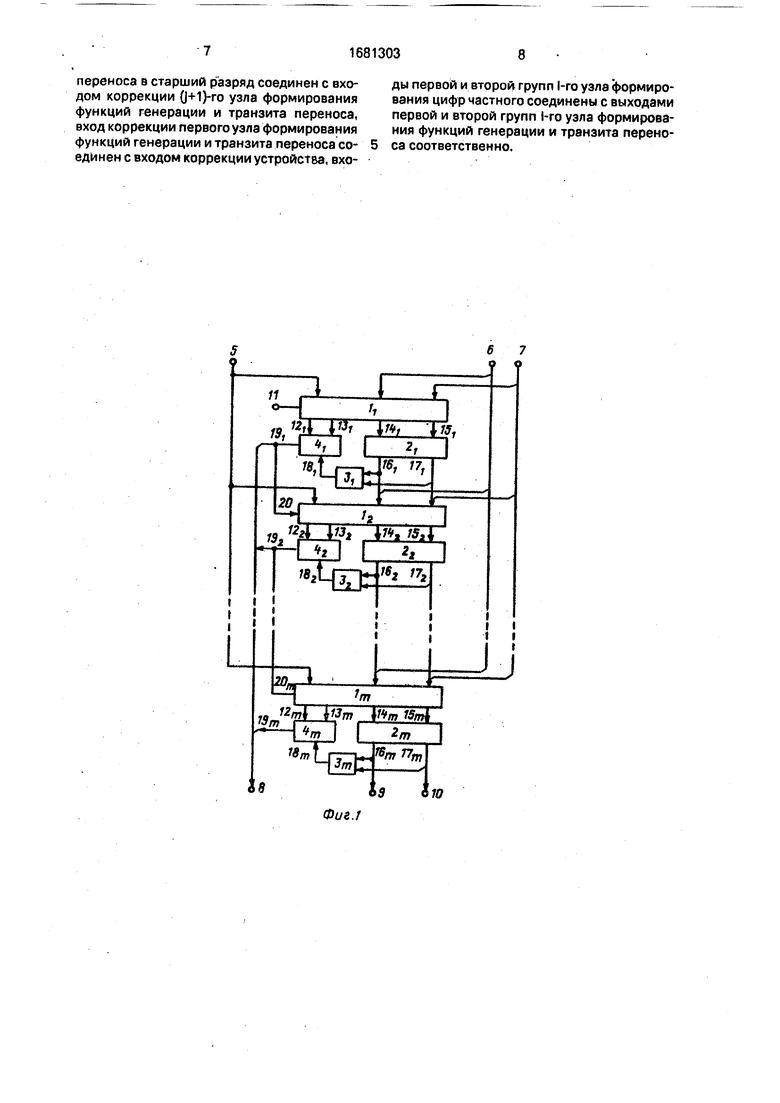

На фиг.1 показана структурная схема устройства для деления; на фиг.2 - структурная схема одного из вариантов реализации устройства; на фиг.3-5 - функциональные схемы ячеек, используемых в структуре на фиг.2.

Устройство для деления содержит (фиг.вычислительныеузлы 1i-1m, узлы21- 2т формирования функций генерации и транзита переноса, узлы 3i-3m формирования переносов в старший разряд, узлы 4т формирования цифр частного, вход 5 делителя, входы 6-7 делимого и логического нуля, выход 8 частного, первый 9 и второй 10 выходы остатка, вход 11 логической единицы, вход 12 коррекции, выход 13 коррекции, выходы 14i-14m сумми 15i-15m переносов вычислительных узлов 1i-1m соответственно, первые 16i-16m и вторые 17i-17m выходы узлов 2i-2m соответственно, выходы 18i-18m узлов 3i-3m, входы 19i 19m узлов 4i-4m и входы 20i-20m настройки.

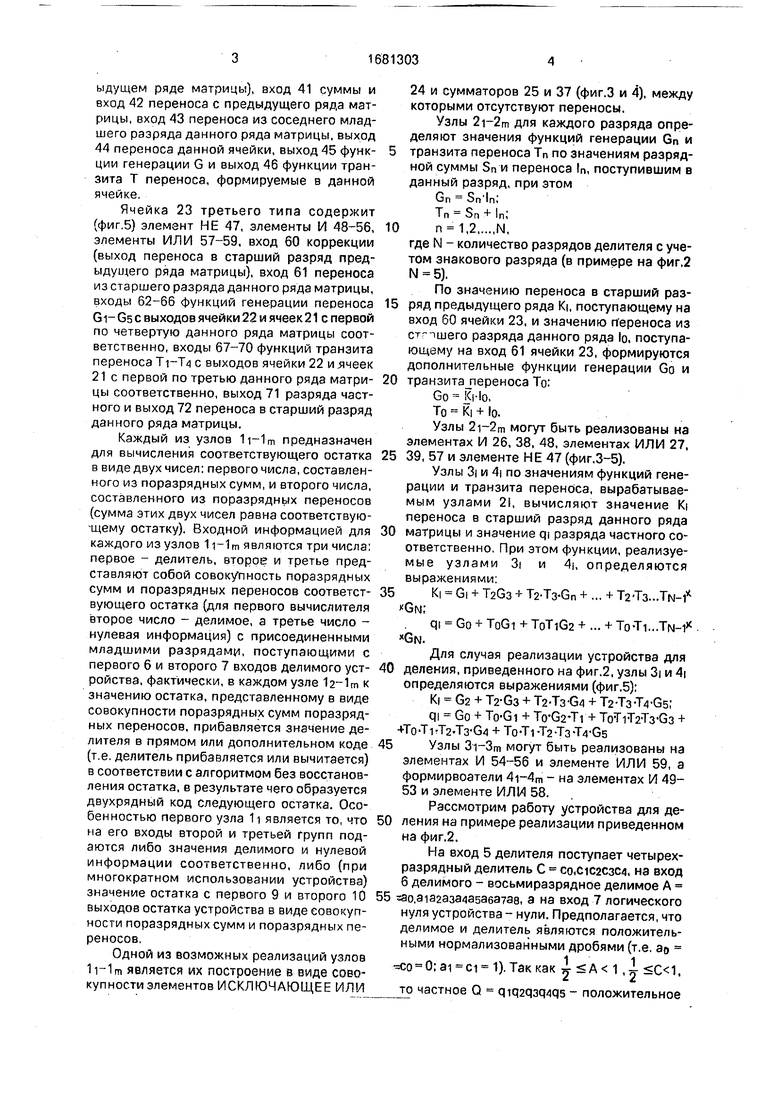

Одна из возможных реализаций устройства для деления в виде модифицированной итеративной сети для 4-разрядного делителя и 8-разрядного делимого приведена на фиг.2. Сеть использует ячейки 21-23 трех типов.

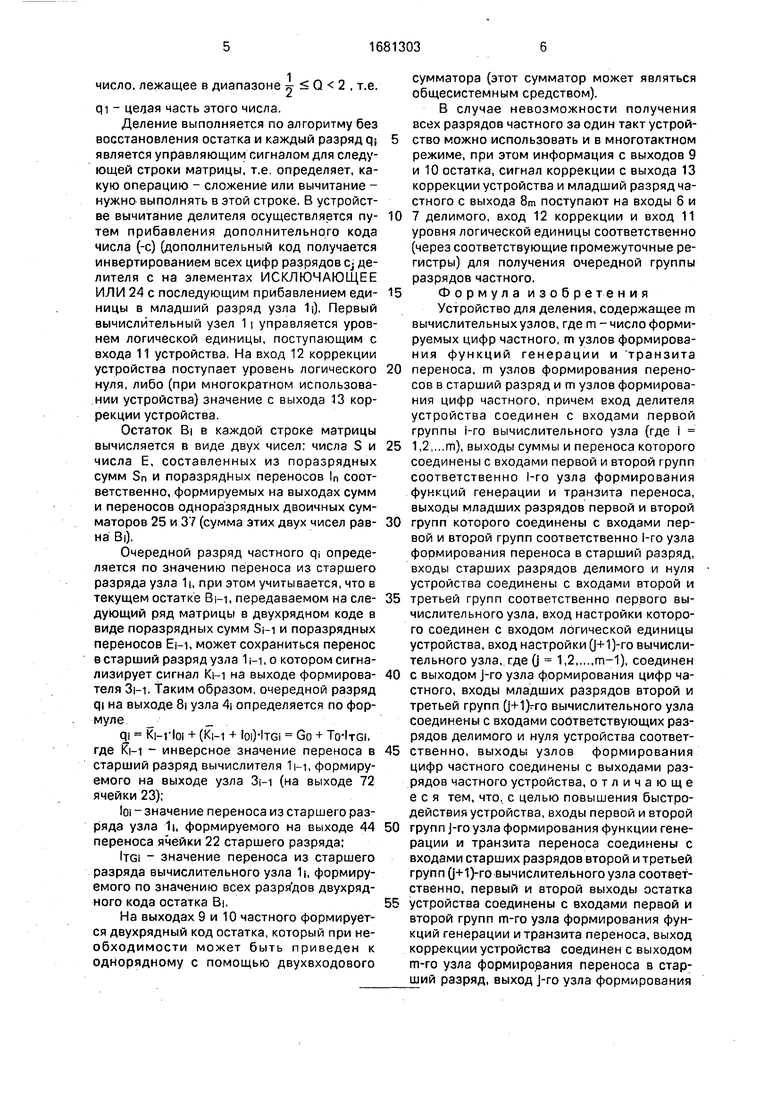

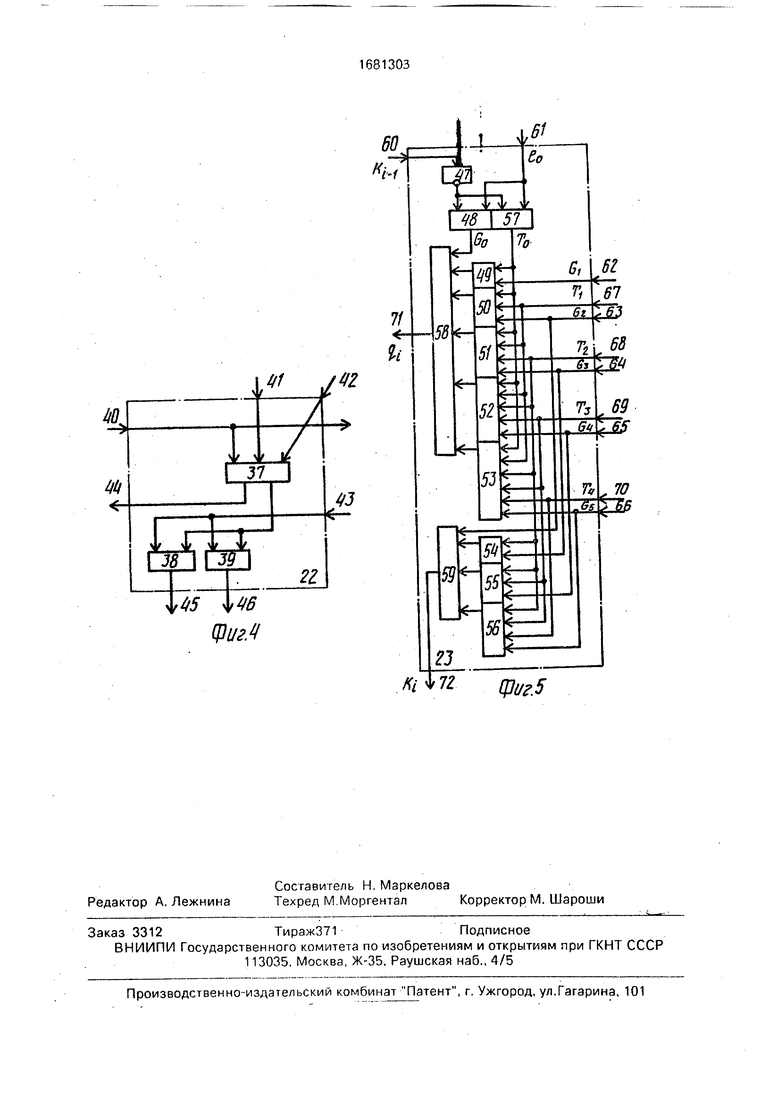

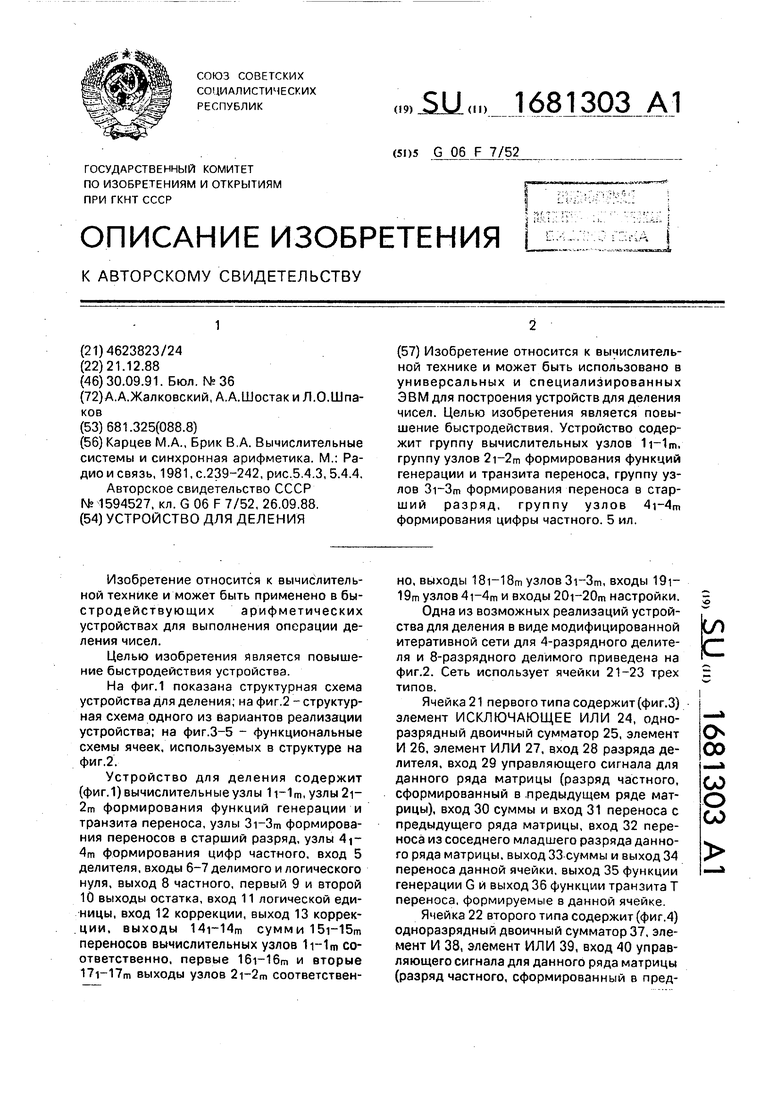

Ячейка 21 первого типа содержит (фиг.З) элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 24, одноразрядный двоичный сумматор 25, элемент И 26, элемент ИЛИ 27, вход 28 разряда делителя, вход 29 управляющего сигнала для данного ряда матрицы (разряд частного, сформированный в .предыдущем ряде матрицы), вход 30 суммы и вход 31 переноса с предыдущего ряда матрицы, вход 32 переноса из соседнего младшего разряда данного ряда матрицы, выход 33 суммы и выход 34 переноса данной ячейки, выход 35 функции генерации G и выход 36 функции транзита Т переноса, формируемые в данной ячейке.

Ячейка 22 второго типа содержит (фиг.4) одноразрядный двоичный сумматор 37, элемент И 38, элемент ИЛИ 39, вход 40 управляющего сигнала для данного ряда матрицы (разряд частного, сформированный в пред(Л

С

о

00

со о

СА)

ыдущем ряде матрицы), вход 41 суммы и вход 42 переноса с предыдущего ряда матрицы, вход 43 переноса из соседнего младшего разряда данного ряда матрицы, выход 44 переноса данной ячейки, выход 45 функции генерации G и выход 46 функции транзита Т переноса, формируемые в данной ячейке.

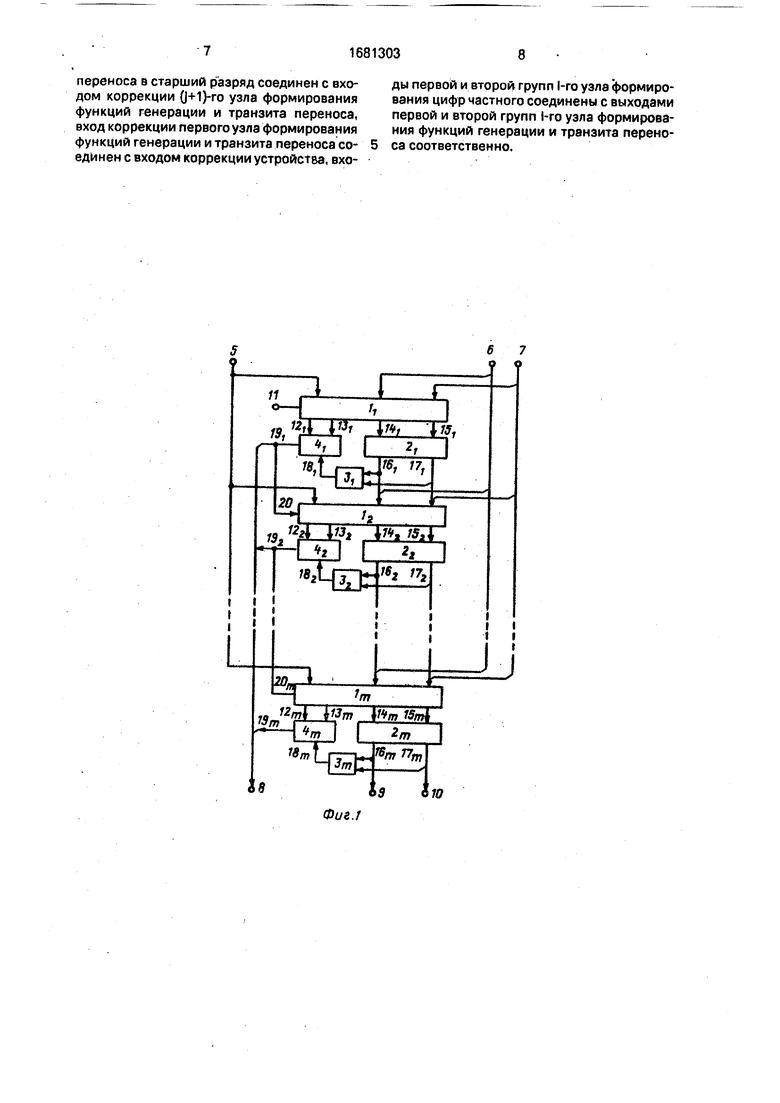

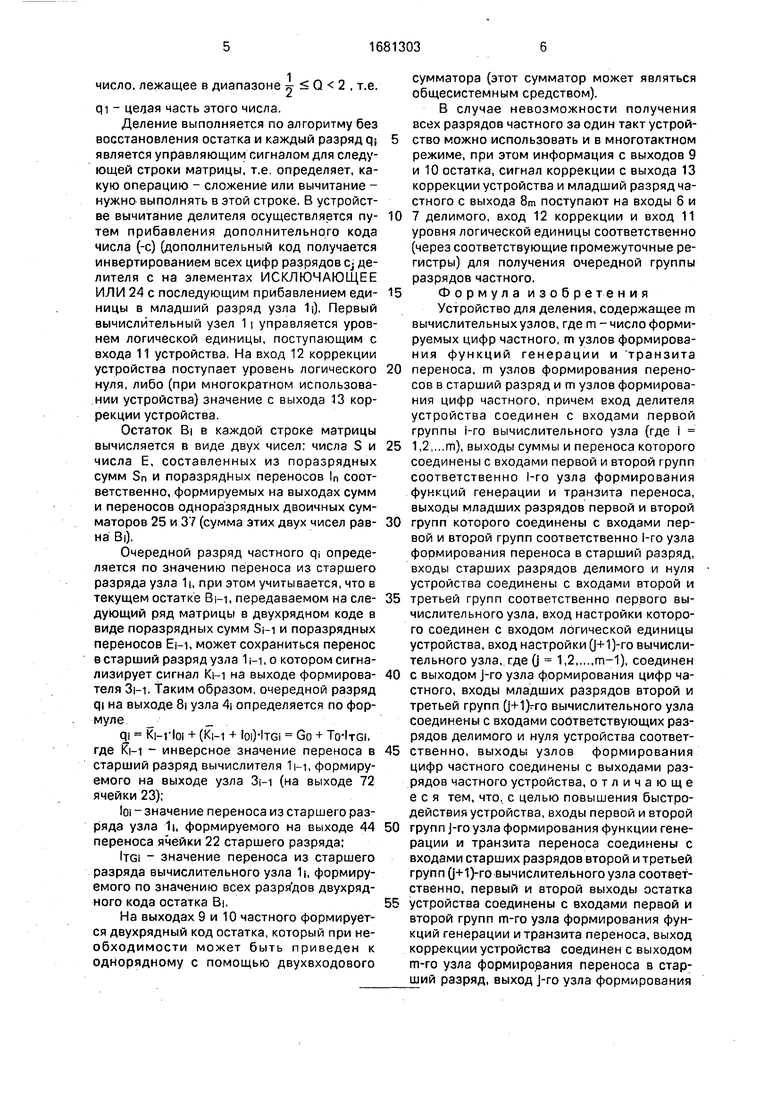

Ячейка 23 третьего типа содержит (фиг.5) элемент НЕ 47, элементы И 48-56, элементы ИЛИ 57-59, вход 60 коррекции (выход переноса в старший разряд предыдущего ряда матрицы), вход 61 переноса из старшего разряда данного ряда матрицы, входы 62-66 функций генерации переноса Gi- Gs с выходов ячейки 22 и ячеек 21 с первой по четвертую данного ряда матрицы соответственно, входы 67-70 функций транзита переноса Ti-T4 с выходов ячейки 22 и ячеек 21 с первой по третью данного ряда матрицы соответственно, выход 71 разряда частного и выход 72 переноса в старший разряд данного ряда матрицы.

Каждый из узлов 1i-1m предназначен для вычисления соответствующего остатка в виде двух чисел: первого числа, составленного из поразрядных сумм, и второго числа, составленного из поразрядных переносов (сумма этих двух чисел равна соответствую- -щему остатку). Входной информацией для каждого из узлов 1 являются три числа: первое - делитель, второе и третье представляют собой совокупность поразрядных сумм и поразрядных переносов соответствующего остатка(для первого вычислителя второе число - делимое, а третье число - нулевая информация) с присоединенными младшими разрядами, поступающими с первого 6 и второго 7 входов делимого устройства, фактически, в каждом узле к значению остатка, представленному в виде совокупности поразрядных сумм поразрядных переносов, прибавляется значение делителя в прямом или дополнительном коде (т.е. делитель прибавляется или вычитается) в соответствии с алгоритмом без восстановления остатка, в результате чего образуется двухрядный код следующего остатка. Особенностью первого узла 1i является то, что на его входы второй и третьей групп подаются либо значения делимого и нулевой информации соответственно, либо (при многократном использовании устройства) значение остатка с первого 9 и второго 10 выходов остатка устройства в виде совокупности поразрядных сумм и поразрядных переносов.

Одной из возможных реализаций узлов 1i-1m является их построение в виде совокупности элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

24 и сумматоров 25 и 37 (фиг.З и 4), между которыми отсутствуют переносы.

Узлы 2i-2m для каждого разряда определяют значения функций генерации Gn и транзита переноса Тп по значениям разрядной суммы Sn и переноса In, поступившим в данный разряд, при этом

Gn Sn lrii

тп sn + in;

л 1,2N,

где N - количество разрядов делителя с учетом знакового разряда (в примере на фиг.2 N 5).

По значению переноса в старший раз- ряд предыдущего ряда К|, поступающему на вход 60 ячейки 23, и значению п ереноса из ст-пшего разряда данного ряда lo, поступающему на вход 61 ячейки 23, формируются дополнительные функции генерации Go и транзита переноса То: , То Ki + lo.

Узлы 2i-2m могут быть реализованы на элементах И 26, 38, 48, элементах ИЛИ 27, 39, 57 и элементе НЕ 47 (фиг.3-5).

Узлы 3) и 4| по значениям функций генерации и транзита переноса, вырабатываемым узлами 2i, вычисляют значение К| переноса в старшим разряд данного ряда матрицы и значение qi разряда частного соответственно. При этом функции, реализуемые узлами 3i и 4|, определяются выражениями.

Ki Gi + Т2Сз + Та-Тз-Gn +... + Та-Тз-Ты-г GN;

qt Go + ToGt + ToTiG2 + ... + TO-TI...TN-I

GN.

Для случая реализации устройства для деления, приведенного на фиг.2, узлы 3i и 4| определяются выражениями (фиг.5):

К| G2 + T2-G3 + T2-T3-G4 + T2-T3-T4-G5;

qi Go + To-Gi + To G2 Ti + ТоТ гТз-Сз +

4TO Tl-T2.T3 G4 + To-TlT2-T3-T4-G5

Узлы могут быть реализованы на элементах И 54-56 и элементе ИЛИ 59, а формирвоатели 4i-4m - на элементах И 49- 53 и элементе ИЛИ 58.

Рассмотрим работу устройства для деления на примере реализации приведенном на фиг.2.

На вход 5 делителя поступает четырехразрядный делитель С co,ciC2C3C4, на вход 6 делимого - восьмиразрядное делимое А

530,3132333435363738, а на вход 7 логического нуля устройства - нули. Предполагается, что делимое и делитель являются положительными нормализованными дробями (т.е. ао

co 0;ai ci 1). Так как i A 1 ,j , то частное Q qiq2qsq4qs - положительное

число, лежащее в диапазоне - Q 2 , т.е.

qi - целая часть этого числа.

Деление выполняется по алгоритму без восстановления остатка и каждый разряд QJ является управляющим сигналом для следующей строки матрицы, т.е. определяет, какую операцию - сложение или вычитание - нужно выполнять в этой строке. В устройстве вычитание делителя осуществляется пу- тем прибавления дополнительного кода числа (-с) (дополнительный код получается инвертированием всех цифр разрядов Cj делителя с на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 24 с последующим прибавлением еди- ницы в младший разряд узла 1|). Первый вычислительный узел 11 управляется уровнем логической единицы, поступающим с входа 11 устройства. На вход 12 коррекции устройства поступает уровень логического нуля, либо (при многократном использовании устройства) значение с выхода 13 коррекции устройства.

Остаток Bi в каждой строке матрицы вычисляется в виде двух чисел: числа S и числа Е, составленных из поразрядных сумм Sn и поразрядных переносов п соответственно, формируемых на выходах сумм и переносов одноразрядных двоичных сумматоров 25 и 37 (сумма этих двух чисел рав- на Bi).

Очередной разряд частного QI определяется по значению переноса из старшего разряда узла 1i, при этом учитывается, что в текущем остатке Вм, передаваемом на еле- дующий ряд матрицы в двухрядном коде в виде поразрядных сумм 5м и поразрядных переносов Еы, может сохраниться перенос в старший разряд узла 1м. о котором сигнализирует сигнал Км на выходе формирова- теля Зм. Таким образом, очередной разряд qi на выходе 8i узла А определяется по формуле

qi Ki-rloi + (Км + loO-lTGi Go + TO-ITGI, где - инверсное значение переноса в старший разряд вычислителя 1м, формируемого на выходе узла Зм (на выходе 72 ячейки 23);

Id - значение переноса из старшего разряда узла 1|, формируемого на выходе 44 переноса ячейки 22 старшего разряда;

ITGI - значение переноса из старшего разряда вычислительного узла 1j, формируемого по значению всех разря дов двухрядного кода остатка В|.

На выходах 9 и 10 частного формируется двухрядный код остатка, который при необходимости может быть приведен к однорядному с помощью двухвходового

сумматора (этот сумматор может являться общесистемным средством).

В случае невозможности получения всех разрядов частного за один такт устройство можно использовать и в многотактном режиме, при этом информация с выходов 9 и 10 остатка, сигнал коррекции с выхода 13 коррекции устройства и младший разряд частного с выхода 8т поступают на входы 6 и 7 делимого, вход 12 коррекции и вход 11 уровня логической единицы соответственно (через соответствующие промежуточные регистры) для получения очередной группы разрядов частного.

Формула изобретения Устройство для деления, содержащее m вычислительныхузлов, где m - число формируемых цифр частного, m узлов формирова- ния функций генерации и транзита переноса, m узлов формирования переносов в старший разряд и m узлов формирования цифр частного, причем вход делителя устройства соединен с входами первой группы i-ro вычислительного узла (где i 1,2,...m), выходы суммы и переноса которого соединены с входами первой и второй групп соответственно 1-го узла формирования функций генерации и транзита переноса, выходы младших разрядов первой и второй групп которого соединены с входами первой и второй групп соответственно 1-го узла формирования переноса в старший разряд, входы старших разрядов делимого и нуля устройства соединены с входами второй и третьей групп соответственно первого вычислительного узла, вход настройки которого соединен с входом логической единицы устройства, вход настройки Q+1)-ro вычислительного узла, где 0 1.2т-1). соединен

с выходом j-ro узла формирования цифр частного, входы младших разрядов второй и третьей групп (j+1)rro вычислительного узла соединены с входами соответствующих разрядов делимого и нуля устройства соответственно, выходы узлов формирования цифр частного соединены с выходами разрядов частного устройства, отличающе е с я тем, что, с целью повышения быстродействия устройства,входы первой и второй групп j-ro узла формирования функции генерации и транзита переноса соединены с входами старших разрядов второй и третьей групп (j+1)-ro вычислительного узла соответственно, первый и второй выходы остатка устройства соединены с входами первой и второй групп m-ro узла формирования функций генерации и транзита переноса, выход коррекции устройства соединен с выходом т-го узла формирования переноса в старший разряд, выход j-ro узла формирования

переноса в старший разряд соединен с входом коррекции узла формирования функций генерации и транзита переноса, вход коррекции первого узла формирования функций генерации и транзита переноса соединен с входом коррекции устройства, входы первой и второй групп 1-го узла формирования цифр частного соединены с выходами первой и второй групп 1-го узла формирования функций генерации и транзита переноса соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1683009A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения устройств для деления чисел. Целью изобретения является повышение быстродействия. Устройство содержит группу вычислительных узлов 1i-1m, группу узлов 2i-2m формирования функций генерации и транзита переноса, группу узлов формирования переноса в старший разряд, группу узлов 4i-4m формирования цифры частного. 5 ил.

35 +J6 JJ фиг.З

ЪЬП щиг5

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с.239-242, рис.5.4.3,5.4.4 | |||

| Устройство для деления | 1988 |

|

SU1594527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-30—Публикация

1988-12-21—Подача