Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах.

Целью изобретения является повышение достоверности работы устройства

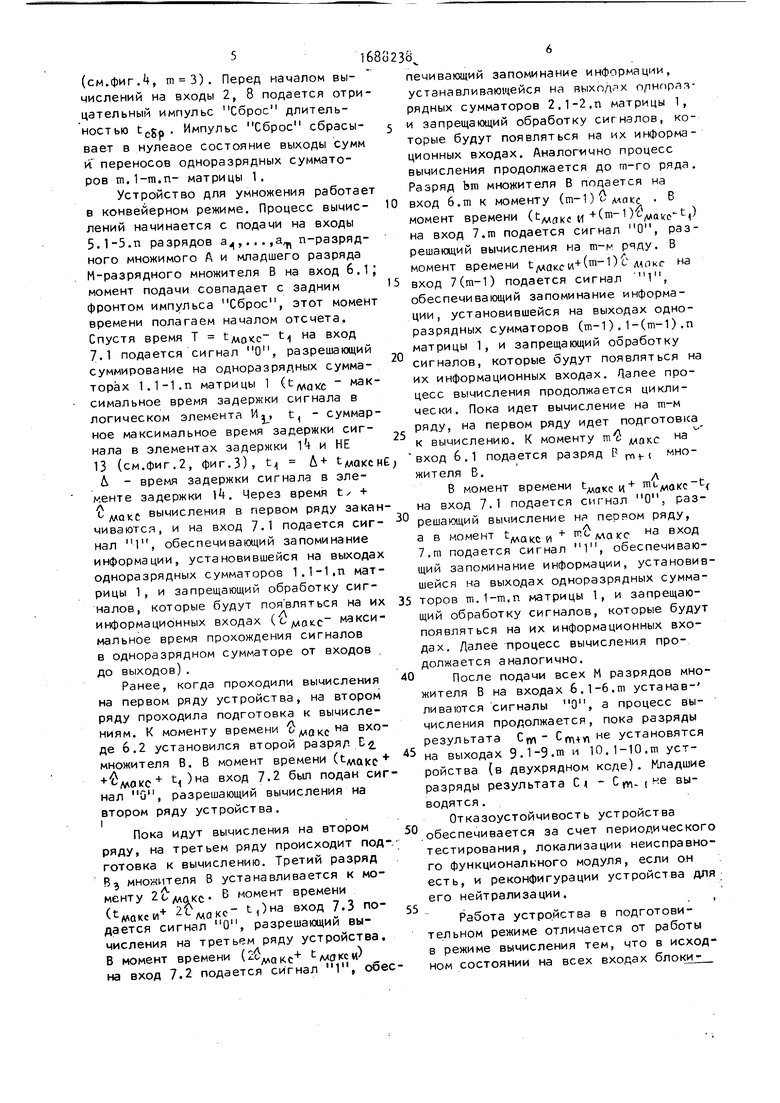

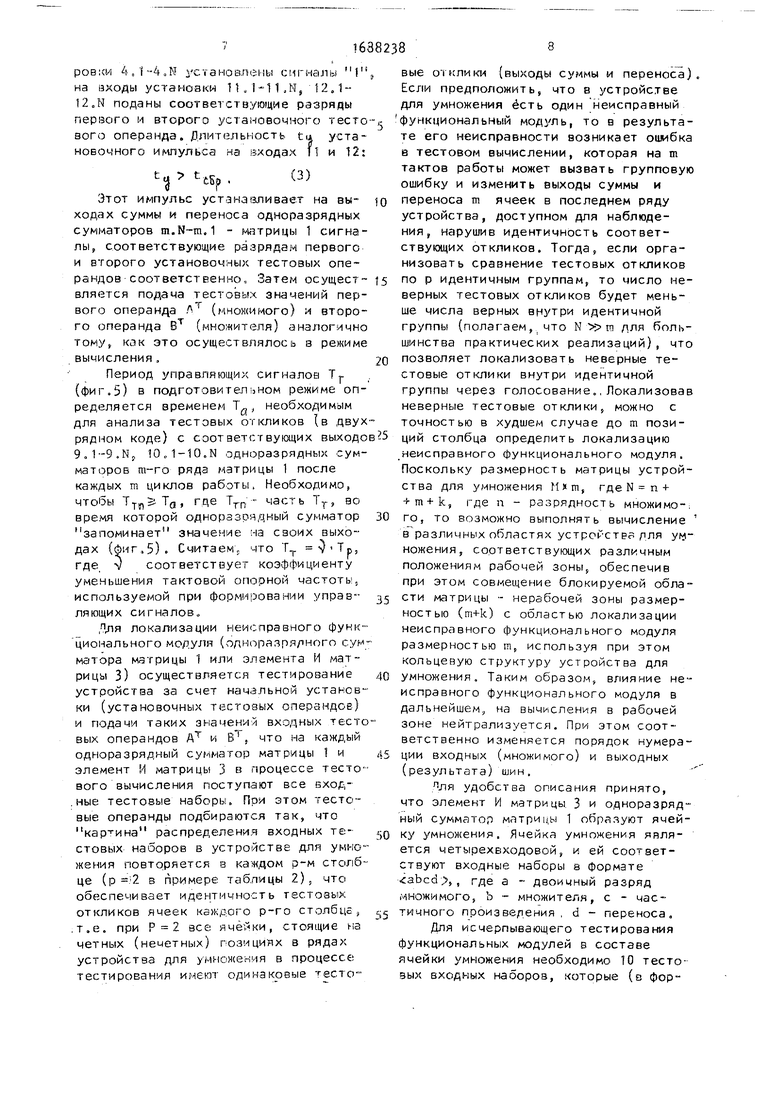

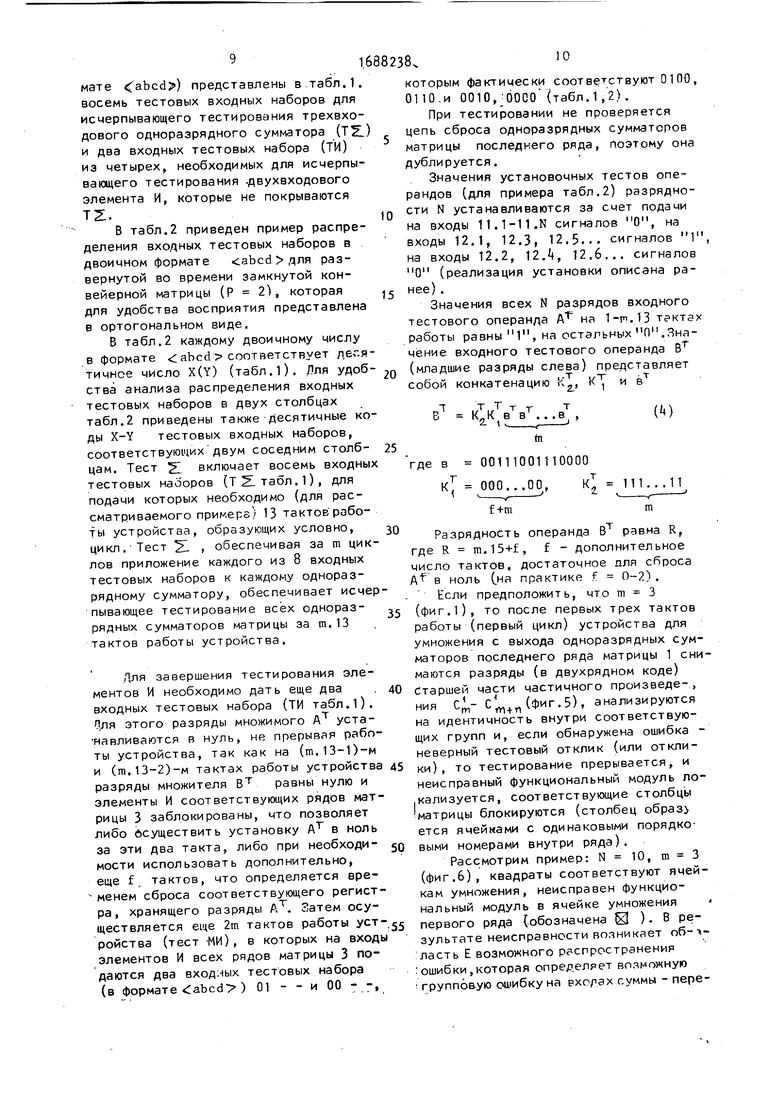

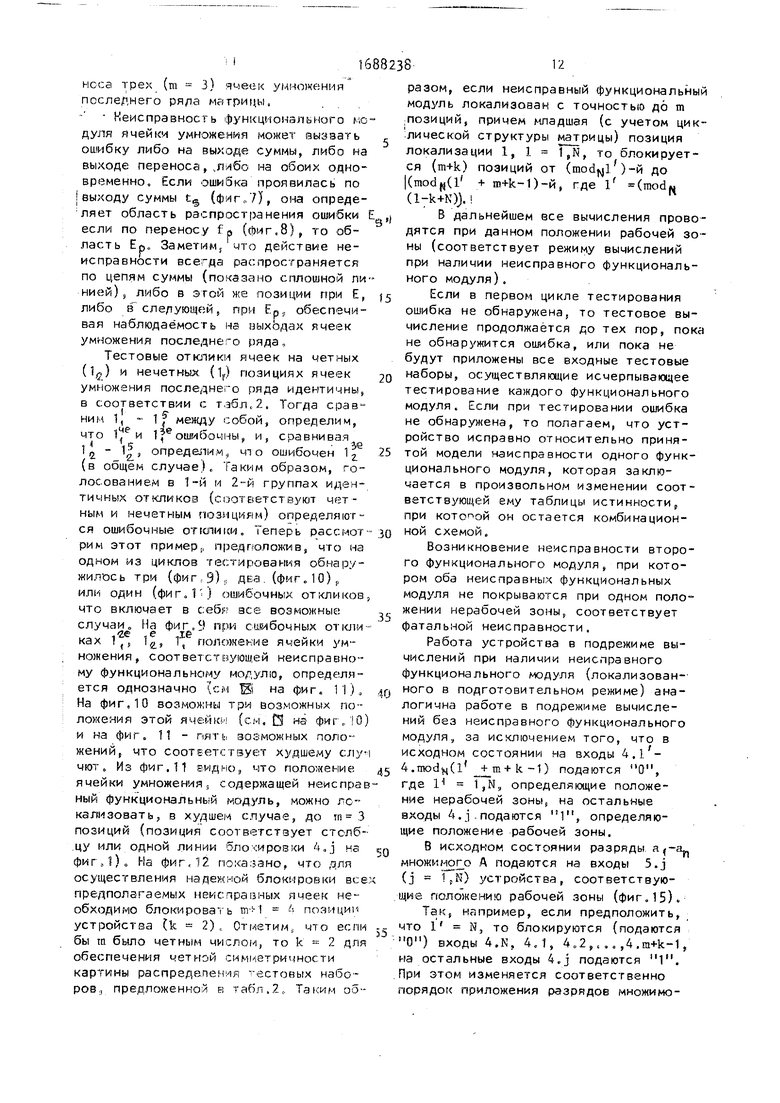

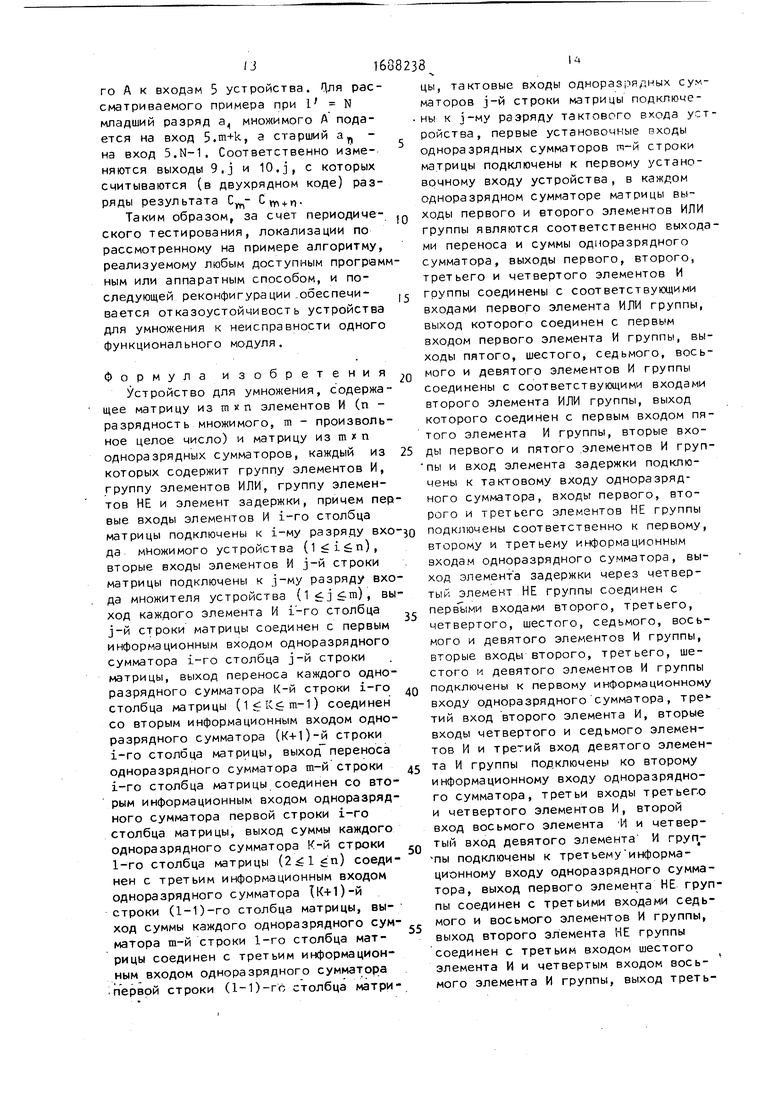

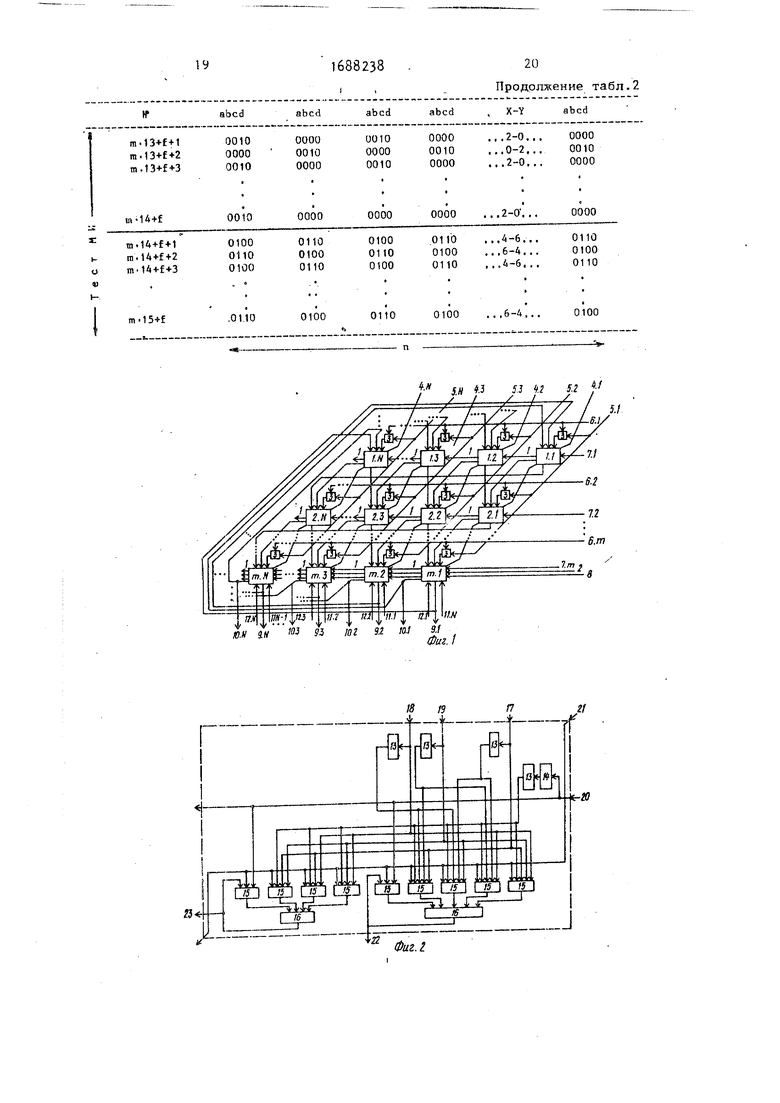

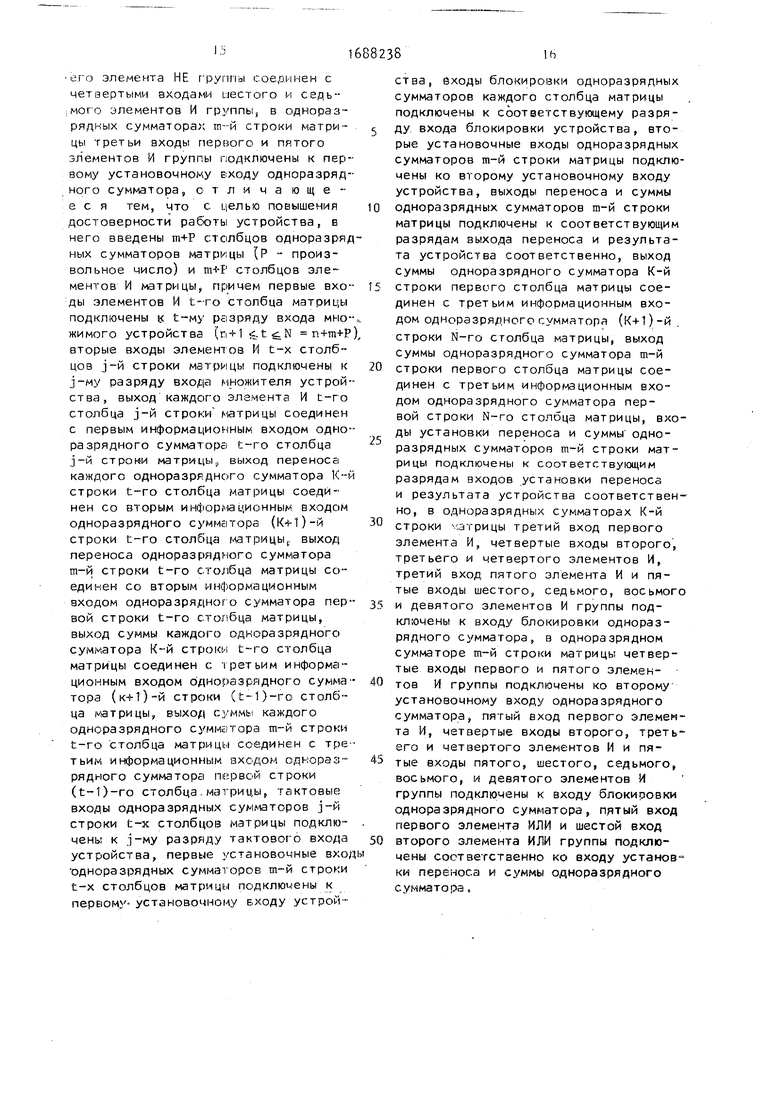

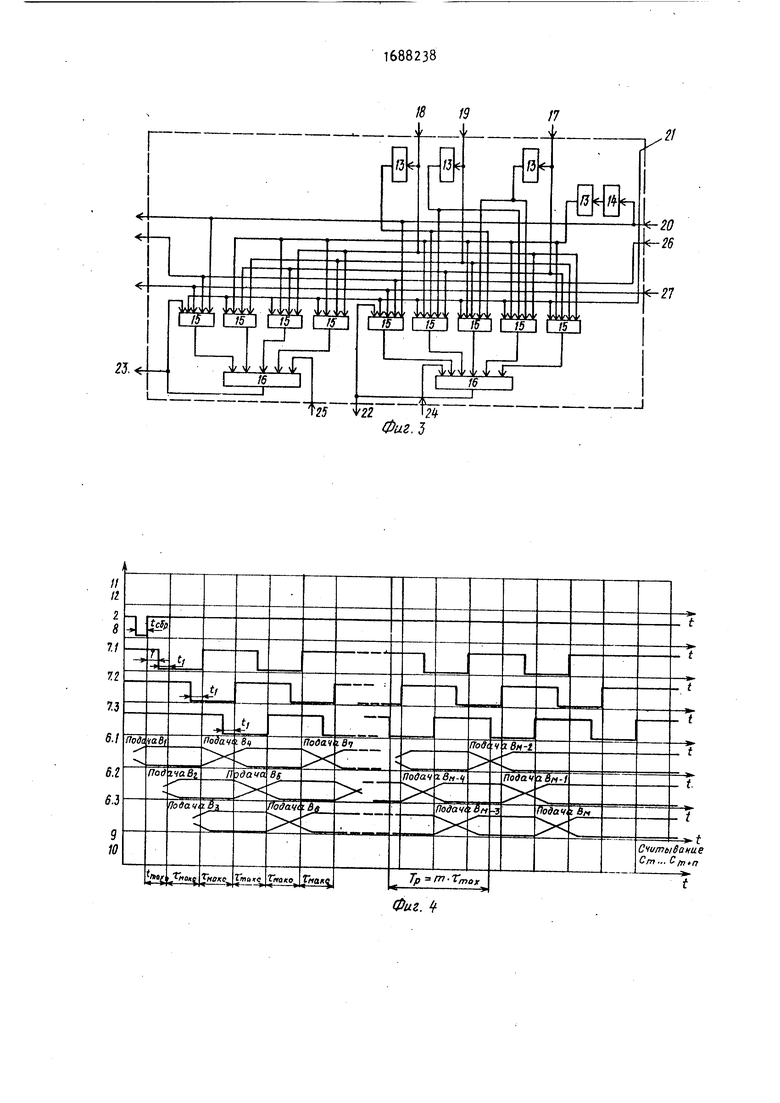

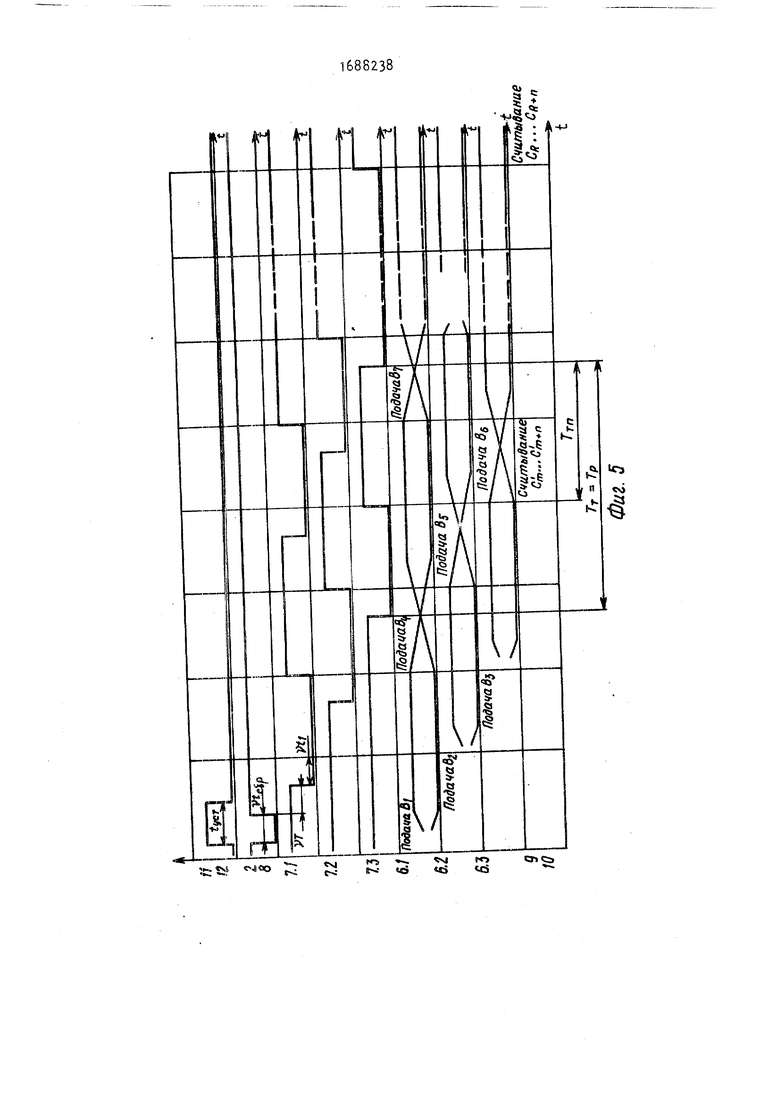

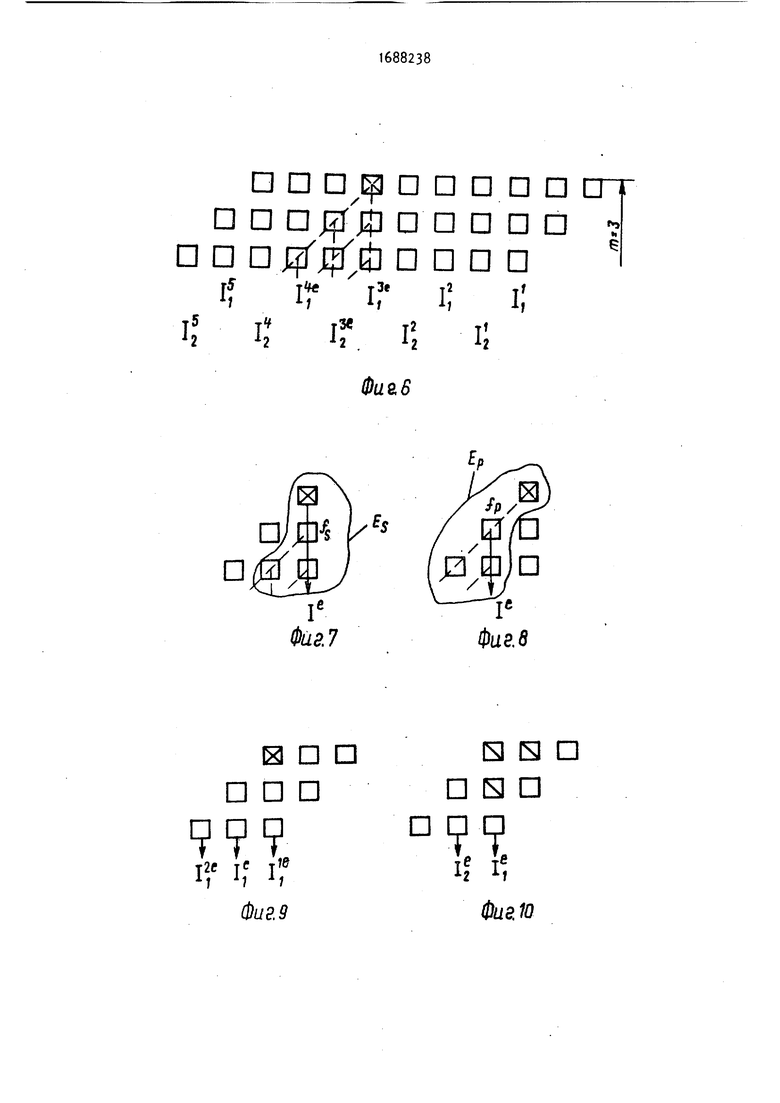

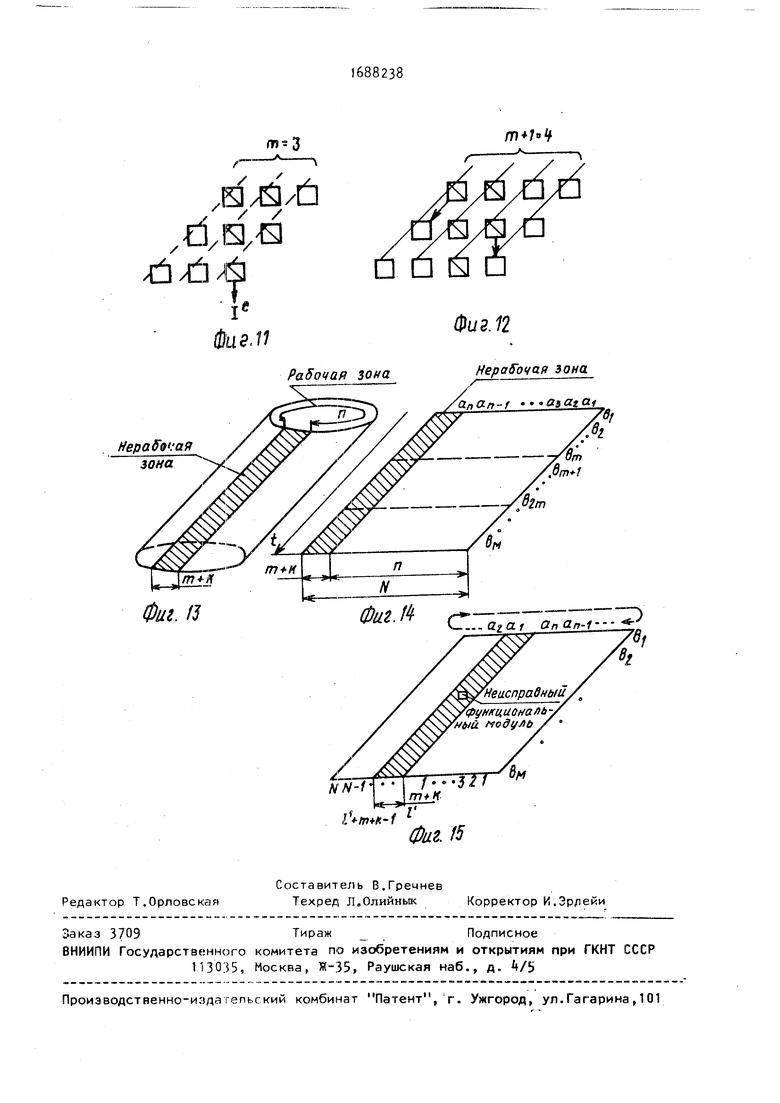

На фиг. 1 приведена функциональная схема устройства , на фиг. 2 - функциональная схема одноразрядного сумматора К-й строки матрицы (1ЈКст-1, где т - разрядность множителя)-, на фиг. 3 - функциональная схема одноразрядного сумматора последней строки матрицы; на фиг.4, 5 - временные диаграммы работы устройства в режиме вычислений и в подготовительном режиме соответственно , на фиг.6-12 показаны принципы локализации неисправного функционального узла , на фиг. 13 15 - расположение рабочей и нерабочей зон в матрице устройства.

Устройство (фиг.1) содержит матрицу 1 одноразрядных сумматоров, первый установочный вход 2, матрицу 3 элементов И, вход 4 блокировки, вход 5 множимого, вход 6 множителя, тактовый вход 7 второй установочный вход 3, выход 9 результата, выход 10 переноса, вход 11 установки результата, вход 12 установки переноса.

Одноразрядные сумматоры матрицы -1 (фиг.2, 3) содержат граппу 13 элементов НЕ, элемент задержки 14, группу 15 элементов И, группу 16 элементов ИЛИ, информационные входы 17-19, тактовый вход 20 и вход 21 блокировки, выходы 22, 23 суммы и переноса, входы 24, 25 установки суммы и переноса, установочные входы 26, 27.

Устройство .может работать в двух режимах: подготовительном и вычислительном.

0

00 00 Ю

03 00

316

В подготовительном режиме производится тестирование устройства для умножения и локализация неисправного функционального модуля. Полагаем, что матрица умножения содержит один неисправный Функциональныймолуль (пол функциональным модулем устройства для умножения понимается элемент И матрицы 3, либо одноразрядный сумматор матрицы 1).

Рассмотрим работу устройства для умножения в режиме вычислений.

Режим вычислений в зависимости от того, содержит устройство умножения неисправный функциональный модуль или нет, подразделяется на подрежимы вычислений при наличии неисправного функционального модуля и без него,, Работа устройства и этих двух подрежи мах отличается только положением рабочей зоны (т.е. области устройства в которой проводятся вычисления), и нерабочей зоны (т„е„ области устройства , в которой вычисления не проводятся (см.фиг. 1 3 15) .

Одноразрядные сумматоры рядов, кроме последнего„ описываются системой уравнений

S(t+1) j(abc + abc - - abc + abc)y +

+ S(t). y z y

P(t + 1) (ab +bc ac)y +

(1)

Одноразрядные сумма горы последнего ряда устройства описываются системой уравнений:

S(t + 1) f(abc + abc -i sbc +аЪс)у + + S(t),d2,(2)

P(t + 1) (ab -be -ь ас) у + ч- P(t) zd,d,2 ,

8 уравнениях (t) и (2) a,b,c - сигналы на информационных входах одноразрядных сумматоров1,

S(t), P(t) - сигналы на выходах

22523 суммы и переноса одноразрядного сумматора в момент времени t {

у - сигнал на тактовом входе 20 одноразрядного сумматора ,, z - сигнал на входе 21

0

5

-

0

5

0

35

40

45

55

олокироаки одноразрядного сумматора; d$ - сигналы на входах

26, 27 одноразрядных сумматоров последнего ряда (сброс).

Как видно из (1) и (2), подачей сигналов О на входы блокировки 4.1- 4.N устройства можно блокировать выходы одноразрядных сумматоров соответствующих столбцов, запрещая тем самым вычисления на этих столбцах устройства для умножения.

Рабочая и нерабочая зоны определяются значениями логических величин на соответствующих входах блокировки f.l-.N. На входы блокировки рабочей зоны подаются сигналы 1, на входы блокировки нерабочей зоны - сигналы О. В подрежиме вычислений без неисправного функционального модуля положение рабочей и нерабочей зон произвольно (например, как на фиг,13). В подрежиме вычислений при наличии неисправного функционального модуля нерабочая зона совмещается с областью устройства, в которой локализован неисправный функциональный модуль (фиг.15), посредством подачи сигналов П0 на соответствующие входы k блокировки. Рабочая зона устанавливается в области устройства ддя умножения, не содержащей неисправности, посредством подачи на соответствующие входы k блокировки сигналов 1. Как было сказано, подача сигналов О на входы k блокировки блокирует выходы одноразрядных сумматоров нерабочей зоны. Вычисления производятся в рабочей зоне и в обоих подрежимах режима вычислений проходят аналогично. Возможные положения рабочей и нерабочей зон показаны на фиг.13-15.

Рассмотрим работу устройства для умножения в подрежиме вычислений без неисправного функционального модуля. Пусть положение рабочей и нерабочей зон такое, как показано на фиг. И. В этом случае на входы k,-,n устройства подаются сигналы 1, на входы 4,n+1-4.N устройства подаются сигналы

Процесс вычисления будет проходить в рабочей зоне матрицы, В исходном состоянии на входах 7.1, 7.2... 7„т, 2; 8 установлены сигналы 1м

(см.фиг.k, m 3). Перед началом вычислений на входы 2, 8 подается отрицательный импульс Сброс длитель1б8

ностью tcgp . Импульс Сброс сбрасывает в нулевое состояние выходы сумм и переносов одноразрядных сумматоров т. 1-го.п- матрицы 1.

Устройство для умножения работает в конвейерном режиме. Процесс вычислений начинается с подачи на входы 5.1-5.П разрядов а,...,3 п-разряд- ного множимого А и младшего разряда М-разрядного множителя В на вход 6.1J момент подачи совпадает с задним фронтом импульса Сброс, этот момент времени полагаем началом отсчета. Спустя время Т t,, на вход 7.1 подается сигнал О, разрешающий суммирование на одноразрядных сумматорах 1.1-1-п матрицы 1 (tWQv;c - максимальное время задержки сигнала в логическом элемента И, t, - суммарное максимальное время задержки сигнала в элементах задержки 1- и НЕ 13 (см.фиг.2, фиг.З), t4 Д+ tMa)CCH

& - время задержки сигнала в элементе задержки И. Через время t/ +

с длакс вычисления в первом ряду заканчиваются, и на вход 7.1 подается сигнал 1, обеспечивающий запоминание информации, установившейся на выходах одноразрядных сумматоров 1.1-1,п матрицы 1, и запрещающий обработку сиг

1б8о23В

печивающий запоминание информации, устанавливающейся на выходих одноразрядных сумматоров 2.1-2.П матрицы 1, и запрещающий обработку сигналов, которые будут появляться на их информационных входах. Аналогично процесс вычисления продолжается до m-го ряда. Разряд bm множителя В подается на вход б.т к моменту (т-1) Ј Ллокс В момент времени (tyWaKC и +(m-1)Ј/wakc-t1) на вход 7.т подается сигнал О, разВ

0

решающий вычисления на m-м ряду, момент времени t/waKCM+(m-1 ) С ДАОКС на 5 вход 7(т-1) подается сигнал 1, обеспечивающий запоминание информации , установившейся на выходах одноразрядных сумматоров (т-1).1-(т-1),п матрицы 1, и запрещающий обработку сигналов, которые будут появляться на их информационных входах. Далее процесс вычисления продолжается циклически. Пока идет вычисление на т-м ряду, на первом ряду идет подготовка к вычислению. К моменту m S ддпкс на вход 6.1 подается разряд В р,, множителя В.

В момент времени Јмаксц+ mt-/noKc t{ вход 7.1 подается сигнал О, раз5

0

на

решающий вычисление на пеовом ряду, а в момент и + на вход 7,га подается сигнал 1, обеспечивающий запоминание информации, установившейся на выходах одноразрядных сумма

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для вычисления сумм произведений | 1973 |

|

SU480077A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах. Цель изобретения - повышение достоверности работы устройства. Устройство содержит матрицу 1 одноразрядных сумматоров, первый установочный вход 2, матрицу 3 элементов И, вход 4 блокировки, входы 5, 6 множимого и множителя, тактовый вход 7, второй установочный вход 3, выходы 9, Ю результата и переноса, входы 11, 12 установки результата и переноса, 15 ил., 2 табл.

налов, которые будут появляться на их 35 торов m.1-m.n матрицы 1, и запрещающий обработку сигналов, которые будут появляться на их информационных входах. Далее процесс вычисления продолжается аналогично.

40После подачи всех М разрядов множителя В на входах 6.1-б.т устанав- ливаются сигналы О, а процесс вычисления продолжается, пока разряды результата Cw - Ст+п не установятся

информационных входах (сддаусс- максимальное время прохождения сигналов в одноразрядном сумматоре от входов до выходов).

Ранее, когда проходили вычисления на первом ряду устройства, на втором ряду проходила подготовка к вычислениям. К моменту времени &ддок.сна входе 6.2 установился второй разрял Е.

множителя В. В момент времени (tMQ)(p + 4 на выходах 9..т и 10. 1-10.m уст+ч;маке+ t, )на вход 7.2 был подан сигройства (в двухрядном кеде). Младшие разряды результата С - С tме вы водятся.

нал

разрешающий вычисления на

втором ряду устройства. I

Пока идут вычисления на втором ряду, на третьем ряду происходит подготовка к вычислению. Третий разряд B-j мнонителя В устанавливается к моменту 2о дддКс. В момент времени ладкси 2ЈMQKC- t,)Ha вход 7.3 подается сигнал О, разрешающий вычисления на третьем ряду устройства. В момент времени (2./vsaKC+ tMOKCM) на вход 7.2 подается сигнал 1, обесна выходах 9..т и 10. 1-10.m уст

ройства (в двухрядном кеде). Младшие разряды результата С - С tме вы водятся.

Отказоустойчивость устройства обеспечивается за счет периодического тестирования, локализации неисправного функционального модуля, если он есть, и реконфигурации устройства для его нейтрализации.

i

Работа устройства в подготовительном режиме отличается от работы в режиме вычисления тем, что в исходном состоянии на всех входах блоки4 , i - 4 „ N ус i а но ал e 11 u сиг на л ы на яходы установки 1KI-11.N, 12.1- 12.N поданы соответствующие разряды первого и второго установочного тесто вого операнда. Длительность tu установочного импульса на входах 11 и 12:

1638238 1,

Ч эх 11

(3)

V

Этот импульс устэнааливает на выходах суммы и переноса одноразрядных сумматоров m.N-m.1 - матрицы 1 сигналы, соответствующие разрядам первого и второго установочных тестовых операндов соответственно, Затем осуществляется подача тестовых значений первого операнда Лг (множимого) и второго операнда Вт (множителя) аналогично тому, как это осуществлялось в режиме вычисления,

Период управляющих сигналов Тг (фиг.5) в подготовительном режиме определяется временем 1Q, необходимым для анализа тестовых откликов (в двухвые о клики (выходы суммы и пеоенос Если предположить, что в устройстве для умножения есть один неисправный

г функциональный модуль, то в результ те его неисправности возникает ошиб е тестовом вычислении, которая на m тактов работы может вызвать группов ошибку и изменить выходы суммы и

Ю переноса m ячеек в последнем ряду устройства, доступном для наблюдения, нарушив идентичность соответствующих откликов. Тогда, если орга низовать сравнение тестовых отклико

15 по р идентичным группам, то число н верных тестовых откликов будет мень ше числа верных внутри идентичной группы (полагаем, что N гя для бол шинства практических реализаций), ч

20 позволяет локализовать неверные тестовые отклики внутри идентичной группы через голосование., Локализов неверные тестовые отклики, можно с точностью в худшем случае до m пози

рядном коде) с соответствующих выходсв 5 ций столбца определить локализацию

запоминает

дах (фиг.5). Считаемр чго IT -у i p

где -J соответствует коэффициенту уменьшения тактовой опорной частоты,, используемой при формировании управляющих сигналов.

Для локализации неисправного функционального модуля (одноразрядного сумматора матрицы I или элемента И матрицы 3) осуществляется тестирование устройства за счет начальной установки (установочных тестовых операндов) и подачи таких знамений входных тестовых операндов Ат и Вт. что на каждый одноразрядный сумматор матрицы 1 и элемент И матрицы 3 в процессе тестового вычисления поступают все входные тестовые наборы. Пои этом тестовые операнды подбираются так, что картина распределения входных тестовых наборов в устройстве для умножения повторяется в каждом D-M столбце (р 2 в примере таблицы 2), что обеспечивает идентичность тестовых откликов ччеек каждого р-го столбце, т.е. при Р -2 вес- ячейки, стоящие на четных (нечетных) позициях в рядах устройства для умножения в процессе1 тестирования имекп одинаковые тесто-8

вые о клики (выходы суммы и пеоеноса) . Если предположить, что в устройстве для умножения есть один неисправный

функциональный модуль, то в результате его неисправности возникает ошибка е тестовом вычислении, которая на m тактов работы может вызвать групповую ошибку и изменить выходы суммы и

переноса m ячеек в последнем ряду устройства, доступном для наблюдения, нарушив идентичность соответствующих откликов. Тогда, если организовать сравнение тестовых откликов

по р идентичным группам, то число неверных тестовых откликов будет меньше числа верных внутри идентичной группы (полагаем, что N гя для большинства практических реализаций), что

позволяет локализовать неверные тестовые отклики внутри идентичной группы через голосование., Локализовав неверные тестовые отклики, можно с точностью в худшем случае до m позинеисправного функционального модуля. Поскольку размерность матрицы устройства для умножения MX т, где N п + + m+k, i де п - разрядность множимого, то возможно выполнять вычисление в различных областях устройства для умножения, соответствующих различным положениям рабочей зоны, обеспечив при этом совмещение блокируемой области матрицы - нерабочей зоны размерностью (m+k) с областью локализации неисправного функционального модуля размерностью т, используя при этом кольцевую структуру устройства для

умножения. Таким образом, влияние неисправного функционального модуля в дальнейшем, на вычисления в рабочей зоне нейтрализуется. При этом соответственно изменяется порядок нумерации входных (множимого) и выходных (результата) шин.

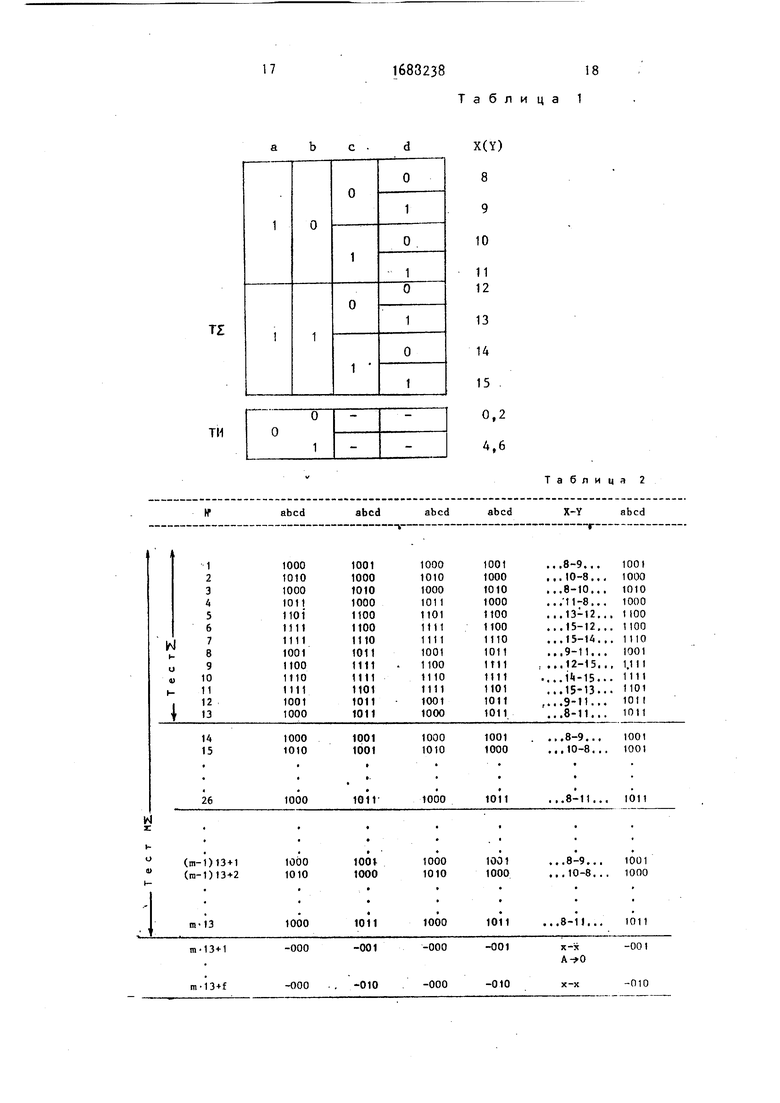

Тля удобства описания принято, что элемент И матрицы 3 и одноразрядный сумматор матрицы 1 образуют ячейку умножения. Ячейка умножения является четырехвходовой, и ей соответствуют входные наборы а формате abcd, , где а - двоичный разряд иножимого, Ь - множителя, с - частичного произвеления , d - переноса. Для исчерпывающего тестирования функциональных модулей в составе ячейки умножения необходимо 10 тестовых входных наборов, которые (в фор

у1

мате abcd) представлены в табл.1, восемь тестовых входных наборов для исчерпывающего тестирования трехвхо- дового одноразрядного сумматора (Т21 и два входных тестовых набора (ТИ) из четырех, необходимых для исчерпывающего тестирования -двухвходового элемента И, которые не покрываются TZ.

В табл.2 приведен пример распределения входных тестовых наборов в двоичном формате abcd для развернутой во времени замкнутой конвейерной матрицы (Р 2}, которая для удобства восприятия представлена в ортогональном виде.

В табл.2 каждому двоичному числу в формате Јabed соответствует десятичное число X(Y) (табл.1). Лля удобства анализа распределения входных тестовых наборов в двух столбцах табл.2 приведены также десятичные коды X-Y тестовых входных наборов, соответствующих двум соседним столб- цам. Тест включает восемь входны тестовых наборов (Т 2. табл.1), для подачи которых необходимо (для рассматриваемого примерз ; 13 тактоврабо- fbi устройства, образующих условно, цикл. Тест 5 , обеспечивая за m циклов приложение каждого из 8 входных тестовых наборов к каждому одноразрядному сумматору, обеспечивает исчепывающее тестирование всех одноразрядных сумматоров матрицы за т.13 тактов работы устройства.

Если предположить, что m 3 (фиг.1), то после первых трех тактов работы (первый цикл) устройства для умножения с выхода одноразрядных сумматоров последнего ряда матрицы 1 сни маются разряды (в двухрядном коде) Старшей части частичного произведе-, crn (Фиг. 5), анализируются

ни я

Для завершения тестирования элементов И необходимо дать еще два40 входных тестовых набора (ТИ табл.1). Лля этого разряды множимого Ат устанавливаются в нуль, не прерывая работы устройства, так как на (т.13-1)-м

и (т.13-2)-м тактах работы устройства 45 Ки), то тестирование прерывается, и разряды множителя Вт равны нулю инеисправный функциональный модуль лоэлементы И соответствующих рядов мат- ализуется, соответствующие столбцы рицы 3 заблокированы, что позволяет либо бсуществить установку Аг в ноль

за эти два такта, либо при необходи- 50 выми номерами внутри ряда), мости использовать дополнительно,Рассмотрим пример: N 10, m 3

еще f, тактов, что определяется вре-() квадраты соответствуют ячейменем сброса соответствующего регист- кам умножения, неисправен функцио- ра, хранящего разряды А . Затем осу-нальный модуль в ячейке умножения

ществляется еще 2т тактов работы первого ряда (обозначена Ј3 ). В ре- ройства (тест -МИ), в которых на входы зультате неисправности возникает об-ч- элементов И всех рядов матрицы 3 по-ласть Е возможного распространения

даются два входных тестовых набора ошибки,которая определяет возможную

(в формате «Јabcd ) 01 - - и 00 - -, групповую ошибку на входах суммы - перена идентичность внутри соответствующих групп и, если обнаружена ошибка - неверный тестовый отклик (или откли матрицы блокируются (столбец образ} ется ячейками с одинаковыми порядко

38Ч

}Q

которым фактически соответствуют 0100, 0110,и 0010,;ООСО (табл.1,2).

При тестировании не проверяется цепь сброса одноразрядных сумматоров матрицы последнего ряда, поэтому она дублируется.

Значения установочных тестов операндов (для примера табл.2) разрядности N устанавливаются за счет подачи на входы 11.1-11.N сигналов О, на входы 12.1, 12.3, 12.5... сигналов 1, на входы 12.2, 12., 12.6... сигналов О (реализация установки описана ранее) .

Значения всех N разрядов входного тестового операнда А на 1-рт.13 тактах работы равны 1 , на остальных О .Значение входного тестового операнда Вт (младшие разряды слева) представляет собой конкатенацию К, и вт

вт кУвУ..У,С)

m

в

к1.

00111001110000

000... 00,,

у-

f+П1

К„ 111.. .11

m

Разрядность операнда Вт равна R, где R m.15+f, f - дополнительное число тактов, достаточное для сброса А в ноль (.на практике f 0-2) .

Если предположить, что m 3 (фиг.1), то после первых трех тактов работы (первый цикл) устройства для умножения с выхода одноразрядных сумматоров последнего ряда матрицы 1 снимаются разряды (в двухрядном коде) Старшей части частичного произведе-, crn (Фиг. 5), анализируются

ни я

Ки), то тестирование прерывается, и неисправный функциональный модуль лона идентичность внутри соответствующих групп и, если обнаружена ошибка - неверный тестовый отклик (или откли ализуется, соответствующие столбцы

выми номерами внутри ряда), Рассмотрим пример: N 10, m 3

матрицы блокируются (столбец образ} ется ячейками с одинаковыми порядко

нсса трех (m - 3} чмеек умножения последнего ряла матрицы.

Неисправность функционального ьс дуля ячейки умножения может вызвать ошибку либо на выходе суммы, либо на выходе переноса, либо на обоих одновременно, Јсли ошибка проявилась по (выходу суммы ts (фиг 7), она определяет область распространения ошибки если по переносу f« (cbnr.8), то область Ер, Заметим мю действие неисправности все-да распространяется по цепям суммы (показано сплошной ли нией), либо в этой же позиции при Е, либо в следующей, npti Fp обеспечивая наблюдаемость на выходах ячеек умножения последнего ряда,

Тестовые отклики ячеек на четных (10) и нечетных (1f) позициях ячеек умножения последнего ряда идентичны, в соответствии с тзбл,. Тогда сравним 1, - ij между ,обой, определим, что и ошибочны, и, сравнивая. ч определив, что ошибочен 1г (в общем случае К Таким образом, голосованием в 1-й и 2-й группах идентичных отчликоз (соответствуют четным и нечетным позициям) определяются ошибочные отклики. Теперь расе ног рим этот примерЈ предположив, что но одном из циклов ген гироваиия обнаружилось три (фиг 9) ДЕ-а (фиг„10),

ИЛИ ОДИН (фИГо1 I ОШибоЧНЫХ OTrOIHKOB

что включает в себ| асг возможные1

случаи„

,#е

ка х 1 f,

На фиг.Ч ппи сьибочных от кли е 1« I г 9 I ,

iЈ, I, положеше ячейки умножения, соответогмуюшей неисправному функциональному модулю, определяется однозначно (i-m ® на фиг. 1 I ) „ На фиг,10 возможны три возможных положения этой ячеик (г ч, И на фиг, 10) и на фиг. 11 - пятi зосможмых положений, что соотеен ч у т худшему сп чгот . Из фиг,11 что положение ячейки умножения, содержащей неисправ ный функциональньи модуль, можно локализовать, в худшем спучае, до позиций (позиция соот ветстзуег столбцу или одной линии 5ло ИроВ| и 4. з фигв1). На фиг,2 , что .эля осуществления налеи-той блокировки все предполагаемых нгистравных ячеек необходимо блокировать тЧ /i позиции устройства (k - 2) Отметим что если бы m было четным числом, то k 2 для обеспечения иетнэй симметричности каргины распредепеч1л встовых наборов, прерпоженно Р ,2 Таким оо15

„ ,t

20

25

30

35

х «О

45

50

55

разом, если неисправный функциональный модуль локализован с точностью до m позиций, причем младшая (с учетом цик- лической структуры матрицы) позиция локализации 1, 1 18N, то блокируется (m+k) позиций от ( )-й до |(modfl(l + ffi+k-D-й, где 1/ (modu (1-k+N)). i

В дальнейшем все вычисления проводятся при данном положении рабочей зоны (соответствует режиму вычислений при наличии неисправного функционального модуля).

Если в первом цикле тестирования ошибка не обнаружена, то тестовое вычисление продолжается до тех пор, пока не обнаружится ошибка, или пока не будут приложены все входные тестовые наборы, осуществляющие исчерпывающее тестирование каждого функционального модуля. Если при тестировании ошибка не обнаружена, то полагаем, что устройство исправно относительно принятой модели неисправности одного функционального модуля, которая заключается в произвольном изменении соответствующей ему таблицы истинности,, при котопой он остается комбинационной схемой.

Возникновение неисправности второго функционального модуля, при котором оба неисправных функциональных модуля не покрываются при одном положении нерабочей зоны, соответствует фатальной неисправности.

Работа устройства в подрежиме вычислений при наличии неисправного функционального модуля {локализованного в подготовительном режиме) аналогична работе в подрежиме вычислений без неиспоавного функционального модуля, за исключением того, что в исходном состоянии ча входы 4.1 - 4.modN(l k -1) подаются О, где I1 1,N, определяющие положение нерабочей зоны, на остальные входы 4.1 подаются 1, определяющие положение рабочей зоны.

В исходном состоянии разряды множимого А подаются на входы 5.j (j 1,K) устройства, соответствующие положению рабочей зоны (фиг.15).

Так, например, если предположить, что 1 N, то блокируются (подаются О) входы 4.N. 4.1, 4.2,«..,4.nH-k-1, на остальные входы 4.j подаются 1. При этом изменяется соответственно порядок приложения разрядов множимо J

го А к входам 5 устройства. ля рассматриваемого примера при 1 N младший разряд а, множимого А подается на вход S.m-t-k, а старший ап - на вход 5.N-1. Соответственно изменяются выходы 9,j и 10.j, с которых считываются (в двухрядном коде) разряды результата С№ + п.

Таким образом, за счет периодического тестирования, локализации по рассмотренному на примере алгоритму реализуемому любым доступным програным или аппаратным способом, и последующей реконфигурации обеспечивается отказоустойчивость устройств для умножения к неисправности одног функционального модуля.

Формула изобретения Устройство для умножения, содержащее матрицу из m x n элементов И (п - разрядность множимого, m - произвольное целое число) и матрицу из m x n одноразрядных сумматоров, каждый из которых содержит группу элементов И, группу элементов ИЛИ, группу элементов НЕ и элемент задержки, причем первые входы элементов И 1-го столбца

матрицы подключены к i-му разряду вхо-эд подключены соответственно к первому,

да множимого устройства (), вторые входы элементов И j-й строки матрицы подключены к j-му разряду входа множителя устройства (1 Ј-JЈ-m), выход каждого элемента И 1-го столбца j-й строки матрицы соединен с первым информационным входом одноразрядного сумматора i-го столбца j-й строки матрицы, выход переноса каждого одноразрядного сумматора К-й строки 1-го столбца матрицы (1ЈК$т-1) соединен со вторым информационным входом одноразрядного сумматора (К+1)-й строки 1-го столбца матрицы, выход переноса одноразрядного сумматора m-й строки 1-го столбца матрицы соединен со вторым информационным входом одноразрядного сумматора первой строки 1-го столбца матрицы, выход суммы каждого одноразрядного сумматора К-й строки 1-го столбца матрицы () соединен с третьим информационным входом одноразрядного сумматора 1К+1)-й строки (1-1)-го столбца матрицы, выход суммы каждого одноразрядного сумматора m-й строки 1-го столбца матрицы соединен с третьим информационным входом одноразрядного сумматора первой строки (1-1)-го столбца матри35

40

второму и третьему информационным входам одноразрядного сумматора, выход элемента задержки через четвертый элемент НЕ группы соединен с первыми входами второго, третьего, четвертого, шестого, седьмого, восьмого и девятого элементов И группы, вторые входы второго, третьего, шестого и девятого элементов И группы подключены к первому информационному входу одноразрядного сумматора, тий вход второго элемента И, вторые входы четвертого и седьмого элементов И и третий вход девятого элемен- 45 та И группы подключены ко второму информационному входу одноразрядного сумматора, третьи входы третьего и четвертого элементов И, второй вход восьмого элемента И и четвертый вход девятого элемента И rpynt- чпы подключены к третьему информа- ционному входу одноразрядного сумматора, выход первого элемента НЕ группы соединен с третьими входами седьмого и восьмого элементов И группы, выход второго элемента ME группы соединен с третьим входом шестого элемента И и четвертым входом восьмого элемента И группы, выход треть50

55

0

цы, тактовые входы одноразрядных сумматоров j-й строки матрицы подключены к i-му разряду тактового входа устройства, первые установочные пходы одноразрядных сумматоров га-и строки матрицы подключены к первому установочному входу устройства, в каждом одноразрядном сумматоре матрицы выходы первого и второго элементов ИЛИ группы являются соответственно выходами переноса и суммы одноразрядного сумматора, выходы первого, второго, третьего и четвертого элементов И группы соединены с соответствующими входами первого элемента ИЛИ группы, выход которого соединен с первым входом первого элемента И группы, выходы пятого, шестого, седьмого, восьмого и девятого элементов И группы соединены с соответствующими входами второго элемента ИЛИ группы, выход которого соединен с первым входом пятого элемента И группы, вторые вхо- 5 ды первого и пятого элементов И груп- пы и вход элемента задержки подключены к тактовому входу одноразрядного сумматора, входы первого, второго и третьего элементов НЕ группы

5

0

5

0

второму и третьему информационным входам одноразрядного сумматора, выход элемента задержки через четвертый элемент НЕ группы соединен с первыми входами второго, третьего, четвертого, шестого, седьмого, восьмого и девятого элементов И группы, вторые входы второго, третьего, шестого и девятого элементов И группы подключены к первому информационному входу одноразрядного сумматора, тий вход второго элемента И, вторые входы четвертого и седьмого элементов И и третий вход девятого элемен- 5 та И группы подключены ко второму информационному входу одноразрядного сумматора, третьи входы третьего и четвертого элементов И, второй вход восьмого элемента И и четвертый вход девятого элемента И rpynt- чпы подключены к третьему информа- ционному входу одноразрядного сумматора, выход первого элемента НЕ группы соединен с третьими входами седьмого и восьмого элементов И группы, выход второго элемента ME группы соединен с третьим входом шестого элемента И и четвертым входом восьмого элемента И группы, выход треть0

5

его элемента НЕ группы соединен с четвертыми входами иестого и седьмого элементов И группы, в одноразрядных сумматорах тп--й строки матри- цы третьи аходы первого и пятого элементов И группы подключены к первому установочному входу одноразрядного сумматора, отличающееся тем, что с целью повышения достоверности работы устройства, в него введены т+Р столбцов одноразрядных сумматоров матрицы (Р - произвольное число) и т+Р столбцов элементов И матрицы, причем первые вхо- ды элементов И t-ro столбца матрицы подключены к t-му разряду входа множимого устройства (n-Н ,tg.N п+т-нр) вторые входы элементов И t-x столбцов j-й строки матрицы подключены к j-му разряду входа множителя устройства, выход каждого элемента И t-ro столбца j-й строки матрицы соединен с первым информационным входом одно-разрядного сумматора t-ro столбца j-й строки матрицы,, выход переноса каждого одноразрядного сумматора К--й строки t-ro столбца матрицы соединен со вторым информационным входом одноразрядного сумматора (Кн-1)-й

строки t-ro столбца матрицы,, выход переноса одноразрядного сумматора m-й строки t-ro столбца матрицы соединен со вторым информационным входом одноразрядного сумматора пер- вой строки t-ro столбца матрицы, выход суммы каждого одноразрядного сумматора К-й строки t-ro столбца матрицы соединен с третьим информационным входом одноразрядного сумма- тора (к+1)-й строки (t-1)-rc столбца матрицы, выход суммы каждого одноразрядного сумматора га-и строки t-ro столбца матрицы соединен с третьим информационным входом одкораз™ рядного сумматора первой строки (t-1)-ro столбца.матрицы, тактовые входы одноразрядных сумматоров j-й строки t-x столбцов матрицы подклю- чены к j-му разряду тактового входа устройства, первые установочные вход одноразрядных сумматоров т-и строки t-x столбцов матрицы подключены к первому- установочному входу устрой5

с 5 0 0

5 0 45 0

ства, входы блокировки одноразрядных сумматоров каждого столбца матрицы подключены к соответствующему разряду входа блокировки устройства, вторые установочные входы одноразрядных сумматоров m-й строки матрицы подключены ко второму установочному входу устройства, выходы переноса и суммы одноразрядных сумматоров m-й строки матрицы подключены к соответствующим разрядам выхода переноса и результата устройства соответственно, выход суммы одноразрядного сумматора К-й строки первого столбца матрицы соединен с третьим информационным входом одноразрядного сумматора (К+1)-й . строки N-ro столбца матрицы, выход суммы одноразрядного сумматора m-й строки первого столбца матрицы соединен с третьим информационным входом одноразрядного сумматора первой строки N-ro столбца матрицы, входы установки переноса и суммы одноразрядных сумматоров m-й строки матрицы подключены к соответствующим разрядам входов установки переноса и результата устройства соответственно, в одноразрядных сумматорах К-й строки матрицы третий вход первого элемента И, четвертые входы второго, третьего и четвертого элементов И, третий вход пятого элемента И и пятые входы шестого, седьмого, восьмого и девятого элементов И группы подключены к входу блокировки одноразрядного сумматора, в одноразрядном сумматоре m-й строки матрицы четвертые входы первого и пятого элементов И группы подключены ко второму установочному входу одноразрядного сумматора, пятый вход первого элемента И, четвертые входы второго, третьего и четвертого элементов И и пятые входы пятого, шестого, седьмого, восьмого, и девятого элементов И группы подключены к входу блокировки одноразрядного сумматоре, пятый вход первого элемента ИЛИ и шестой вход второго элемента ИЛИ группы подключены соответственно ко входу установки переноса и суммы одноразрядного сумматора.

со

го

г г с; ю

(О

X

тэ

гс

я

X

с.

о

Я

с i

о I

о о о I

f

abed

abed

0010 0000 0010

0000 0010 0000

ш-14+f

0010

0000

IO.H м «a 9 юг 92 м а/

Фиг. I

-J

Ј.;- Фиг. I

Продолжение табл.2 X-Yabed

abed

abed

0000 0010 0000

,.2-0... 0000 ,.0-2,,. 0010 ,.2-0... 0000

0000

0000

.2-0.

0000

S.H t.3 5J « 5.2 V

Фиг. I

tz-

61 81

Ј гл/р

tfj

8 28891

fe

Jl

ffiSI7(J

I in

DSD S H

ITZyZ

тfT/тГ

г

г,

Т Ч л1 si

Т 1Т т т т i1г1 с-1

DD П D ф jifjif D П П

D ПD П D П П П

П ПП П П ЙХП П П

0э

(, IT т

л , Я1

iii

D П П П

9ъпф

г

г,

Т Ч л1 si

m-3

/

/

/ Q/ /

-d /u /и

e

Фа г И

t3/a/u / /

-s

Рабочий зона

Фиг. Я

Фиг. 12

Нера&очъя зона. Q-n&n-f g3ggOf

Функциональ-, ный. модуль /

l

Фиг. 15

| Авторское свидетельство СССР № 4156064, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1987 |

|

SU1501045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-30—Публикация

1989-05-11—Подача