второй входы первой ячейки дополнительной строки подключены к входам нулевого сигнала устройства, первый вход первой ячейки первой строки и пятый вход N-ой ячейки дополнительно строки подключены соответственно к первому и второму управляющим входам устройства, четвертые входы ячеек первой строки и N-ro столбца подключены соответственно к выходам соот ветствующих элементов И третьей и вт рой групп, пятые входы ячеек N-ro столбца подключены к выходам соответствующих элементов ИЛИ группы.

2. Матричное вычислительное устройство по п, 1, о т л и ч а ю щ е ес я тем, что каждая ячейка содержит

одноразрядный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем первый вход ячейки соединен с первым выходом ячейки и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,второй вход которого соединен с выходом элемента И, выход элемента ИСКЛОЧАЮЩЕЕ ИЛИ соединен с первым входом cyjjiMaTopa, второй вход, выход суммы, вход переноса и выход переноса которого соединены соответственно с четвертым входом, четвертым выходом, третьим входом и третьим выходом ячейки, первый вход элемента И соединен с вторым входом и вторым выходом ячейки, второй вход элемента И соединен с пятым входом и.пятым выходом ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Матричное устройство для деления /его варианты/ | 1981 |

|

SU1035602A1 |

| МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1991 |

|

RU2018932C1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

Изобретение относится к вычислительной технике и может Ьыть использовано /у1Я построения матричных устройств деления и умножения в специализированных вычислителях и быстро- 5 действукхцих ЭВМ.

Известно матричное устройство для . выполнения операции умножения двоичных чисел, содержащее матрицу ячеек, каждая из которых включает однораэ- ® рядный сумматор и И l

Недостатком известного устройства для умножения являются ограниченные функциональные возможности, так как устройство позволяет выполнять толь- 5 ко умножение в прямых кодах.

Наиболее близким к изобретению по технической сущности является матричное вычислительное устройство для выполнения деления, содержащее матри 20 цу ячеек из п строк и п столбцов, причем первый, второй, третий и четвертый входы ячейки }-ой строки, J-ro столбца . соединены соответственно с . первым выходом ячейки 1-ой строки, 5 (j-l)-ro столбца, вторым выходом ячейки (1-1)-ой строки, j-ro столбца, третим выходом ячейки г-ой строки (jfl)-ro столбца и четвертым выходом ячейки (Г-1)-ой строки, (J-H)-ro столбца, 30 первый вход ячейки i -ой строки первого столбца соединен с третьим выходом ячейки (-1)-ой строки первой строки

первого столбца, первый выход ячейки Г-ой строки п-го столбца соединен с третьим входом ячейки F-ой строки п-го столбца, вторые входы ячеек первой строки являются входа 4 1 делителя устройства, четвертые входы ячеек первой строки и п-го столбца являются входами делимого устройства, третьи выходы ячеек первого столбца являются выходами частного устройства, четвертые выходы ячеекп-ой строки являются выходами остатка устройства (|в1,п j«t,n).

Ячейка содержит одноразрядный сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход ячейки соединен с первым выходом ячейки и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,- второй вход которого соединен с вторым входом ячейки, а выход соединен с первым входом сумматора, второй вход которого соединен с четвертым входом ячейки, а выход суммы, вход переноса и выход переноса соединены соответственно с четвертым выходом, третьим входом и третьим выходом ячейки .

Недостатком известного устройства является ограниченность функциональных возможностей, т.е. при данном наборе ячеек и связей между ними выполняется только одна арифметическая операция - деление Двоичных чисел в прямых кодах.

Целью изобретения является расширение функциональных возможностей за счет реализации операций деления и умножения.

Поставленная цель достигается тем, 5 что устройство, содержащее матрицу ячеек из .N строк и N столбцов, пер-, вый вход п-ой ячейки каждой строки (,3,...,N) подключен к первому выходу (п-1)-ой ячейки этой же строки, второй вход п-ой ячейки каждого столбца под ключей к второму выходу (п-1 )-ой ячейки то же столбца,третий вход i-ой ячейкикаждой строки (1 1, 2,.. .... ,N-1) подключен к третьему выходу (1+1)-ой ячейки этой же строки, четвертый вход каждой ячейки каждой строки, за исключением ячеек первой строки и N-го столбца, подключен к четвертому выходу ячейки предыдущей строки последующего столбца, третий вход каждой ячейки N-ro столбца подключен к первому вхЬду этой же ячейки,-вторые входы ячеек первой строки соответственно подключены к входам первого операнда устройства, четвертые выходы ячеек N-ой строки являются выходами младших разрядов результата устройства, содержит группу элементов ИЛИ, первую, вторую и тpetью группы 30 элементов И и дополнительную строку из N ячеек, причем первый вход п-ой ячейки дополнительной строки подключен к первому выходу (п-1)-ой ячейки этой же строки, второй вход п-ой ячейки 35 дополнительной строки подключен к четвертому выходу (п-1)-ой ячейки nepiвого столбца, третий вход 1-ой ячей- ки дополнительной строки подключен к третьему .выходу (i + 1)-ой ячейки той 40 же строки)четвертый вход i-ой ячейки дополнительной строки соединен с третьим выходом Ной ячейки первого столбца и первым входом -ого элемента И первого столбца, выход которого со- 5 единен с первым входом (+1)-ой ячейки первого столбца, третий и четвертый входы N-ой ячейки дополнительной строки соединена соответственно с первым выходом этой женячейки и третьим 50 выходом ячейки первого столбцаj пятый вход 1-ой ячейки каждой строки, подклкяен к пятому выходу (+1)-ой ячейки этой же строки, первые входы элементов И первой, второй и третьей-55 групп, элементов ИЛИ группы подключены к первому управляющему входу устройства, вторые входы элементов

ИЛИ группы подключены соответственно к вторым входам элементов И третьей группы и входам старших разрядов первого операнда устройства, вторые входы элементов И второй группы подключены соответственно к входам младших разрядов первого операнда устройства, четвертые выходы ячеек дополнительной строки являются выходами старших разрядов результата устройства, первый и второй входы первой ячейки дополнительной строки подключены к входам нулевого сигнала устройства, первый вход первой ячейки первой строки и

пятый вход N-ой ячейки дополнительной строки подключены соответственно к первому и второму управляющим входам, четвертые входы ячеек первой строки и N-ro столбца подключены соответственно к выходам соответствующих элементов И третьей и второй групп, пятые входы ячеек N-ro столбца подключены к выходам соответствующих элементов ИЛИ группы.

Кроме того, каждая ячейка содержит

одноразрядный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем первый вход ячейки соединен с первым выходом ячейки и первым входом элемента /ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которогб соединен с выходом элемент та И, выход элемента ИСКЛЮЧАЩЕС ИЛИ соединен с первым входом сумматора, второй вход, выход суммы, вход переноса и выход переноса которого сое/у1нены соответственно с четвертым входом, четвертым выходом, третьим входом и третьим выходом ячейки, первый вход элемента И соединен с вторым входом и вторым выходом ячейки , второй вход элемента И соединен с пятым входом и пятым выходом ячейки

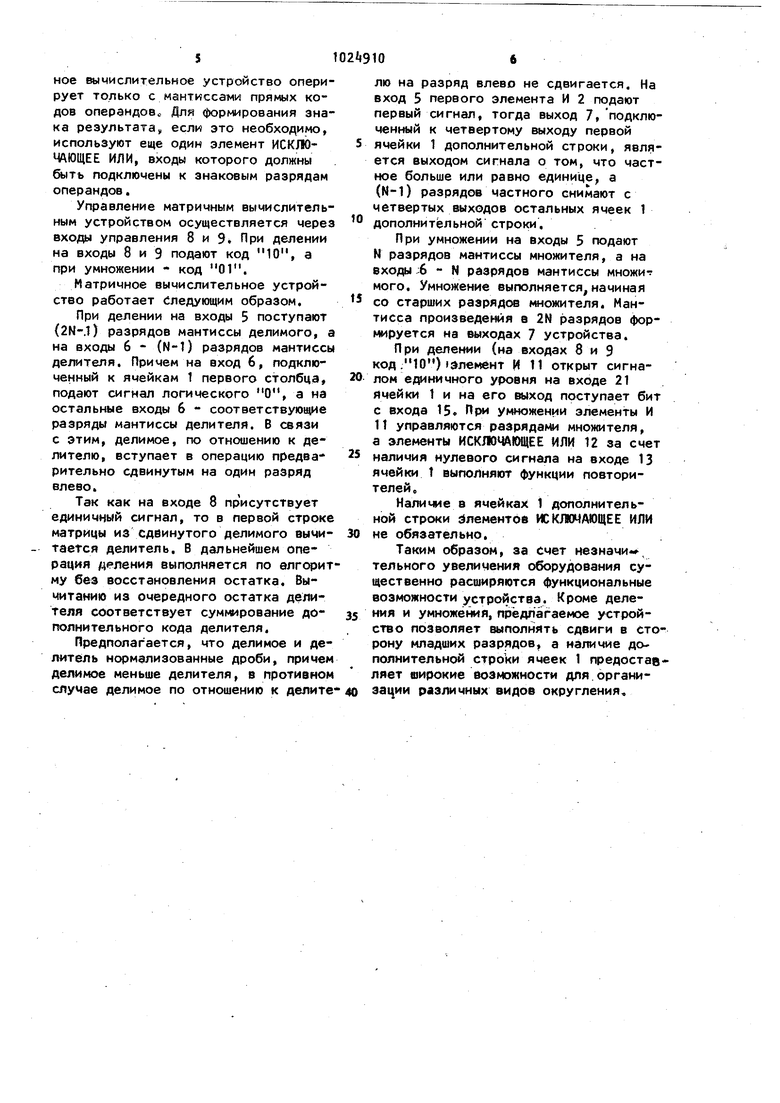

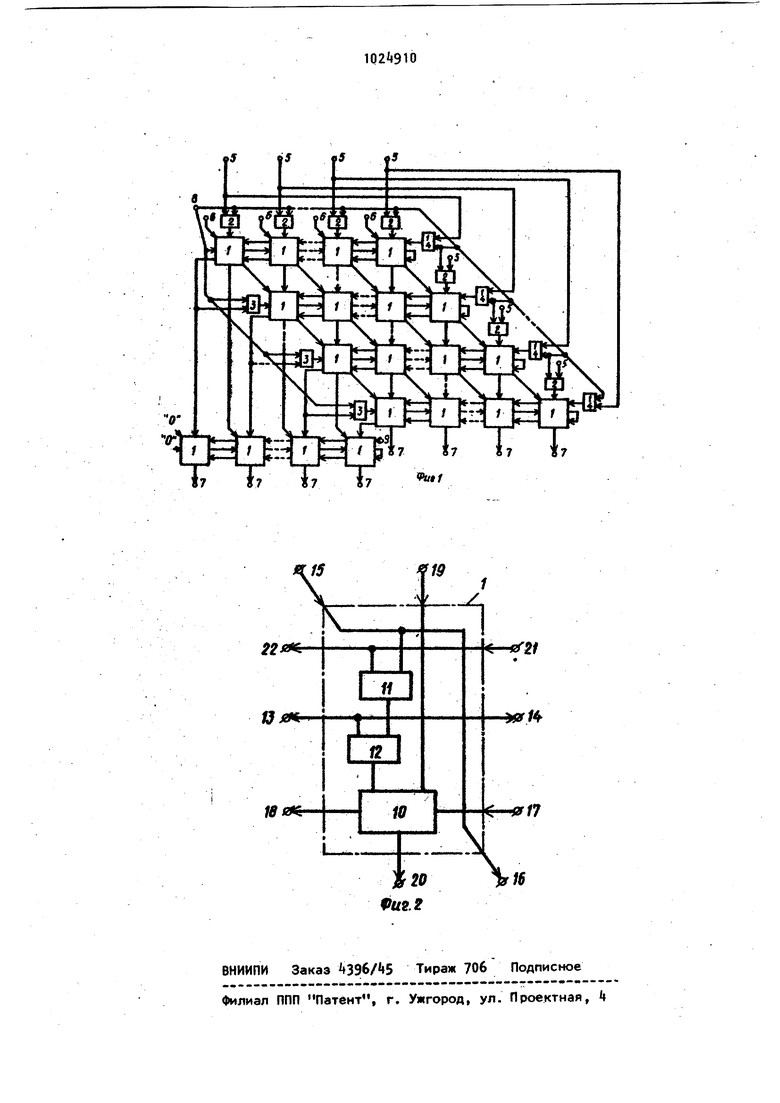

На фиг.1 приведена структурная схема матричного вычислительного устройства; на фиг.2 - функциональная схема ячейки.

Матричное вычислительное устройство содержит ячейки 1, элементы И 2, элементы ИЗ элементы ИЛИ k, входы операндов 5 и 6, выходы 7 результата, управляющие входы 8 и 9. Ячейка 1 содержит одноразрядный сумматор 10, элемент И 11, элемент ИСКЛОЧАЮЩЕЕ . ИЛИ 12, первый вход 13 первый выход И, второй вход 15, второй выход 1б, третий вход 17, третий выход 18, четвертый вход 19, четвертый выход 20, пятый вход 21, пятый выход 22. Матричное вычислительное устройство оперирует только с мантиссами прямых кодов операндовс Для формирования знака результата, если это необходимо, используют еще один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого должны бытъ подключены к знаковым разрядам операндов.

Управление матричным вычислительным устройством осуществляется через входы управления 8 и Э При делении на входы 8 и 9 подают код 10, а при умножении - код 01.

Матричное вычислительное устройство работает Следующим образом.

При делении на входы 5 поступают (2N-.1) разрядов мантиссы делимого, а на входы 6 - (N-1) разрядов мантиссы делителя. Причем на вход 6, подключенный к ячейкам 1 первого столбца, подают сигнал логического О, а на остальные входы 6 - соответствующие разряды мантиссы делителя. 6 связи с этим, делимое, по отношению к делителю, вступает в операцию предва- рительно сдвинутым на один разряд влево.

Так как на входе 8 присутствует единичный сигнал, то в первой строке матрицы из сдвинутого делимого вычитается делитель. В дальнейшем операция деления выполняется по алгоритму без восстановления остатка. Вычитанию из очередного остатка делителя соответствует суммирование дополнительного кода делителя.

Предполагается, что делимое и делитель нормализованные дроби, причем делимое меньше делителя, в противном случае делимое по отношению к делите

лю на разряд влево не сдвигается. На вход 5 первого элемента И 2 подают первый сигнал, тогда выход 7, подключенный к четвертому выходу первой ячейки 1 дополнительной строки, является выходом сигнала о том, что частное больше или равно единице, а (N-1) разрядов частного снимают с четвертых выходов остальных ячеек 1

дополнительной строки.

При умножении на входы 5 подают N разрядов мантиссы множителя, а на входа -6 - N разрядов мантиссы множит мого. Умножение выполняется,начиная

со старших разрядов множителя. Мантисса произведения в 2N разрядов формируется на выходах 7 устройства.

При делении (на входах 8 и 9 код .10)Элемент И 11 открыт сигналом е ир ничного уровня на входе 21 ячейки 1 и на его выход поступает бит с входа 15. умножении элементы И 11 управляются разрядами множителя, а элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 12 за счет

наличия нулевого сигнала на входе 13 ячейки 1 выполняют функции повторителейо

Наличие в ячейках 1 дополнительной строки Элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

не обязательно.

Таким образом, за счет незначи-, тельного увеличения оборудования существенно расширяются функциональные возможности устройства. Кроме деления и умножения, предлагаемое устройство позволяет выполнять сдвиги в сторону младших разрядов, а наличие до полнительной строки ячеек 1 предоставляет широкие Возможности для организации различных видов округления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропроцессорные БИС и микро-ЭВМ: построение и применение | |||

| Под ред | |||

| А.А.Васенкова | |||

| М., Советское радио, 1980, с.102, рис.3.19 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронная арифметика.М., Радио и связь, 1981, с.238, рис.5, (прототип). | |||

Авторы

Даты

1983-06-23—Публикация

1982-02-25—Подача