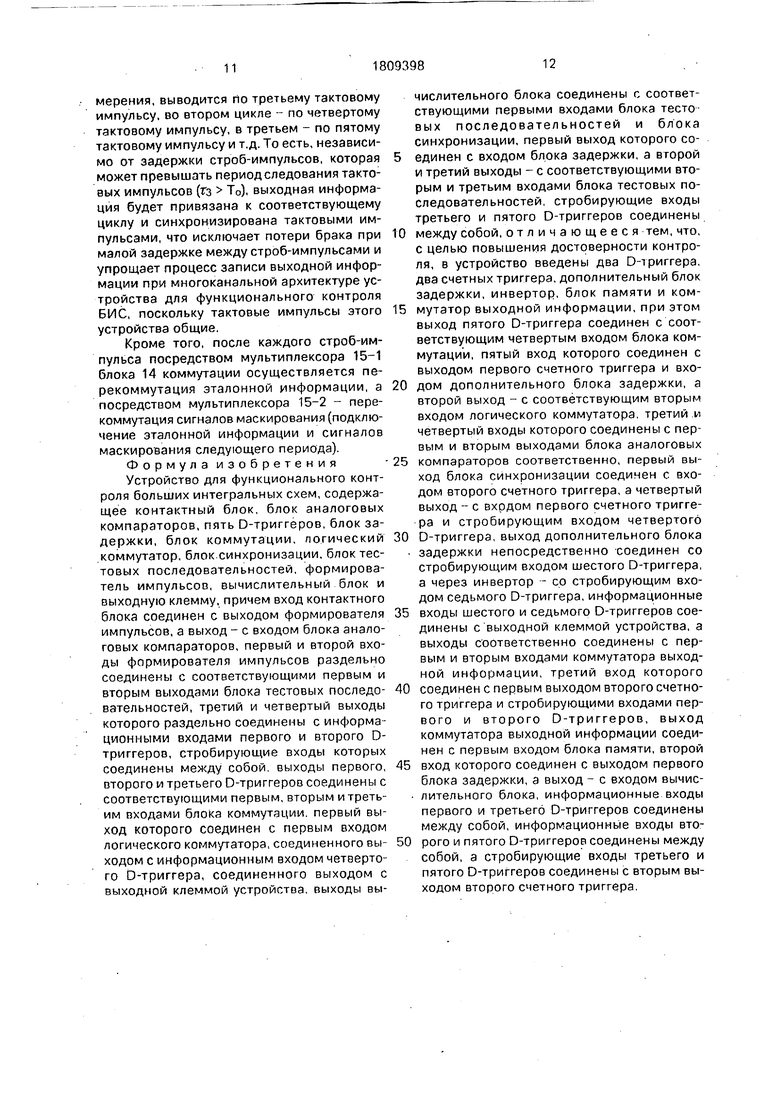

Блок 1 аналоговых компараторов состоит из операционных усилителей 27, 28, первые входы которых объединены и подключены к выходу контактного блока 18, а вторые входы раздельно соединены с клеммами для подключения источников опорных напряжений Uon.1, Uon.2 соответственно, предназначенных для задания программируемых значений логических уровней 1 и О соответственно. Вход контактного блока 18 соединен с выходом формирователя 19 импульсов, первый и второй входы которого раздельно соединены с соответствующими выходами блока 20 тестовых последовательностей, третий и четвертый входы формирователя 19 импульсов раздельно соединены с клеммами для подключения источников UB, UH опорных напряжений верхнего и нижнего уровней соответственно. Третий выход блока 20 тестовых последовательностей соединен с объединенными информационными входами D-триггеров 2, 3, а четвертый выход - с объединенными информационными входами D-триггеров 4, 5. Выходы О-триггеров 2...5 раздельно соединены с первыми и вторыми входами мультиплексоров 15-1, 15-2, образующими с первого по четвертый входы блока 14 коммутации, третьи объединенные входы мультиплексоров 15-1, 1.5-2, образующие пятый вход блока 14 коммутации, подключены к выходу счетного триггера 9 и входу блока 12 задержки. Первый и второй выходы блока 14 коммутации раздельно соединены с соответствующими входами логического коммутатора 16, третий и четвертый входы которого соединены с выходами усилителей 27, 28 соответственно блока 1 аналоговых компараторов, а выход - с информационным входом D-триггера 6, выход которого соединен с объединенными информационными входами D-триггеров 7, 8 и выходной клеммой 23. Выходы D-триггеров 7, 8 раздельно соединены с первым и вторым входами коммутатора 17 выходной информации, третий вход которого соединен с первым (прямым) выходом счетного триггера 10 и объединенными стробирую- щмми входами D-триггеров 2, 4. Объединённые стробирующие входы D-триггеров З, 5 соединены со вторым выходом счетного триггера ТО, вход которого соединен с первым выходом блока 21 синхронизации и входом блока 11 задержки. Второй и третий выходы блока 21 синхронизации раздельно соединены с соответствующими входами блока 20 тестовых последовательностей, а четоертый выход - со стробирующим входом D-триггера б и входом счетного триггера 9. Выход блока 12 задержки непосредственно.

соединен со стробирующим входом D- триггера 7 и через инвертор 13 - со стробирующим входом D-триггера 8. Выход коммутатора 17 выходной информации соединен с первым входом блока 22 памяти, второй вход которого соединен с выходом блока 11 задержки, а выход - со входом блока 25 согласования, имеющего двусторонние-связи о ЭВМ 26 вычислительного

0 блока 24 и соединенного своими выходами

с объединенными группами входов блока 20

тестовых последовательностей и блока 21

синхронизации, .

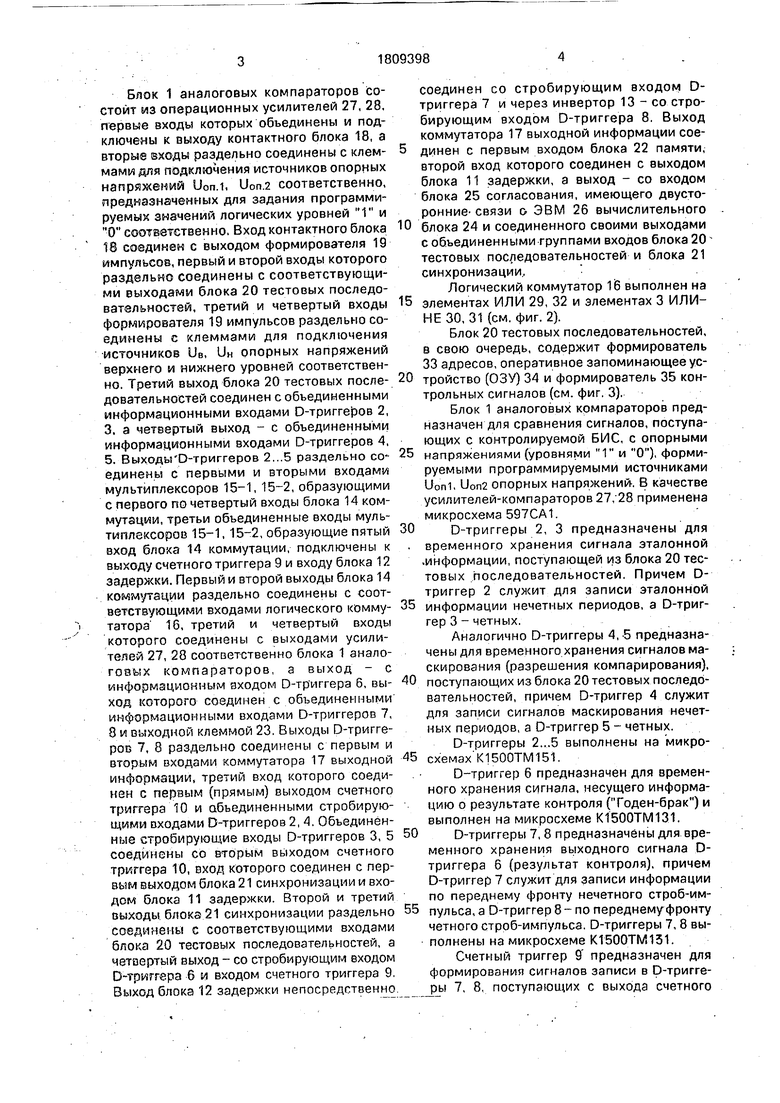

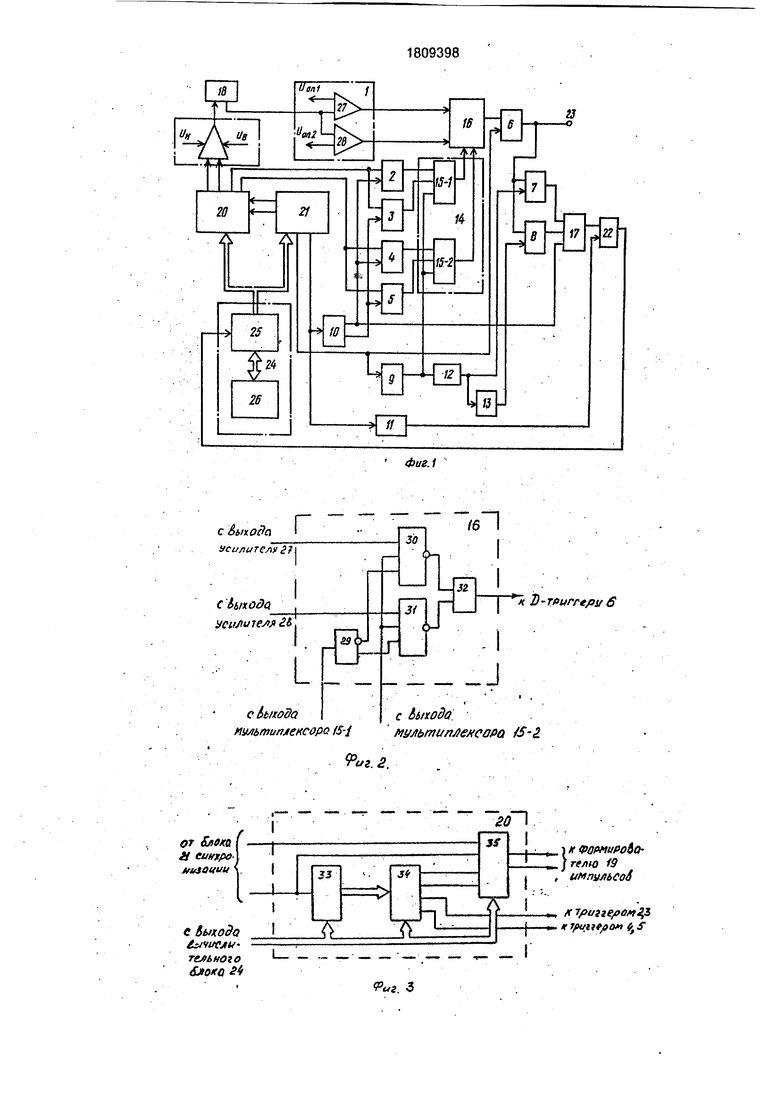

Логический коммутатор 16 выполнен на

5 элементах ИЛИ 29, 32 и элементах 3 ИЛИ- НЕЗО, 31 (см. фиг. 2).

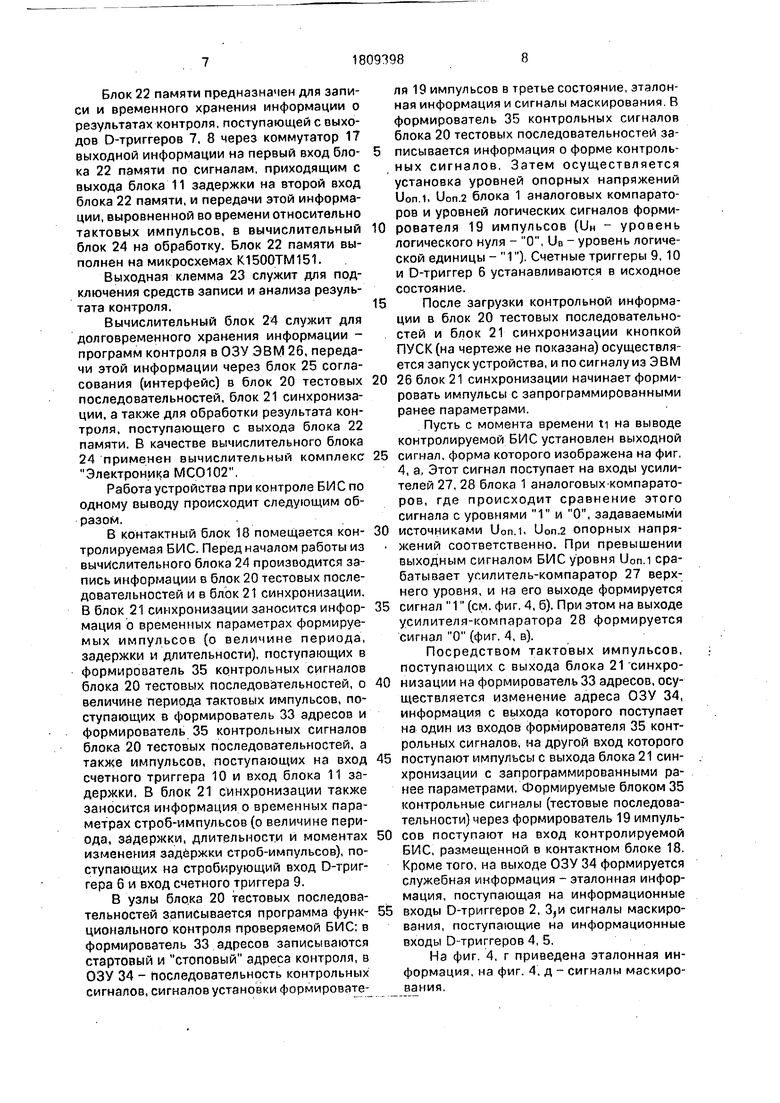

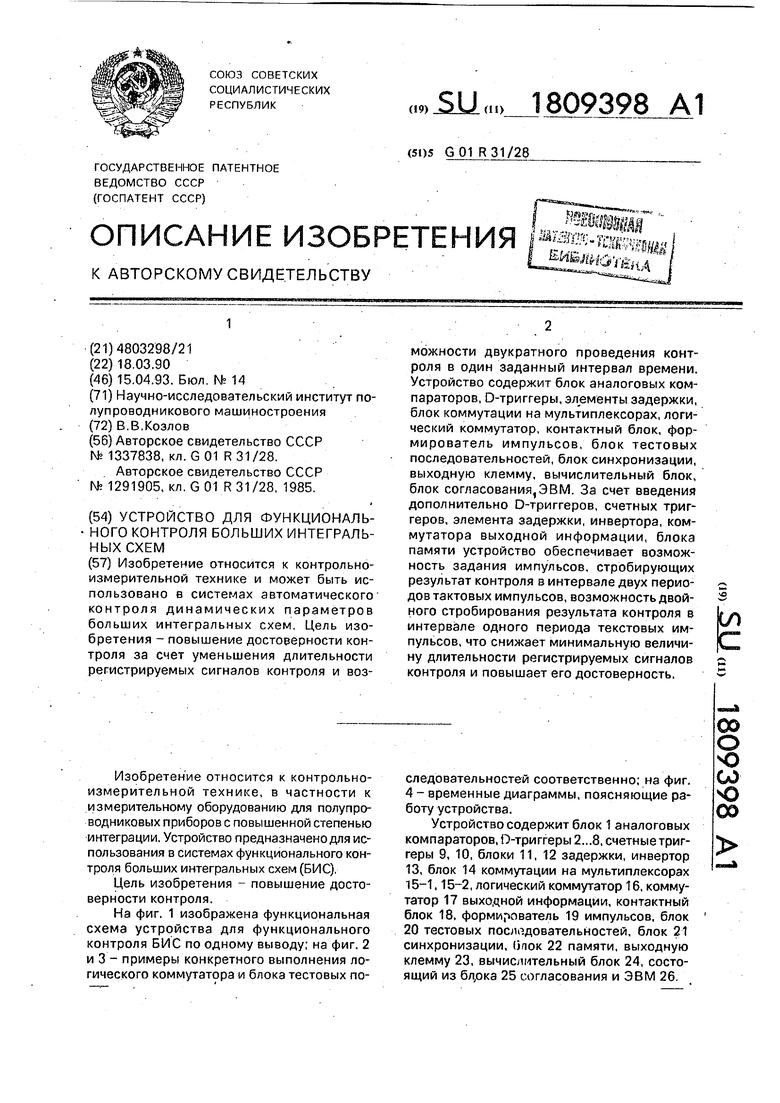

Блок 20 тестовых последовательностей, в свою очередь, содержит формирователь 33 адресов, оперативное запоминающее ус0 тройство (ОЗУ) 34 и формирователь 35 контрольных сигналов (см. фиг. 3),

Блок 1 аналоговых компараторов предназначен для сравнения сигналов, поступающих с контролируемой БИС, с опорными

5 напряжениями (уровнями 1 и О), формируемыми программируемыми источниками Uoni, Uon2 опорных напряжений. В качестве усилителей-компараторов 27/28 применена микросхема 597СА1.

0 D-триггеры 2, 3 предназначены для . временного хранения сигнала эталонной .информации, поступающей из блока 20 тестовых последовательностей. Причем D- триггер 2 служит для записи эталонной

5 информации нечетных периодов, а D-триг- гер 3 - четных.

Аналогично D-триггеры 4,5 предназначены для временного хранения сигналов маскирования (разрешения компарирования),

0 поступающих из блока 20 тестовых последовательностей, причем D-триггер 4 служит для записи сигналов маскирования нечетных периодов, а D-триггер 5 - четных.

D-триггеры 2...5 выполнены на микро5 схемах К1500ТМ151.

D-триггер 6 предназначен для временного хранения сигнала, несущего информацию о результате контроля (Годен-брак) и выполнен на микросхеме К1500ТМ131.

0 D-триггеры 7, 8 предназначены для временного хранения выходного сигнала D- триггера 6 (результат контроля), причем D-триггер 7 служит для записи информации по переднему фронту нечетного строб-им5 пульса, а D-триггер 8 - по переднемуфронту четного строб-импульса. D-триггеры 7, 8 выполнены на микросхеме К1500ТМ131.

Счетный триггер 9 предназначен для формирования сигналов записи в D-триггеры 7, 8, поступающих с выхода счетного

триггера 9 через блок 12 задержки на стробирующий вход D-триггера 7 непосредственно, а на стробирующий вход D-триггера 8 - через инвертор 13. Кроме того, счетный триггер 9 служит для управления работой мультиплексоров 15-1, 15-2 блока 14 коммутации, формируя сигналы разрешения трансляции сигналов с выходов D-триггеров 2...5 на входы логического коммутатора 16.

Счетный триггер 10 предназначен для формирования сигналов записи информации в D-триггеры 2...5, вырабатываемых по переднему фронту тактовых импульсов, поступающих на вход счетного триггера 10 с выхода блока 21 синхронизации, а также для формирования сигналов управления коммутатором 17 выходной информации.

Счетные триггеры 9, 10 реализованы на микросхеме К1500ТМ131.

Блок 11 задержки предназначен для увеличения диапазона установки строб-импульса в устройстве и реализован на микросхеме. Ю1500; М 102.

Блок 12 задержки предназначен для задержки выходного сигнала счетного триггера 9 на время, превышающее время распространения сигнала через D-триггер 6. Величина задержки блока 12 задержки для надежной записи в D-триггеры 7. 8 составляет около 1,0-1,5 не. Блок 12 задержки реализован на микросхеме К1500ЛМ102.

Инвертор 13 предназначен для инверсии сигнала с выхода блока 12 задержки и передачи его на стробирующий вход D-триггера 8. Инвертор 13 выполнен на микросхеме К1500 Л М102.

Блок 14 коммутации предназначен для поочередного пропускания служебной информации с выходов D-триггеров 2...5 на входы логического коммутатора 16, причем мультиплексор 15-1 служит для пропускания эталонной информации с выходов D- триггеров 2, 3 на первый вход логического коммутатора 16, а мультиплексор 15-2 - для пропускания сигналов маскирования с выходов D-триггеров 4, 5 на второй вход логического коммутатора 16. Мультиплексоры 15-1, 15-2 блока 14 коммутации реализованы на микросхемах К1500КП163.

Логический коммутатор 16 предназначен для пропускания сигналов с выходов усилителей 27, 28 блока 1 аналоговых компараторов через логические элементы 3 ИЛИ-НЕ 30, 31 и элемент ИЛИ 32 на информационный вход D-триггера 6 в зависимости от служебной информации - эталонной информации, поступающей через элемент ИЛИ 29 с выхода, мультиплексора 15-1 блока 14 коммутации на вторые входы элементов 3 ИЛИ-НЕ 30, 31, и сигналов маскирования, поступающих с выхода мультиплексора 15-2 на объединенные третьи входы логических элементов 3 ИЛИ-НЕ 30, 31. Для реализации логического коммута- 5 тора 16 использованы микросхемы К1500ЛМ102.

Коммутатор 17 выходной информации предназначен для поочередного пропускания сигналов результата контроля с выходов

0 D-триггеров на вход блока 22 памяти в зависимости от сигналов управления, поступающих с прямого выхода счетного триггера 10 на третий вход коммутатора 17 выходной информации, реализованного на микросхе5 ме К15СОЛМ102..

Контактный блок 18 служит для обеспечения подключения выводов контролируемой БИС (в нашем случае одного вывода) ко входу блока 1 аналоговых компараторов и

0 выходу формирователя 19 импульсов, служащего для формирования импульсных сигналов с уровнями выходных напряжений, соответствующими заданным опорным уровням напряжений высокого и низкого

5 уровней UB, UH соответственно, а также для задания формируемых напряжений на вывод контролируемой БИС. В качестве контактного блока использовано стандартное подключающее устройство типа УК, а фор0 мирователь 19 импульсов реализован по схеме формирователя типа три состояния. Блок 20 тестовых последовательностей предназначен для формирования контрольных последовательностей, поступающих на

5 входы формирователя 19 импульсов, и установки (перевода) последнего в третье состояние, формирования сигналов эталонной информации, поступающих через D-триггеры 2, 3 и мультиплексор 15-1 блока 14 ком0 мутации на вход логического элемента ИЛИ 29 логического коммутатора 16 для осуществления коммутации сигналов блока 1 аналоговых компараторов. Кроме того, блок 20 служит для формирования сигналов маски5 рования. поступающих с выхода ОЗУ 34 через D-триггеры 4, 5, мультиплексор 15-2 блока 14 коммутации на входы элементов 3 ИЛИ-НЕ 30,31 логического коммутатора 16. Формирователь 33 адресов совместно с

0 ОЗУ 34 блока 20 тестовых последовательностей представляет собой буферную память, выполненную на микросхемах К1500РУ415 го стандартными сигналами управления. Блок 21 синхронизации предназначен

5 для формирования тактовых импульсов с программируемыми временными параметрами: задержками и длительностями, обеспечивающими тактирование и построение временной диаграммы работы устройства при функциональном контроле БИС.

Блок 22 памяти предназначен для записи и временного хранения информации о результатах контроля, поступающей с выходов D-триггеров 7, 8 через коммутатор 17 выходной информации на первый вход бло- ка 22 памяти по сигналам, приходящим с выхода блока 11 задержки на второй вход блока 22 памяти, и передачи этой информации, выровненной во времени относительно тактовых импульсов, в вычислительный блок 24 на обработку. Блок 22 памяти выполнен на микросхемах К1500ТМ151.

Выходная клемма 23 служит для подключения средств записи и анализа результата контроля.

Вычислительный блок 24 служит для долговременного хранения информации - программ контроля в ОЗУ ЭВМ 26, передачи этой информации через блок 25 согласования (интерфейс) в блок 20 тестовых последовательностей, блок 21 синхронизации, а также для обработки результата контроля, поступающего с выхода блока 22 памяти. В качестве вычислительного блока 24 применен вычислительный комплекс Электроника МС0102.

Работа устройства при контроле БИС по одному выводу происходит следующим образом,

В контактный блок 18 помещается кон- тролируемая БИС. Перед началом работы из вычислительного блока 24 производится запись информации в блок 20 тестовых последовательностей и в блок 21 синхронизации. В блок 21 синхронизации заносится инфор- мация о временных параметрах формируемых импульсов (о величине периода, задержки и длительности), поступающих в формирователь 35 контрольных сигналов блока 20 тестовых последовательностей, о величине периода тактовых импульсов, поступающих в формирователь 33 адресов и формирователь 35 контрольных сигналов блока 20 тестовых последовательностей, а также импульсов, поступающих на вход счетного триггера 10 и вход блока 11 задержки. В блок 21 синхронизации также заносится информация о временных параметрах строб-импульсов (о величине периода, задержки, длительности и моментах изменения задержки строб-импульсов), поступающих на стробирующий вход D-триг- гера 6 и вход счетного триггера 9.

В узлы блока 20 тестовых последовательностей записывается программа функ- ционального контроля проверяемой БИС: в формирователь 33 адресов записываются стартовый и столовый адреса контроля, в ОЗУ 34 - последовательность контрольных сигналов, сигналов установки формирователя 19 импульсов в третье состояние, эталонная информация и сигналы маскирования. В формирователь 35 контрольных сигналов блока 20 тестовых последовательностей записывается информация о форме контрольных сигналов. Затем осуществляется установка уровней опорных напряжений Uon.i, Uon.2 блока 1 аналоговых компараторов и уровней логических сигналов формирователя 19 импульсов (UH - уровень логического нуля - О, UB - уровень логической единицы - 1). Счетные триггеры 9,10 и D-триггер 6 устанавливаются в исходное состояние.

После загрузки контрольной информации в блок 20 тестовых последовательностей и блок 21 синхронизации кнопкой ПУСК (на чертеже не показана) осуществляется запуск устройства, и по сигналу из ЭВМ 26 блок 21 синхронизации начинает формировать импульсы с запрограммированными ранее параметрами.

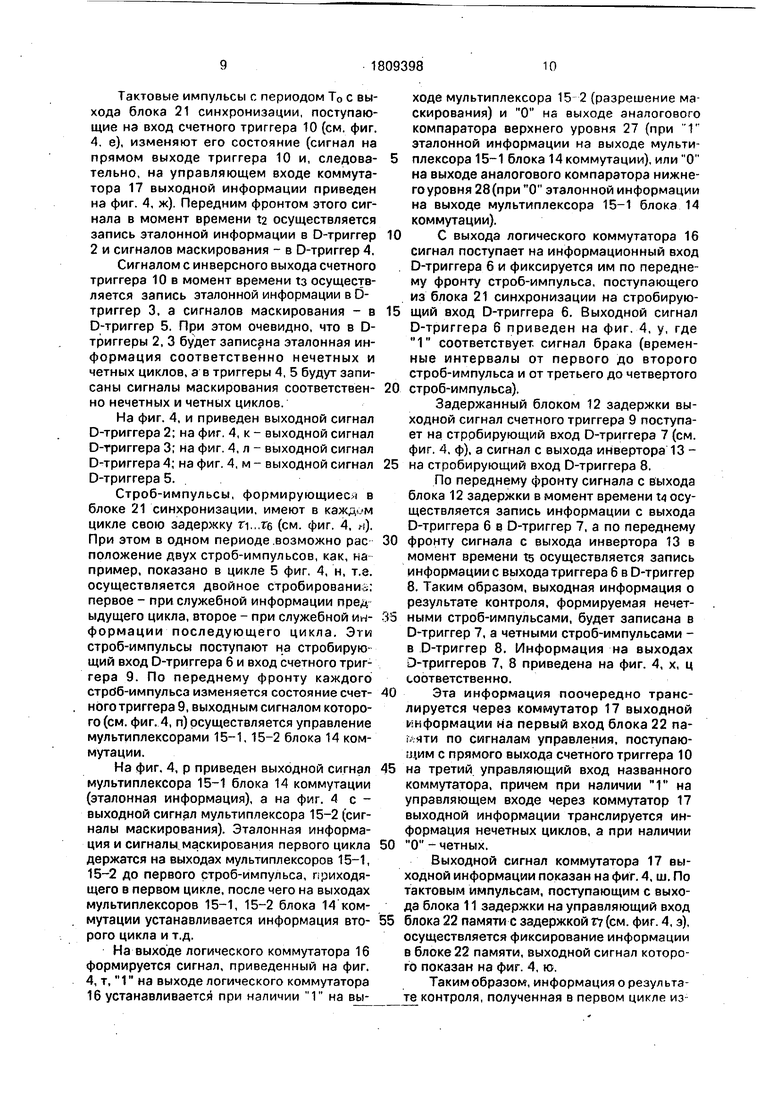

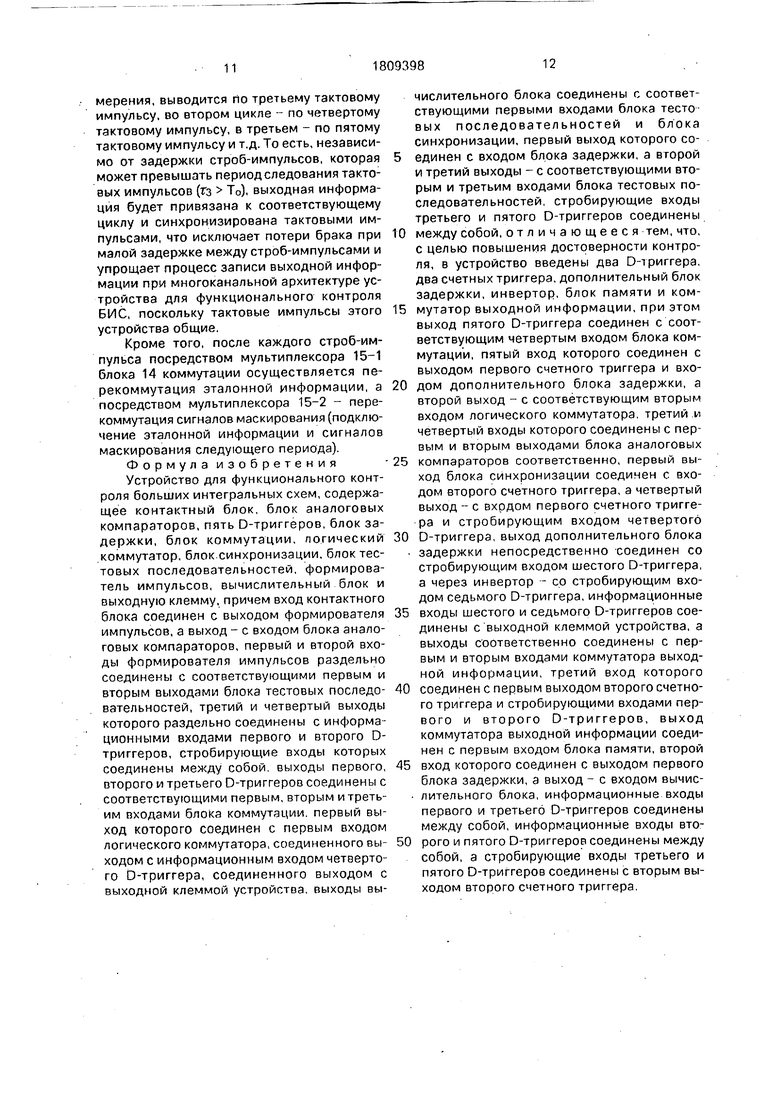

Пусть с момента времени ti на выводе контролируемой БИС установлен выходной сигнал, форма которого изображена на фиг, 4, а, Этот сигнал поступает на входы усилителей 27, 28 блока 1 аналоговых-компарато- ров, где происходит сравнение этого сигнала с уровнями 1 и О, задаваемыми источниками Uon.1, Uon.2 опорных напряжений соответственно. При превышении выходным сигналом БИС уровня Uon.1 срабатывает усилитель-компаратор 27 верхнего уровня, и на его выходе формируется сигнал 1 (см. фиг, 4, б). При этом на выходе усилителя-компаратора 28 формируется сигнал О (фиг. 4, в).

Посредством тактовых импульсов, поступающих с выхода блока 21 синхронизации на формирователь 33 адресов, осуществляется изменение адреса ОЗУ 34, информация с выхода которого поступает на один из входов формирователя 35 контрольных сигналов, на другой вход которого поступают импульсы с выхода блока 21 синхронизации с запрограммированными ранее параметрами, Формируемые блоком 35 контрольные сигналы (тестовые последовательности) через формирователь 19 импульсов поступают на вход контролируемой БИС, размещенной в контактном блоке 18. Кроме того, на выходе ОЗУ 34 формируется служебная информация - эталонная информация, поступающая на информационные входы D-триггеров 2, 3,и сигналы маскирования, поступающие на информационные входы D-триггеров 4, 5.

На фиг. 4, г приведена эталонная информация, на фиг. 4, д - сигналы маскирования.

Тактовые импульсы с периодом Т0 с выхода блока 21 синхронизации, поступающие на вход счетного триггера 10 (см. фиг. 4. е), изменяют его состояние (сигнал на прямом выходе триггера 10 и, следовательно, на управляющем входе коммутатора 17 выходной информации приведен на фиг. 4, ж). Передним фронтом этого сигнала в момент времени t2 осуществляется запись эталонной информации в D-триггер 2 и сигналов маскирования - в D-триггер 4,

Сигналом с инверсного выхода счетного триггера 10 в момент времени гз осуществляется запись эталонной информации в D- триггер 3, а сигналов маскирования - в D-триггер 5. При этом очевидно, что в D- триггеры 2, 3 будет записана эталонная информация соответственно нечетных и четных циклов, а в триггеры 4, 5 будут записаны сигналы маскирования соответственно нечетных и четных циклов.

На фиг. 4, и приведен выходной сигнал D-триггера 2; на фиг. 4, к - выходной сигнал D-триггера З; на фиг. 4, л - выходной сигнал D-триггера 4; на фиг. 4, м - выходной сигнал D-триггера 5.

Строб-импульсы, формирующиеся в блоке 21 синхронизации, имеют в каждом цикле свою задержку n.,.re (см. фиг. 4, и). При этом в одном периоде .возможно рас положение двух строб-импульсов, как, на пример, показано в цикле 5 фиг, 4, н, т.е. осуществляется двойное стробированиа: первое - при служебной информации пред ыдущего цикла, второе - при служебной информации последующего цикла. Эти строб-импульсы поступают на стробирую- щий вход D-триггера б и вход счетного триггера 9. По переднему фронту каждого стрбб-импульсз изменяется состояние счетного триггера 9, выходным сигналом которого (см. фиг. 4, п) осуществляется управление мультиплексорами 15-1, 15-2 блока 14 коммутации.

На фиг. 4, р приведен выходной сигнал мультиплексора 15-1 блока 14 коммутации (эталонная информация), а на фиг. 4с- выходной сигнал мультиплексора 15-2 (сигналы маскирования). Эталонная информация и сигналы,маскирования первого цикла держатся на выходах мультиплексоров 15-1, 15-2 до первого строб-импульса, приходящего в первом цикле, после чего на выходах мультиплексоров 15-1, 15-2 блока 14 коммутации устанавливается информация второго цикла и т.д.

На выходе логического коммутатора 16 формируется сигнал, приведенный на фиг. 4, т, 1 на выходе логического коммутатора 16 устанавливается при наличии 1 на выходе мультиплексора 152 (разрешение маскирования) и О на выходе аналогового компаратора верхнего уровня 27 (при 1 эталонной информации на выходе мульти- 5 плексора 15-1 блока 14 коммутации), или О на выходе аналогового компаратора нижнего уровня 28(при О эталонной информации на выходе мультиплексора 15-1 блока 14 коммутации).

0 С выхода логического коммутатора 16 сигнал поступает на информационный вход . D-триггера б и фиксируется им по переднему фронту строб-импульса, поступающего из блока 21 синхронизации на стробирую5 щий вход D-триггера б. Выходной сигнал D-триггера 6 приведен на фиг. 4, у, где 1 соответствует, сигнал брака (временные интервалы от первого до второго строб-импульса и от третьего до четвертого

0 строб-импульса).

Задержанный блоком 12 задержки выходной сигнал счетного триггера 9 поступает на стррбирующий вход D-триггера 7 (см. фиг. 4, ф), а сигнал с выхода инвертора 13 5 на стробирующий вход D-триггера 8.

По переднему фронту сигнала с выхода блока 12 задержки в момент времени t4 осуществляется запись информации с выхода D-триггера 6 в D-триггер 7, а по переднему

0 фронту сигнала с выхода инвертора 13 в момент времени ts осуществляется запись информации с выхода триггера 6 в D-триггер 8. Таким образом, выходная информация о результате контроля, формируемая нечет5 ными строб-импульсами, будет записана в D-триггер 7, а четными строб-импульсами - в D-триггер 8. Информация на выходах D-триггеров 7, 8 приведена на фиг. 4, х, ц соответственно.

0 Эта информация поочередно транслируется через коммутатор 17 выходной информации на первый вход блока 22 па- ляти по сигналам управления, поступающим с прямого выхода счетного триггера 10

5 на третий управляющий вход названного коммутатора, причем при наличии 1 на управляющем входе через коммутатор 17 выходной информации транслируется информация нечетных циклов, а при наличии

0 О - четных.

Выходной сигнал коммутатора 17 выходной информации показан на фиг. 4, ш. По тактовым импульсам, поступающим с выхода блока 11 задержки на управляющий вход

5 блока 22 памяти с задержкой г/ (см. фиг. 4, э), осуществляется фиксирование информации в блоке 22 памяти, выходной сигнал которого показан на фиг. 4, ю.

Таким образом, информация о результате контроля, полученная в первом цикле из

мерения, выводится по третьему тактовому импульсу, во втором цикле - по четвертому тактовому импульсу, в третьем - по пятому тактовому импульсу и т.д. То есть, независимо от задержки строб-импульсов, которая может превышать период следования тактовых импульсов (тз То), выходная информация будет привязана к соответствующему циклу и синхронизирована тактовыми импульсами, что исключает потери брака при малой задержке между строб-импульсами и упрощает процесс записи выходной информации при многоканальной архитектуре устройства для функционального контроля БИС, поскольку тактовые импульсы этого устройства общие.

Кроме того, после каждого строб-импульса посредством мультиплексора 15-1 блока 14 коммутации осуществляется перекоммутация эталонной информации, а посредством мультиплексора 15-2 - перекоммутация сигналов маскирования (подключение эталонной информации и сигналов маскирования следующего периода).

Формула изобретения Устройство для функционального контроля больших интегральных схем, содержащее контактный блок, блок аналоговых компараторов, пять D-триггеров, блок задержки, блок коммутации, логический коммутатор, блок синхронизации, блок тестовых последовательностей, формирователь импульсов, вычислительный блок и выходную клемму, причем вход контактного блока соединен с выходом формирователя импульсов, а выход - с входом блока аналоговых компараторов, первый и второй входы формирователя импульсов раздельно соединены с соответствующими первым и вторым выходами блока тестовых последо- вательностей, третий и четвертый выходы которого раздельно соединены с информационными входами первого и второго D- триггеров, стробирующие входы которых соединены между собой, выходы первого, второго и третьего D-триггеров соединены с соответствующими первым, вторым и третьим входами блока коммутации, первый выход которого соединен с первым входом логического коммутатора, соединенного вы- ходом с информационным входом четвертого D-триггера, соединенного выходом с выходной клеммой устройства, выходы вычислительного блока соединены с соответствующими первыми входами блока тестовых последовательностей и блока синхронизации, первый выход которого соединен с входом блока задержки, а второй и третий выходы - с соответствующими вторым и третьим входами блока тестовых последовательностей, стробирующие входы третьего и пятого D-триггеров соединены между собой, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены два D-триггера, два счетных триггера, дополнительный блок задержки, инвертор, блок памяти и коммутатор выходной информации, при этом выход пятого D-триггера соединен с соответствующим четвертым входом блока коммутации, пятый вход которого соединен с выходом первого счетного триггера и входом дополнительного блока задержки, а второй выход - с соответствующим вторым входом логического коммутатора, третий .и четвертый входы которого соединены с первым и вторым выходами блока аналоговых компараторов соответственно, первый выход блока синхронизации соединен с входом второго счетного триггера, а четвертый выход - с входом первого счетного триггера и стробирующим входом четвертого D-триггера, выход дополнительного блока задержки непосредственно соединен со стробирующим входом шестого D-триггера, а через инвертор - со стробирующим входом седьмого D-триггера, информационные входы шестого и седьмого D-триггеров соединены с выходной клеммой устройства, а выходы соответственно соединены с первым и вторым входами коммутатора выходной информации, третий вход которого соединен с первым выходом второго счетного триггера и стробирующими входами первого и второго D-триггеров, выход коммутатора выходной информации соединен с первым входом блока памяти, второй вход которого соединен с выходом первого блока задержки, а выход - с входом вычислительного блока, информационные входы первого и третьего D-триггеров соединены между собой, информационные входы второго и пятого D-триггеров соединены между собой, а стробирующие входы третьего и пятого D-триггеров соединены с вторым выходом второго счетного триггера.

Ф«г. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для ввода информации | 1989 |

|

SU1645949A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

Авторы

Даты

1993-04-15—Публикация

1990-03-18—Подача