Область применения устройства - вычислительная техника, а именно сосредоточенные многомашинные вычислительные комплексы с использованием компонентов, архитектурно совместимых с системой малых электронных вычислительных машин (СМ ЭВМ) и содержащих оперативные запоминающие устройства (ОЗУ) статического типа.

Цель изобретения - повышение быстродействия.

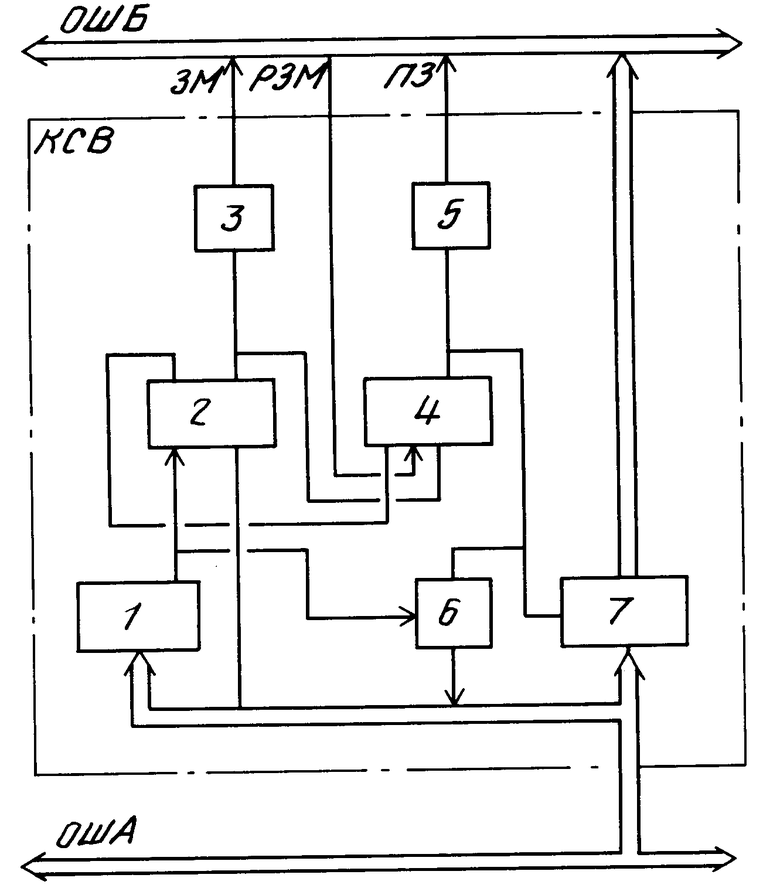

На чертеже дана блок-схема контроллера связи вычислительных машин по общей шине (КСВ).

Контроллер содержит селектор 1 адреса общей шины А (ОША), триггер 2 запроса магистрали (ЗМ) с формирователем 3 сигнала ЗМ к общей шине (ОШБ), триггер 4 подтверждения запроса (ПЗ) с формирователем 5 сигнала ПЗ к ОШБ, формирователь 6 сигнала адресуемого выхода триггера 4 в ОША, шинные формирователи 7 связи.

Обмен информацией выполняется в условиях запрета прерываний программы в ЭВМ с ОША, являющейся источником информации и инициатором обмена. ЭВМ с ОША, подготовившая информацию для передачи ее в ЭВМ с ОШБ, вырабатывает сигнал инициации обмена через формирователь 3, посылая по ОША на информационный вход триггера 2 единицу ЗМ. Факт поступления сигнала разрешения захвата магистрали ОШБ определяется ЭВМ-источником путем программного опроса формирователя 6, связанного по информационному входу с триггером 4, который служит для запоминания сигнала РЗМ (разрешения запроса магистрали), поступающего с ОШБ в условиях ПЗ от КСВ, инициирующего выдачу в ОШБ через формирователь 5 сигнала ПЗ и открывающего посредством формирователей 7 связи однонаправленный путь прохождения информации из ОША в ОШБ (кроме сигналов чтения данных и ответа), после чего вступает в действие программа ЭВМ-источника по передаче информации в ОШБ ЭВМ-приемника. Передача информации выполняется по команде "пересылка" в цикле записи по прямому доступу через ОШБ в ОЗУ ЭВМ-приемника по указанному в команде адресу приемника. Параллельно выполняется передача той же информации по тому же адресу в ОЗУ ЭВМ-источника. С помощью последовательности команд может быть передана требуемая совокупность слов информации. По окончании обмена информацией ЭВМ-источник снимает сигнал ЭВМ с ОШБ посылкой нулевой информации в триггер 2, что вызывает обнуление триггера 4 инверсным сигналом с выхода триггера 2, снятие сигнала ПЗ с выхода формирователя 5 и запирание шинных формирователей 7 связи. В ЭВМ-приемнике восстанавливается работа по программе, которая была приостановлена на все время обмена. ЭВМ-источник снимает запрет прерываний и продолжает работу по текущей программе.

После захвата общей шины передача одного слова осуществляется за время, равное времени выполнения команды "пересылка" в ЭВМ-источнике.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения магистрали приборного интерфейса с магистралью микро-ЭВМ | 1986 |

|

SU1368885A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для сопряжения магистрали эвм с магистралью внешних устройств | 1984 |

|

SU1229765A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

Область применения устройства - вычислительная техника, а именно сосредоточенные многомашинные вычислительные комплексы с использованием компонентов, архитектурно совместимых с системой малых ЭВМ (СМ ЭВМ) и содержащих оперативные запоминающие устройства (ОЗУ) статического типа. Цель изобретения состоит в повышении быстродействия (обмена информацией между вычислительными машинами комплекса). Устройство позволяет после захвата ОШБ выполнять передачу слова по одной команде "Пересылка" программы ЭВМ с ОША в цикле записи по прямому доступу в ОЗУ ЭВМ с ОШБ по адресу приемника команды параллельно передаче этой же информации по этому же адресу в ОЗУ ЭВМ с ОША. 1 ил.

КОНТРОЛЛЕР СВЯЗИ ВЫЧИСЛИТЕЛЬНЫХ МАШИН ПО ОБЩЕЙ ШИНЕ, содержащий селектор адреса и два триггера, причем информационный вход селектора адреса является входом контроллера для подключения к шине адреса первой вычислительной машине, а также формирователь сигнала запроса магистрали и формирователь сигнала подтверждения запроса, соединенные с выходами контроллера для подключения к одноименным входам второй вычислительной машины, отличающийся тем, что, с целью увеличения быстродействия, он содержит формирователь сигнала адресуемого выхода и шинные формирователи связи, причем информационные входы шинных формирователей связи являются входами контроллера для подключения к общей шине первой вычислительной машины, выходы шинных формирователей связи соединены с выходами контроллера для подключения к общей шине второй вычислительной машины, выход селектора адреса соединен с синхровходом первого триггера и с входом разрешения формирователя сигнала адресуемого выхода, выход которого подключен к выходу контроллера для подключения к общей шине передачи первой вычислительной машины, информационный вход первого триггера соединен с входом контроллера для подключения к общей шине первой вычислительной машины, инверсный выход первого триггера соединен с входом сброса второго триггера, информационный вход которого соединен с прямым выходом первого триггера и входом формирователя сигнала запроса магистрали, выход второго триггера соединен с информационным входом формирователя сигнала адресуемого выхода, входом управления шинных формирователей связи и входом формирователя сигнала подтверждения запроса, синхровход второго триггера соединен с входом контроллера для подключения к выходу разрешения запроса магистрали второй вычислительной машины.

| Устройство для организации внутрисистемной связи | |||

| Микропроцессорные средства и системы, 1988, N 2, с.55. |

Авторы

Даты

1994-09-30—Публикация

1991-06-28—Подача