Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля блоков и устройств дискретного действия при их производстве и эксплуатации.

Цель изобретения - увеличение полноты контроля.

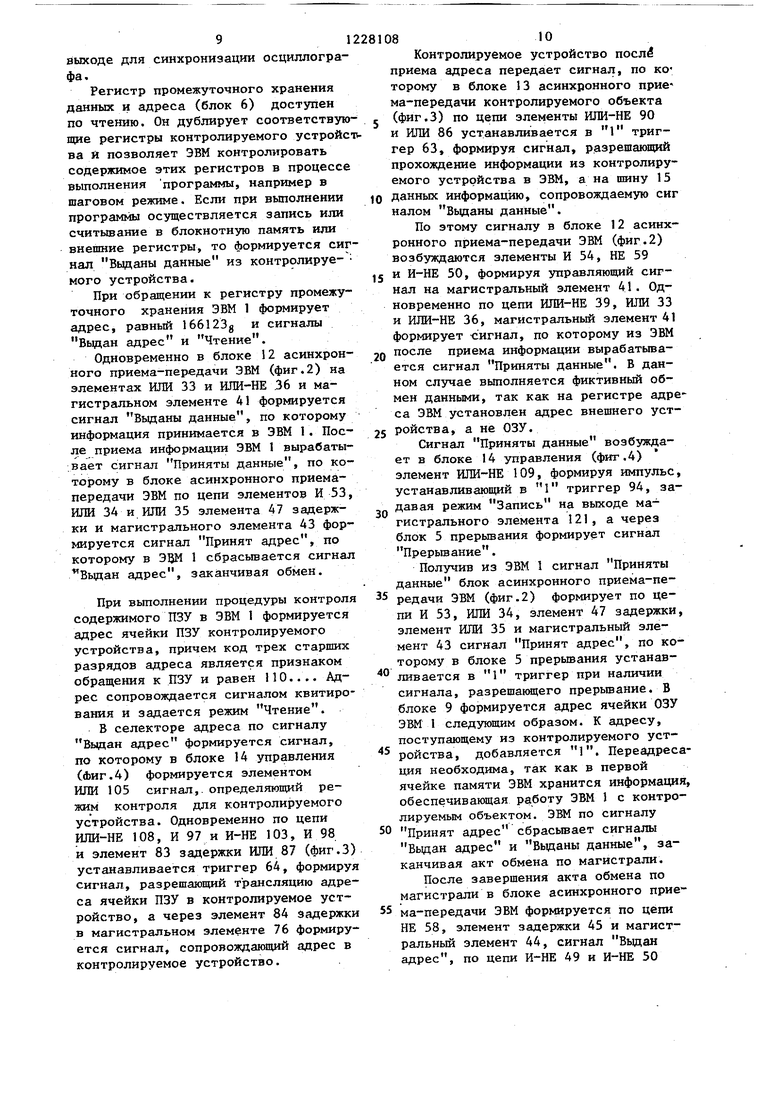

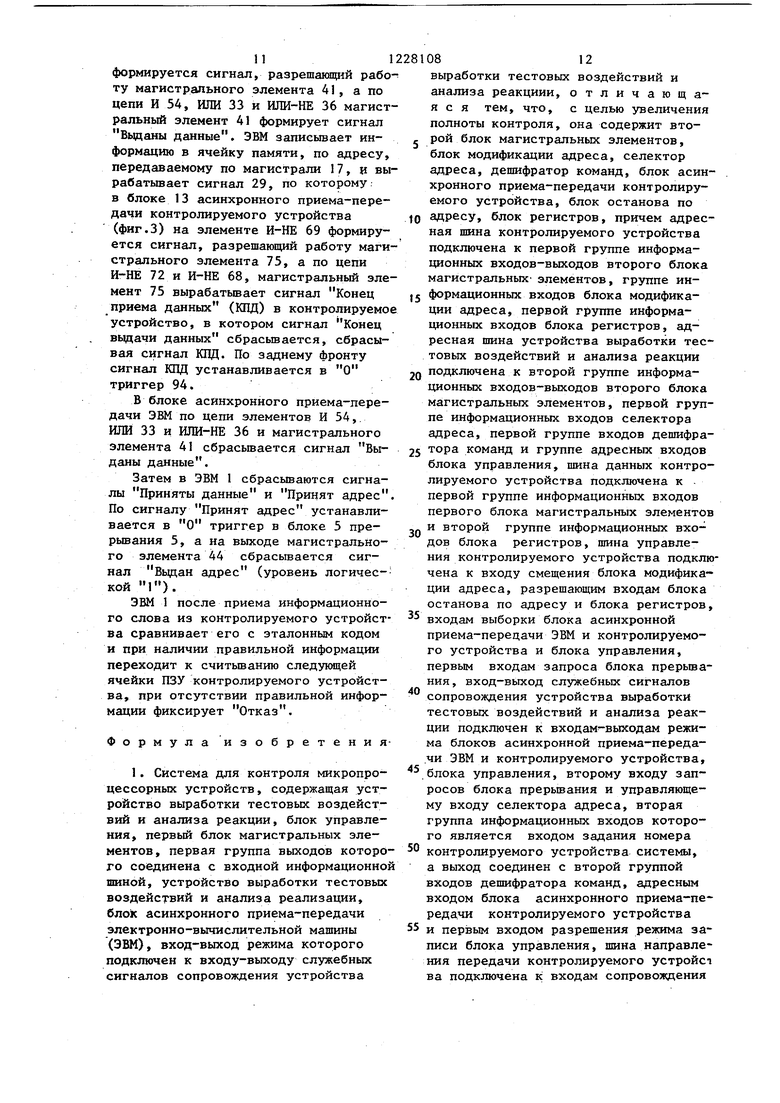

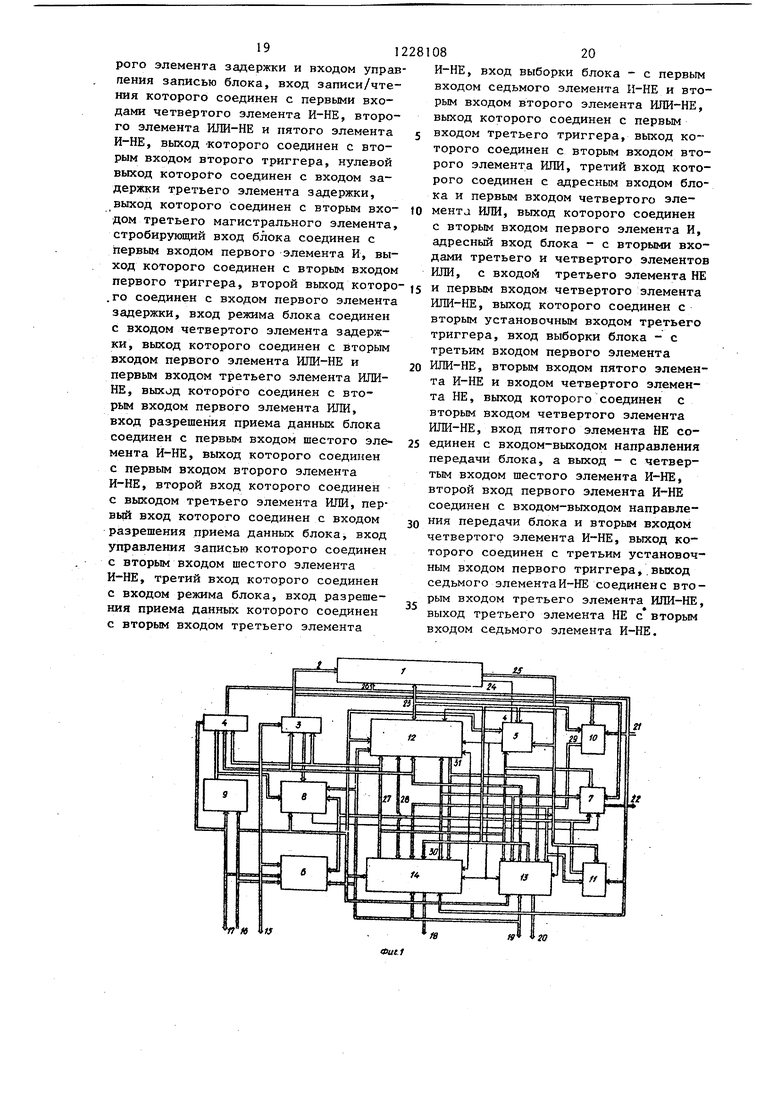

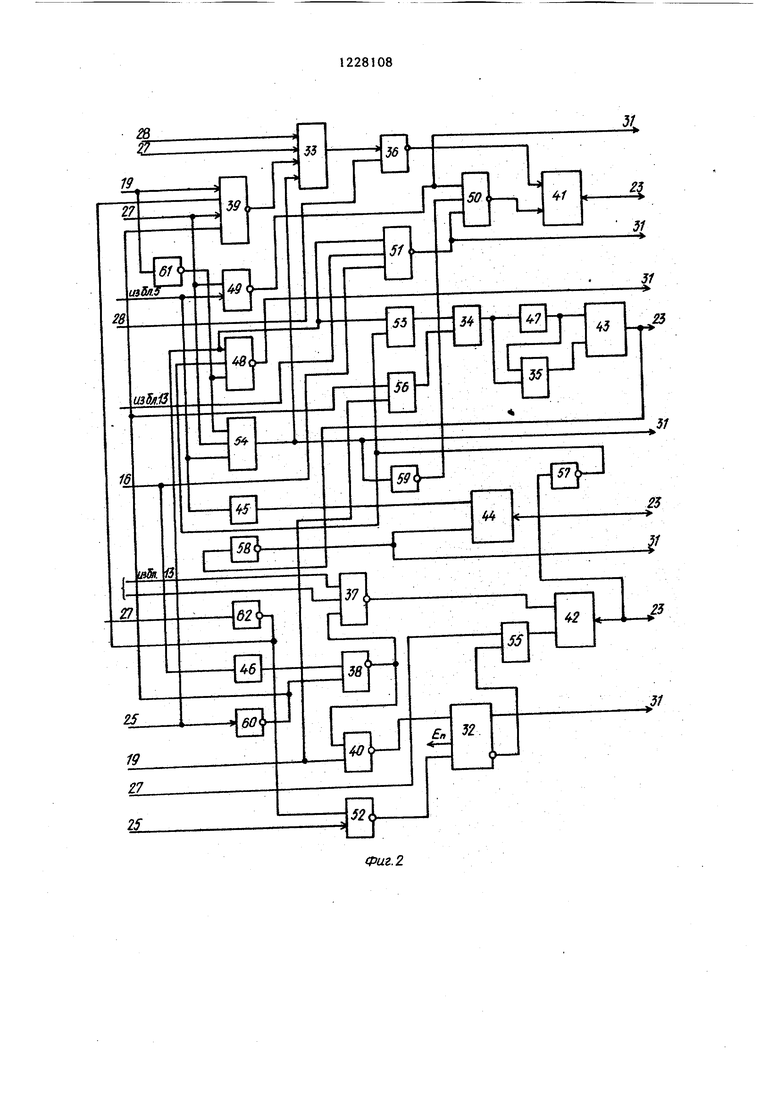

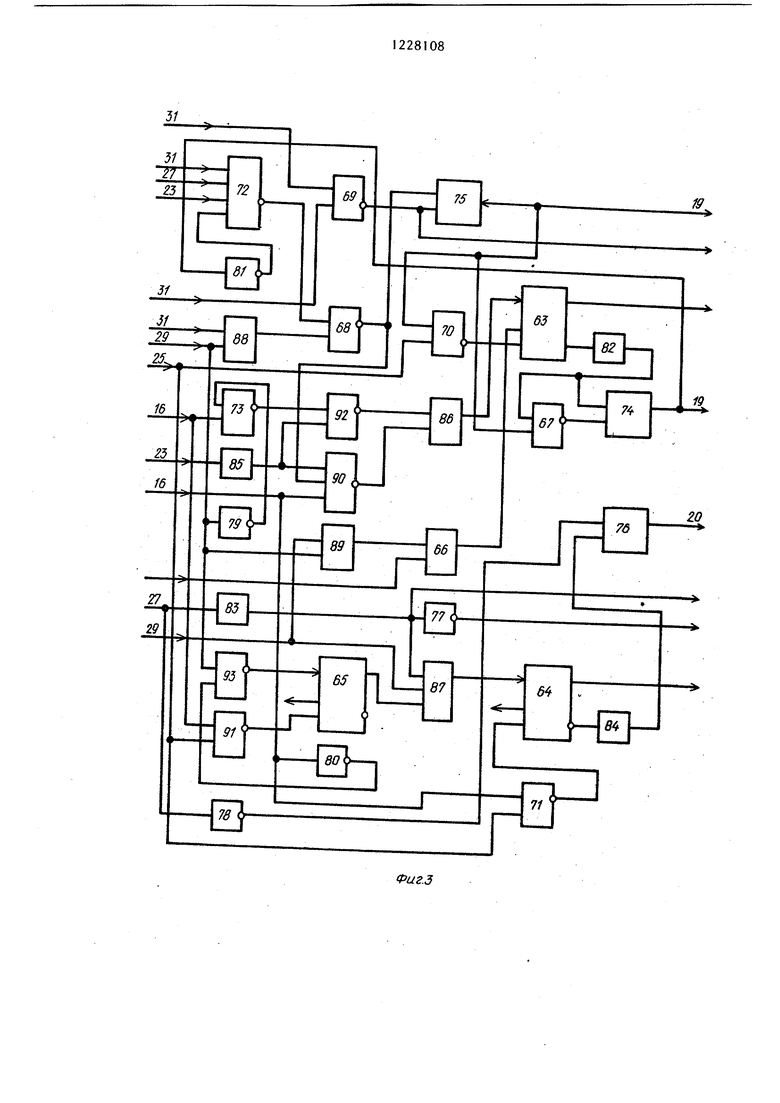

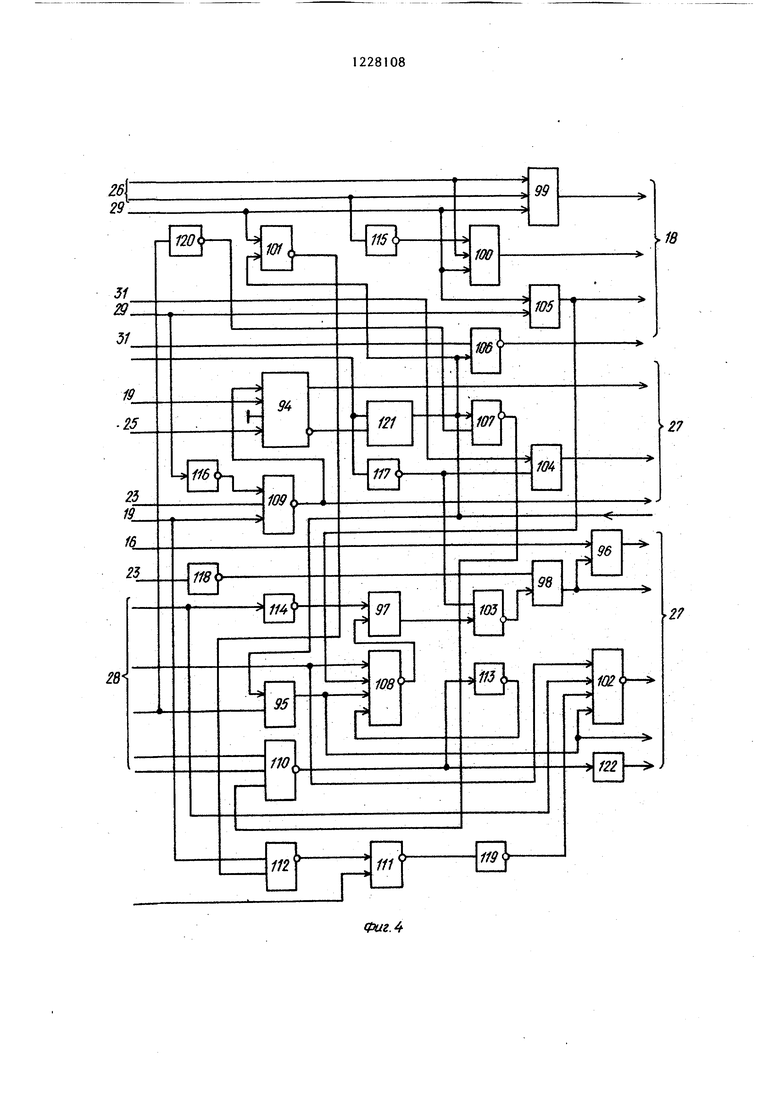

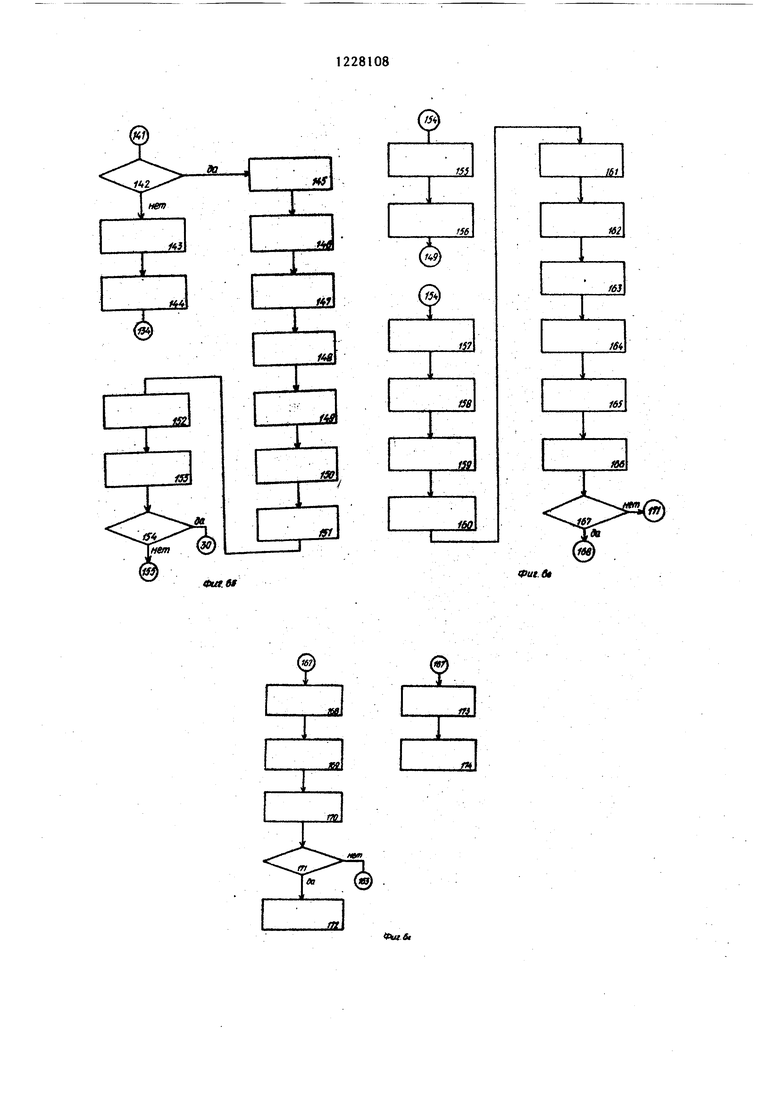

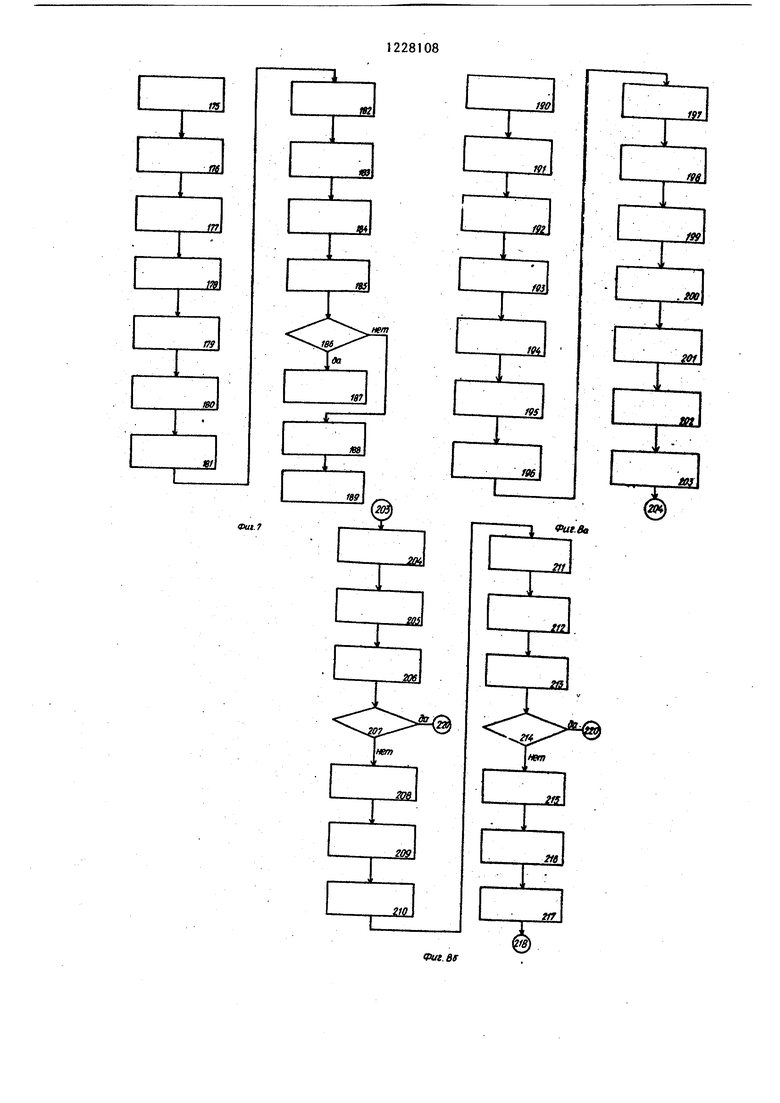

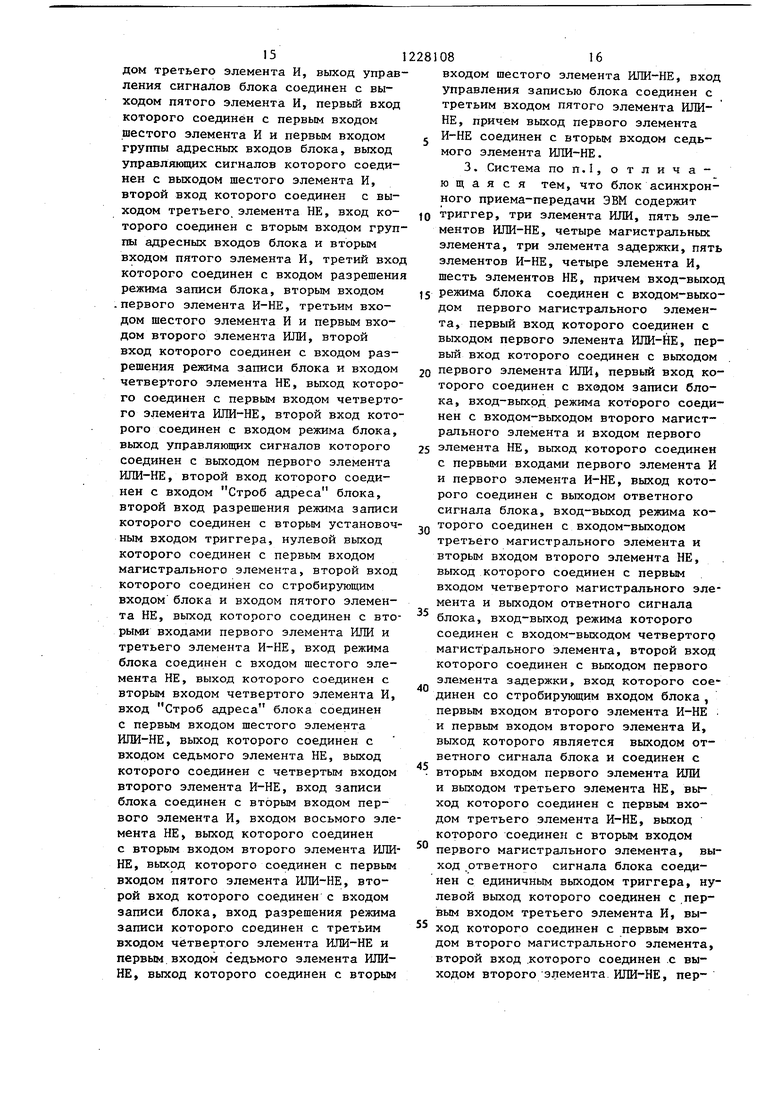

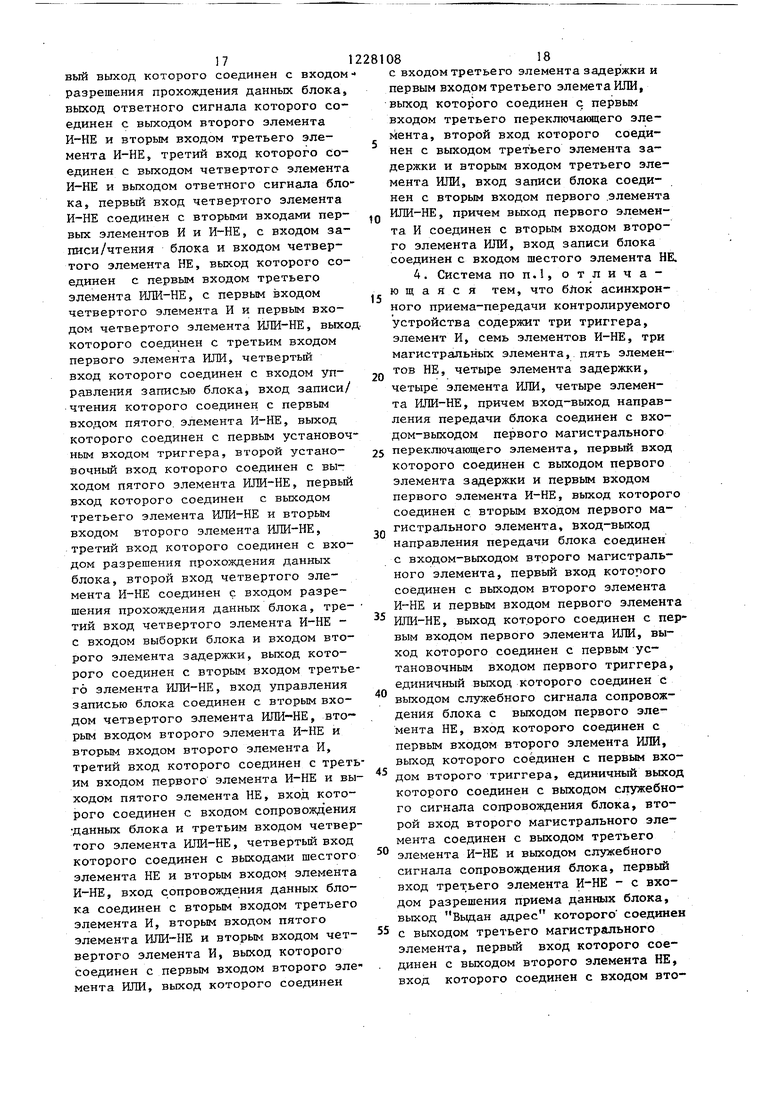

На фиг. 1 изображена структурная схема предлагаемой системы; на фиг 2. схема блока асинхронного приема-передачи ЭВМ; на фиг. 3 - схема блока асинхронного приема-передачи контролируемого устройства; на фиг. 4 - схема блока управления; на фиг. 5 - схема блока останова по адресу; на фиг. 6а - 6г - блок-схема алгоритма процедуры контроля блокнотной памяти контролируемого устройства; на фиг. 7 - блок-схема алгоритма процедуры контроля регистров внешних устройств контролируемого устройства; на фиг. 8а - 8в - блок-схема алгоритма процедуры контроля вьтолнения программы с замещением постоянного запоминающего устройства (ПЗУ).

Система содержит устройство 1 выработки тестовых воздействий и анализа реакции (в качестве которого может быть использована ЭВМ Электроника НЦОЗД), информационную шину 2 (шина тестовых сигналов), блоки 3 и 4 магистральных элементов, блок 5 прерывания, блок 6 регистров, регист 7 режимов, блок 8 останова по адресу блок 9 модификации адреса, селектор 10 адреса, дешифратор 11 команд, блок 12 асинхронного приема-передачи ЭВМ, блок 13 асинхронного приема- передачи контролируемого устройства, блок 14 управления, шины 15 данных, управления 16 и адреса 17 контролируемого устройства, выход 18 управляющих сигналов, вход-выход 19 направления передачи, выход 20 Выдан адрес, выход 21 номера контролируемого устройства, выход 22 режима вход-выход 23, вход 24 прерьшания, выход 25, адресную шину 26, выход 27 блока 14, выход 28 дешифратора 11, выход 29 селектора 10, выходы 30 и 31 блоков 14 и 12 соответственно.

Блок 12 асинхронного приема-передачи ЭВМ (фиг.2) содержит триггер 32, элементы ИЛИ 33-35, элементы ИЛИ-НЕ 36-40, магистральные элементы 41-44, элементы 45-47 задержки, элементы И-НЕ 48-52, элементы И 53-56, элементы НЕ 57-62.

Блок 13 асинхронного приема-пе - дачи контролируемого устройства (фиг.З) содержит триггеры 63-65, элемент И 66, элементы И-НЕ 67-73, магистральные элементы 74-76, элементы НЕ 77-81, элементы 82-85 задержки, элементы ИЛИ 86-89, элементы ШШ-НЕ 90-93.

Блок 14 управления (фиг.4) со- Q держит триггер 94, элементы И 95-100 элементы И-НЕ 101-103, элементы ШШ 104 и 105, элементы ИЛИ-НЕ 106-112, элементы НЕ 113-120, магистральньй элемент 121, элемент 122 задержки. 5 Блок 8 останова по адресу содер- . жит регистр 123, схему 124 сравнения, первьй элемент И 125, второй элемент И 126, элемент 127 задержки.

На фиг. ба-г, 7 и 8а-в позициями Q 128-221 обозначены команды, выполняемые ЭВМ в соответствии с алгоритмом.

Система работает следующим образом.

Контролируемое устройство (программируемый контроллер), являясь универсальным вычислительным блоком, специализируется на программном уровне, причем системные программы размещаются: в постоянном запоминающем устройстве (ПЗУ), что исключает операции ввода-вывода программ и упрощает эксплуатацию. Экономические соображения заставляют разработчика

5 избегать какой-либо аппаратной избыточности, а условия эксплуатации определяют максимально простые и надежные конструктивные решения.

Перечисленные особенности ставят перед разработчиком проблему контроля, а перед пользователями - проблему отладки рабочих программ для конкретной системы управления на базе микропроцессорного контроллера, поскольку сам контроллер не имеет для этого практически никаких средств.

Одним из возможных решений этой проблемы является применение программных кросс-систем на больших ЭВМ.

Однако такой путь имеет ряд недостатков . Прежде всего, не всякий пользователь имеет свободньй доступ к большим ЭВМ и в большинстве случаев его квалификации недостаточно для их эф5 фективного использования. Кроме того,, пользователя интересует конечный результат, т.е. отлаженная система, а не только системные программы.

0

0

5

Другой возможный подход заключа- ется в полном натурном моделировании системы, а ПЗУ программируемого контроллера моделируется с помощью универсальной микро-ЭВМ. Натурное моделирование системы обеспечивает полноту отладки.

Такая система должна обеспечивать возможность подключения контролируемого устройства к магистрали ЭВМ; переадресацию команд контроллера в отведенные подсистемные программы (т.е. замещающую ПЗУ) область запоминающего устройства (ЗУ) микро- ЭВМ, доступ к системным регистрам блокнотной памяти и внешней магистрали контроллера со стороны процессора микро-ЭВМ

В системе контролируемое устройст .во подключается к магистрали ЭВМ 1, как второй процессор с номером, поступающим по группе входов 21. Такое включение позволяет контролируемому устройству адресоваться к оперативному запоминающему устройству (ОЗУ) ЭВМ 1, как к памяти программ при отключенном собственном ПЗУ независимо от основного процессора ЭВМ 1. Отличие заключается в том, что при обращении со стороны контролируемого устройства в ОЗУ ЭВМ 1 блок переадресации системы обеспечивает увеличение на 1 седьмого разряда адреса, так что нулевой ячейке ПЗУ контролируемого устройства соответствует ячейка ОЗУ ЭВМ 1 с номером 000400. Модификация защищает нулевую страницу ОЗУ ЭВМ , поскольку математическое обеспечение ЭВМ 1 предполагает хранение в ней векторов системных прерьшаний и определяет верхнюю границу области памяти, отведенной под отлалдаваемые программы контролируемого объекта.

При выполнении процедуры контроля за выполнение команд контролируемого устройства в ЭВМ 1 формируется адрес регистра режима (166167) на шине 2 тестовых сигналов задается код, равный нулю, и передается в 11 и 15 разрядах, задается режим Запись, Сигнал, Вьщан адрес. В селекторе 10 адреса формируется признак обращения к регистру 7 режимов, по которому в дешифратор 1 команд устанавливает первый разряд регистра 7 режима в 1 который устанавливается при нулевых сигналах в 11 и 15 разрядах информации. На втором выходе регистра 7 режима появляется сигнал Пуск, запускающий микропроцессор контролируемого устройства. Одновременно в блоке управления срабатьшают элемент ИЛИ-НЕ

ПО и элемент 122 задержки, формируя сигнал, по которому в блоке асинхронного приема-передачи ЭВМ на первый вход второго магистрального переключающего элемента 42 (фиг.2) через элемент И 55 поступает сигнал уровня логического нуля, формируя ответный сигнал Приняты данные.

В контролируемом устройстве по сигналу Пуск формируется нулевой

адрес ячейки ПЗУ и сигнал Выборка ПЗУ. В этом режиме информация из ПЗУ в контролируемом устройстве не считывается, а вместо ПЗУ информация -считьшается из памяти ЭВМ 1.

Адрес по группе входов 17 поступает в блок 9, где выполняется прибавление 1 в 7-й разряд адреса, а модифицированный адрес заносится на регистр, одновременно в блоке 5 прерывания формируется сигнал Прерьгоа- ние, по которому ЭВМ 1 заканчивает выполнение текущей команды и формирует сигнал Разрешение прерывания.

По этому сигналу блока 5 прерывания в блоке 14 управления (фиг.4) по цепи элементов НЕ 117 и ИЛИ 104 сигнал, разрешающий прохождение адреса через второй блок 8 магистраль;-, ных элементов и формирующий через элемент 45 задержки блока 12 синх-

ронного приема-передачи ЭВМ (фиг.2) разрешение на магистральный элемент 44, на первый вход которого поступает уровень логического нуля, выраба- тьшая сигнал Выдан адрес, который определяет наличие достоверного адреса на магистрали 26. Одновременно в блоке 14 управления на магистральном элементе 121 формируется режим Чтение (уровень логической 1).

В ОЗУ ЭВМ 1 по модифицированному адресу, поступающему по группе входов 26 считывается информация, сопровождаемая сигналом Выданы данные по шине 23, по которому в блоке 13 асинхронного обмена контролируемого устройства возбуждаются элемент 85 задержки, элементы ИЛИ-НЕ 92 и ИЛИ 86, устанавливающие триггер 63 в 1, формируя сигнал разрешения

на прохождение информации в первый блок 3 магистральных элементов, а по цепи 82 задержки, элемент И-НЕ 67 и магистральный элемент 74 - сигнал

Выданы данные для контролируемого устройства. Контролируемое устройство после приема команды вырабатывает сигнал Приняты данные, по которому сбрасывается сигнал Выданы данные по цепочке И-НЕ 67 и магистральный элемент 74, одновременно в блоке асинхронного приема-передачи ЭВМ формируется по цепи элемент 46 задержки элементы НЕ 60, ИЛИ-НЕ 38 и ИЛИ-НЕ 40, устанавливая триггер 32 в 1. Благодаря чему по цепи И 55 и ШШ-НЕ 37, магистральный элемент 42 выраба- тьгоается сигнал Приняты данные ЭВМ сбрасывает сигнал Вьщаны данные и формирует сигнал Принят адрес 31, по которому сбрасьшается сигнал Выдан адрес и акт обмена по магистрали заканчивается.

При приеме команды в контролируемом устройстве формируется сигнал Команда вьщана по которому в бло- ке 6 на регистр, заносится команда. Регистр команд доступен по чтению. При обращении к нему ЭВМ-1 формирует адрес 166125, поступающий по группе входов-выходов 26, уровень логичекой 1 по шине 25, определяющий режим Чтение и сигнал по шине 23 Вы дан адрес.

В селекторе 10 адреса формируется признак обращения к регистрам, по которому в дешифраторе команд при наличии перечисленных сигналов, вы- рабатьгоается сигнал разрешения на прохождение информации, в блоке 14 управления на элементе И-НЕ 102 формируется разрешение на прохождение информации через первый блок 3 ма- гистральных элементов, в блоке асинхронного приема-передачи ЭВМ на элементах ИЛИ-НЕ 36 и магистральном элементе 41, формируется сигнал Выданы данные, по которому информация при- нимается в ЭВМ 1. После приема информации ЭВМ 1 формирует сигнал Приняты данные, вырабатьгеающий по цепочке И-53, ИЛИ 34 и ИЛИ 35, элемент 47 задержки и магистральный элемент 43 сиг нал Принят адрес и у станав лив акаций уровень логической 1 на шине 23. Затем ЭВМ сравнивает.принятую информацию с эталонной, .осуществляя таким образом контроль за правильным прие- мом команд.

В процессе вьтолнения программы контролируемое устройство использует

свою память с произвольным доступом в режиме блокнотной памяти. В блокнотной памяти хранятся промежуточные результаты, константы и установки, заносимые с системного пульта, системные данные при обращении к подпрограммам. При откладке программы доступ к системным константам и промежуточным результатам чрезвычайно важен.

При выполнении процедуры контроля блокнотной памяти контролируемого устройства в ЭВМ формируется адрес, старшие 8 разрядов которого равны 176 ...д а младшие определяют номер ячейки блокнотной памяти, на линии 62 задается режим запись (уровень логического нуля) по соответствующей линии шины 25 вырабатывается сигнал Вьадан адрес, а по линии шины 23 - сигнал Вьзданы данные.

В селекторе 10 адреса формируется признак обращения к блокнотной памяти, по которому в блоке Т4 управления (фиг.4) на элементах НЕ П5, И 100, ШШ 105 и ИЛИ-НЕ 106 формируются уп- равляклцие сигналы для определения режима записи в блокнотную память.

Одновременно в блоке 12 асинхронного приёма-передачи контролируемого устройства через элемент ИЛИ 87 устанавливается в 1 триггер 64, формируя сигнал, разрешающий прохождение 8-ми разрядов адреса через второй блок 8 магистральных элементов, а через элемент 84 задержки и магистральный элемент 7 6 - сигнал Вьщан адрес Разрешение на прохождение этого сигнала формируется на элементах ИЛИ-НЕ 108, И 97, И-НЕ 103 и И 98 блока 14 управления (фиг.4).

В контролируемом устройстве после приема адреса вырабатывается сигнал Принят адрес, по которому в блоке асинхронного приема-передачи контролируемого устройства устанавливается в О триггер 64, блокируя передачу адреса в контролируемое устройство и сбрасывая сигнал Вьщан адрес (устанавливается уровень логической 1).

Одновременно по сигналу Принят адрес возбуждаются элементы ИЛИ-НЕ 90 и ШШ 86, устанавливая триггер 63 в 1, Формирующий сигнал, разрешающий прохождение через первый блок 3 магистральных элементов.

7

Через 200 не на элементе 82 задержки, элементе И-НЕ 67 и магистральном элементе 74 формируется сигнал Вьщаны данные.

Контролируемое устройство после приема данных вырабатьшает сигнал Приняты данные, по которому в 0ло- ке асинхронного приема-передачи ЭВМ возбуждается элемент ИЛИ-НЕ 37, разрешая формирование сигнала Приняты данные, а по цепи ИЛИ-НЕ 40 устанавливается в 1 триггер 32, формируя по цепи элемент И 55, магистральный элемент 42 сигнал, по которому в ЭВМ заканчивается цикл обме- на.

При выполнении режима Чтение из блокнотной памяти, на линии шины 25 задается режим чтение (уровень логической единицы) , а по линии шины 23 вырабатьшается сигнал Вьщан адрес . Передача адреса в контролируемом устройстве вьтолняется также, как в режиме Запись, причем по линии 18 передается уровень логическо- го нуля, определяющий режим чтения.

В контролируемом устройстве после приема адреса формируется сигнал Принят адрес, формируется информация, считанная из блокнотной памяти, и сигнал Вьщаны данные, сопровожда кяций информацию. В блоке 12 асинхронного приема-передачи ЭВМ (фИг.2) возбуждаются элементы ИЛИ-НЕ 39, ИЛИ 33 и ИЛИ-НЕ 36, формируя сигнал Выданы данные. Одновременно в бло- ке 14 управления (фиг.4) по цепи элементов И-НЕ 101, ИЛИ-НЕ 112, ИЛИ-НЕ 111, НЕ 119, И-НЕ 102 формируется разрешение на прохождение информации через первый блок 3 магистральных элементов.

После приема данных ЭВМ формирует сигнал Приняты данные, по которому в блоках 12 и 13 возбуждаются элементы И-НЕ 48, ИЛИ 88 и И-НЕ 68 и ма- гистральный элемент 75, формируя сигнал приняты данные, сбрасывающий сигнал Выданы данные ,

Кроме обращения к ячейкам блокнотной памяти система позволяет осуществить доступ к внешней магистрали контролируемого устройства, т.е. к регистрам отлаживаемой системы, а через них к датчикам и испольнитель ным механизмам.

Организация обмена такая же, как и при обращении К блокнотной памяти. Признаком обращения к внешним регист

1

0 5

0

0

088

рам является наличие кода 176..., в 3-х старших разрядах адреса и 1 в 7-м разряде адреса, при этом возбуждается элемент И 99 в блоке 14 управления (фиг.4) и формируется признак обращения к внешним регистрам.

Для управления вычислительным процессом контролируемого устройства в систему введены регистры управления, адресуемые на магистрали независимо от системных регистров контролируемого объекта. К ним относятся: регистр режима работы контролируемого устройства; регистр останова по адресу; регистр команд; регистр промежуточного хранения данных и адреса.

Регистр режима двухразрядный. При обращении к нему информация передается в 11 и 15-м разрядах машинного слова. Функциональное значение разрядов следукяцее. При записи О в оба разряда система производит пуск контролируемого устройства в автоматическом режиме выполнения программы. Процедура пуска была описана вьш1е.

При записи комбинации 01 происходит пуск контролируемого устройства в шаговом режиме, т.е. команда за командой с остановом после выполнения каждой. Процедура записи информации в регистр режима аналогична вьш1е описанной.

При записи комбинации 11 происходит останов контролируемого устройства, если он выполняет программу в автоматическом режиме. Запись по адресу выполняется аналогично вышеописанному. При передаче адреса 66I63g в селекторе адреса срабатывает схема сравнения и два элемента И, формируя признак обращения к регистру режима.

При занесении в блок останова по адресу адреса останова каждый -раз при совпадении текущего адреса команды контролируемого устройства с заданным происходит его останов. Запись информации в блок останова выполняется аналогично записи в регистр режима. Адрес регистра останова по адресу задается первый 166127в.

При выполнении программы контролируемым устройством текущий адрес поступает на блок 15, в момент совпадения текущего адреса с заданным числом формируется сигнал по шине Останов. При отсутствии совпадения останова по адресу ке происходит, а вырабатывается одиночный импульс на

выходе для синхронизации осциллографа.

Регистр промежуточного хранения данных и адреса (блок 6) доступен по чтению. Он дублирует соответствую щие регистры контролируемого устройс ва и позволяет ЭВМ контролгфовать содержимое этих регистров в процессе выполнения программы, например в шаговом режиме. Если при выполнении программы осуществляется запись или считывание в блокнотную память или внешние регистры, то формируется сигнал Выданы данные из контролируе- мого устройства.

При обращении к регистру промежуточного хранения ЭВМ 1 формирует адрес, равный 166123g и сигналы Выдан адрес и Чтение.

Одновременно в блоке 12 асинхронного приема-передачи ЭВМ (фиг.2) на элементах ИЛИ 33 и ШШ-НЕ .36 и магистральном элементе 41 формируется сигнал Выданы данные, по которому информация принимается в ЭВМ 1. После приема информации ЭВМ 1 вырабатывает сигнал Приняты данные, по которому в блоке асинхронного приема- передачи ЭВМ по цепи элементов И 53, ИЛИ 34 и ИЛИ 35 элемента 47 задержки и магистрального элемента 43 формируется сигнал Принят адрес, по которому в ЭЗМ 1 сбрасьшается сигнал Выдан адрес, заканчивая обмен.

При выполнении процедуры контроля содержимого ПЗУ в ЭВМ 1 формируется адрес ячейки ПЗУ контролируемого устройства, причем код трех старших разрядов адреса является признаком обращения к ПЗУ и равен ПО.... Адрес сопровождается сигналом квитирования и задается режим Чтение.

В селекторе адреса по сигналу Вьщан адрес формируется сигнал, по которому в блоке 14 управления (Лиг.4) формируется элементом ИЛИ 105 сигнал,, определяющий режим контроля для контролируемого устройства. Одновременно по цепи ШШ-НЕ 108, И 97 и И-НЕ 103, И 98 и элемент 83 задержки ИЛИ 87 (фиг.З) устанавливается триггер 64, формируя сигнал, разрешающий трансляцию адреса ячейки ПЗУ в контролируемое устройство, а через элемент 84 задержки в магистральном элементе 76 формируется сигнал, сопровождающий адрес в контролируемое устройство.

Контролируемое устройство после приема адреса передает сигнал, по которому в блоке 13 асинхронного прие« ма-передачи контролируемого объекта

(фиг.З) по цепи элементы ИЛИ-НЕ 90 и ИЛИ 86 устанавливается в 1 триггер 63, формируя сигнал, разрешающий прохождение информации из контролируемого устройства в ЭВМ, а на шину 15

0 данных Информацию, сопровождаемую сиг налом Вьщаны данные.

По этому сигналу в блоке 12 асинхронного приема-передачи ЭВМ (фиг.2) возбзпкдаются элементы И 54, НЕ 59

j и И-НЕ 50, формируя управляющий сигнал на магистральный элемент 41. Одновременно по цепи ИЛИ-НЕ 39, ИЛИ 33 и ИЖ-НЕ 36, магистральный элемент 41 формирует 1игнал, по которому из ЭВМ

Q после приема информации вырабатывается сигнал приняты данные, В данном случае выполняется фиктивный обмен данными, так как на регистре адреса ЭВМ установлен адрес внешнего уст5 ройства, а не ОЗУ.

Сигнал Приняты данные возбуждает в блоке 14 управления (фиг.4) элемент ИЛИ-НЕ 109, формируя импульс, устанавливающий в 1 триггер 94, задавая режим Запись на выходе магистрального элемента 121, а через блок 5 прерывания формирует сигнал Прерьшание.

Получив из ЭВМ 1 сигнал Приняты данные блок асинхронного приема-пе редачи ЭВМ (фиг.2) формирует по цепи И 53, ИЛИ 34, элемент 47 задержки, элемент ИЛИ 35 и магистральный элемент 43 сигнал Принят адрес, по которому в блоке 5 прерьшания устанав ливается в 1 триггер при наличии сигнала, разрешакяцего прерьшание. В блоке 9 формируется адрес ячейки ОЗУ ЭВМ 1 следующим образом. К адресу, поступающему из контролируемого уст ройства, добавляется 1. Переадресация необходима, так как в первой ячейке памяти ЭВМ хранится информация, обеспечивающая работу ЭВМ 1 с контролируемым объектом. ЭВМ по сигналу

0 Принят адрес сбрасьгоает сигналы Выдан адрес и Вьщаны данные, заканчивая акт обмена по магистрали. После завершения акта обмена по магистрали в блоке асинхронного прие5 ма-передачи ЭВМ формируется по цепи НЕ 58, элемент задержки 45 и магистральный элемент 44, сигнал Вьщан адрес, по цепи И-НЕ 49 и И-НЕ 50

0

формируется сигнал, разрешающий рабо ту магистрального элемента 41, а по цепи И 54, ИЛИ 33 и ИЛИ-НЕ 36 магистральный элемент 41 формирует сигнал Вьщаны данные. ЭВМ записывает информацию в ячейку памяти, по адресу, передаваемому по магистрали 17, и вырабатывает сигнал 29, по которому в блоке 13 асинхронного приема-передачи контролируемого устройства (фиг.З) на элементе И-НЕ 69 формируется сигнал, разрешающий работу магистрального элемента 75, а по цепи И-НЕ 72 и И-НЕ 68, магистральный элемент 75 вырабатьшает сигнал Конец приема данных (КПД) в контролируемо устройство, в котором сигнал Конец вьщачи данных сбрасьшается, сбрасывая сигнал КПД. По заднему фронту сигнал КПД устанавливается в О триггер 94.

В блоке асинхронного приема-передачи ЭВМ по цепи элементов И 54, ИЛИ 33 и ИЛИ-НЕ 36 и магистрального элемента 41 сбрасьшается сигнал Выданы данные.

Затем в ЭВМ 1 сбрасываются сигналы Приняты данные и Принят адрес По сигналу Принят адрес устанавливается в О триггер в блоке 5 прерывания 5, а на выходе магистрального элемента 44 сбрасьгоается сигнал Выдан адрес (уровень логической 1).

ЭВМ 1 после приема информационного слова из контролируемого устройства сравнивает его с эталонным кодом и при наличии правильной информации переходит к считьшанию следующей ячейки ПЗУ контролируемого устройства, при отсутствии правильной информации фиксирует Отказ.

Формула изобретения1. Система для контроля микропроцессорных устройств, содержащая устройство выработки тестовых воздействий и анализа реакции, блок управления, первый блок магистральных элементов, первая группа выходов которого соединеиа с входной информационно шиной, устройство выработки тестовых воздействий и анализа реализации, блок асинхронного приема-передачи электронно-вычислительной машины (ЭВМ), вход-выход режима которого подключен к входу-выходу служебных сигналов сопровождения устройства

выработки тестовых воздействий и анализа реакциии, отличающаяся тем, что, с целью увеличения полноты контроля, она содержит второй блок магистральных элементов, блок модификации адреса, селектор адреса, дешифратор команд, блок асинхронного приема-передачи контролируемого устройства, блок останова по

адресу, блок регистров, причем адресная шина контролируемого устройства подключена к первой группе информационных входов-выходов второго блока магистральных элементов, группе информационных входов блока модификации адреса, первой группе информационных входов блока регистров, адресная шина устройства выработки тестовых воздействий и анализа реакции

подключена к второй группе информационных входов-выходов второго блока магистральных элементов, первой группе информационных входов селектора адреса, первой группе входов дешифратора команд и группе адресных входов блока управления, шина данных контролируемого устройства подключена к - первой группе информационных входов первого блока магистральных элементов и второй группе информационных входов блока регистров, шина управления контролируемого устройства подключена к входу смещения блока модификации адреса, разрешающим входам блока останова по адресу и блока регистров,

входам выборки блока асинхронной приема-передачи ЭВМ и контролируемого устройства и блока управления, первым входам запроса блока прерьша- ния, вход-вьтход служебных сигналов

сопровождения устройства выработки тестовых воздействий и анализа реакции подключен к входам-выходам режима блоков асинхронной приема-передачи ЭВМ и контролируемого устройства,

блока управления, второму входу запросов блока прерывания и управляющему входу селектора адреса, вторая группа информационных входов которого является входом задания номера

контролируемого устройства системы, а выход соединен с второй группой входов дешифратора команд, адресным входом блока асинхронного приема-передачи контролируемого устройства

и первым входом разрешения режима записи блока управления, пшна направления передачи контролируемого устройст ва подключена к входам сопровождения

данных асинхронного приема-передачи ЭВМ, входу-выходу направления передачи блока асинхронного приема-передачи контролируемого устройства, стробирующим входам блока останова по адресу, блока регистров и вторым входом разрешения записи йлока управления, выход управления записью которого соединен с управляющими входами первого и второго блоков . магистральных элементов и входами управления записью блоков асинхронного приема-передачи ЭВМ и контролируемого устройства, третьим входом запросов блока прерывания и вторым разрядным входом регистра режимов, выход служебного сигнала сопровождения блока асинхронного приема-передачи контролируемого устройства соединен со стробирукяцими входами первого и второго блоков магистральных элементов и входом разрешения прохождения данных блока асинхронного приема-передачи ЭВМ, выход блока модификации адреса - с третьей группой информационных входов второго блока магистральных элементов и входом текущего адреса блока останова по адресу, вход заданного адреса которого соединен с вторым выходом первого блока магистральных элементов, группа выходов дешифратора команд соединена с третьим разрядным входом регистра режимов, входами записи блока останова по адресу и блока регистров блока асинхронного приема-передачи ЭВМ и блока управления, выход Запись/чтение устройства вычисления тестовых воздействий и анализа реакции соединен с четвертым входом запросов блока прерьтания входами-выходами запись/ ;/чтение блока асинхронного приема-передачи ЭВМ, контролируемого устройства блока управления и третьей группой входов дешифратора команд, второй выход блока прерьшаний соединен со стробирующими входами блоков асинхронного приема-передачи ЭВМ и контролируемого устройства и блока управления, выход управляющих сигналов которого и выход регистра режима соединены с входной шиной управления контролируемого устройства, первый выход первого блока магистральных элементов соединен четвертым разрядным входом регистра режима, пятый разрядный вход которого соединен с выходом блока останова по адресу, выход ответного сигнала блока асинхронного приема-передачи ЭЙМ соединен с входом Строб адреса блока управления и входом разрешения приема данных блока асинхронного при- ема-передачи контролируемого устройства, выход Выдан адрес которого соединен с входом сопровождения адреса контролируемого устройства. 2. Система по п.1, о тл и ч а ю щ а я с я тем, что блок управле-- ния содержит шесть элементов И, три элемента И-НЕ, два элемента ШШ, семь элементов КПИ-НЕ, восемь элементов НЕ, магистральный элемент, элемент задержки и триггер, причем вход- выход записи/чтения блока соединен с входом-выходом магистрального элемента, с первыми входами первого элемента ИЛИ-НЕ, первого элемента H-HEj

второго элемента ИЛИ-НЕ и первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ- НЕ, выходом управления записью блока и первым входом второго элемента

И-НЕ, выход которого соединен с выходом управления записью блока, соединенным с выходом второго элемента И, первый вход которого соединен с входом выборки блока, выход управления записью которого соединен с выходом четвертого элемента ШШ-НЕ и первым установочным входом триггера, единичный выход которого соединен с выходом управления записью, соединенным также с выходом первого элемента задержки, вход которого соединен с выходом пятого элемента ШШ-НЕ и входом первого элемента НЕ, выход которого соединен с вторым входом третьего элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемен та И, выход которого соединен с вторым входом второго, элемента И.,и с выходом управления записью блока и выходом первого элемента ИЛИ, первый вход которого соединен с входом Строб-адреса блока, выход управляющих сигналов которого соединен с выходом второго элемента ИЛИ третьим входом третьего элемента ИЛИ-НЕ, четвертый вход которого соединен с входом записи блока и вторым, третьим входами второго элемента И-НЕ, сое- диненнь&1 входом второго элемента НЕ, выход которого соединен с вторым вхо

дом третьего элемента И, выход управления сигналов блока соединен с выходом пятого элемента И, первый вход которого соединён с первым входом шестого элемента И и первым входом группы адресных входов блока, выход управляющих сигналов которого соединен с выходом шестого элемента И, второй вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с вторым входом группы адресных входов блока и вторым входом пятого элемента И, третий вход которого соединен с входом разрешения режима записи блока, вторым входом .первого элемента И-НЕ, третьим входом шестого элемента И и первым входом второго элемента ИЛИ, второй вход которого соединен с входом разрешения режима записи блока и входом четвертого элемента НЕ, выход которого соединен с первым входом четвертого элемента ШШ-НЕ, второй вход которого соединен с входом режима блока, выход управляющих сигналов которого соединен с выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с входом Строб адреса блока, второй вход разрешения режима записи которого соединен с вторым установочным входом триггера, нулевой выход которого соединен с первым входом магистрального элемента, второй вход которого соединен со стробирующим входом блока и входом пятого элемента НЕ, выход которого соединен с вторыми входами первого элемента ИЛИ и третьего элемента И-НЕ, вход режима блока соединен с входом шестого элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, вход Строб адреса блока соединен с первым входом шестого элемента ШШ-НЕ, выход которого соединен с входом седьмого элемента НЕ, выход которого соединен с четвертым входом второго элемента И-НЕ, вход записи блока соединен с вторым входом первого элемента И, входом восьмого элемента НЕ, выход которого соединен с вторым входом второго элемента ИЛИ- НЕ, выход которого соединен с первым входом пятого элемента ИЛИ-НЕ, второй вход которого соединен с входом записи блока, вход разрешения режима записи которого соединен с третьим входом четвертого элемента ИЛИ-НЕ и первым.входом седьмого элемента ИЛИ- НЕ, выход которого соединен с вторым

5

0

5

0

5

0

5

0

5

входом шестого элемента ИЛИ-НЕ, вход управления записью блока соединен с третьим входом пятого элемента ИЛИ- НЕ, причем выход первого элемента И-НЕ соединен с вторым входом седьмого элемента ИЛИ-НЕ.

3. Система по п.1, отличающая с я тем, что блок асинхронного приема-передачи ЭВМ содержит триггер, три элемента ИЛИ, пять элементов ИЛИ-НЕ, четыре магистральных элемента, три элемента задержки, пять элементов И-НЕ, четыре элемента И, шесть элементов НЕ, причем вход-выход режима блока соединен с входом-выходом первого магистрального элемента, первый вход которого соединен с вьпсодом первого элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого элемента ИЛИ первый вход которого соединен с входом записи блока, вход-выход режима которого соединен с входом-выходом второго магистрального элемента и входом первого элемента НЕ, выход которого соединен с первыми входами первого элемента И и первого элемента И-НЕ, выход которого соединен с выходом ответного сигнала блока, вход-выход режима которого соединен с входом-выходом третьего магистрального элемента и вторым входом второго элемента НЕ, выход которого соединен с первым входом четвертого магистрального элемента и выходом ответного сигнала блока, вход-выход режима которого соединен с входом-выходом четвертого магистрального элемента, второй вход которого соединен с выходом первого элемента задержки, вход которого соединен со стробирующим входом блока , первым входом второго элемента И-НЕ . и первьм входом второго элемента И, выход которого является выходом ответного сигнала блока и соединен с вторым входом первого элемента ИЛИ и выходом третьего элемента НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с вторым входом первого магистрального элемента, выход ответного сигнала блока соединен с единичным выходом триггера, нулевой выход которого соединен с .первым входом третьего элемента И, выход которого соединен с первым входом второго магистрального элемента, второй вход .которого соединен .с выходом второго элемента ИЛИ-НЕ, первый выход которого соединен с входом разрешения прохождения данных блока, выход ответного сигнала которого соединен с выходом второго элемента И-НЕ и вторым входом третьего элемента И-НЕ третий вход которого соединен с выходом четвертого элемента И-НЕ и выходом ответного сигнала блока, первый вход четвертого элемента И-НЕ соединен с вторыми входами первых элементов И и И-НЕ, с входом за- 1шси/чтения блока и входом четвертого элемента НЕ, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, с первым входом четвертого элемента И и первым входом четвертого элемента ИЛИ-НЕ, выхо которого соединен с третьим входом первого элемента ИЛИ, четвертый вход которого соединен с входом управления записью блока, вход записи/ чтения которого соединен с первым входом пятого, элемента И-НЕ, выход которого соединен с первым установоч ным входом триггера, второй установочный вход которого соединен с выходом пятого элемента ИЛИ-НЕ, первый вход которого соединен с выходом третьего элемента ИЛИ-НЕ и вторым входом второго элемента ИЛИ-НЕ, третий вход которого соединен с входом разрешения прохождения данных блока, второй вход четвертого элемента И-НЕ соединен с входом разрешения прохождения данных блока, тре- тий вход четвертого элемента И-НЕ - с входом выборки блока и входом второго элемента задержки, выход которого соединен с вторым входом третьего элемента ИЛИ-НЕ, вход управления записью блока соединен с вторым входом четвертого элемента ИЛИ-НЕ, вторым входом второго элемента И-НЕ и вторым входом второго элемента И, третий вход которого соединен с третьим входом первого элемента И-НЕ и выходом пятого элемента НЕ, вход которого соединен с входом сопровождения данных блока и третьим входом четвертого элемента ИЛИ-НЕ, четвертый вход которого соединен с выходами шестого элемента НЕ и вторым входом элемента И-НЕ, вход сопровождения данных блока соединен с вторым входом третьего элемента И, вторым входом пятого элемента ИЛИ-НЕ и вторым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен

0

5

0

5

0

5

0

5

0

с входом третьего элемента задержки и первым входом третьего элемета ИЛИ, выход которого соединен с первым входом третьего переключакяцего элемента, второй вход которого соединен с выходом третьего элемента задержки и вторым входом третьего элемента ИЛИ, вход записи блока соединен с вторым входом первого .элемента ИЛИ-НЕ, причем выход первого элемента И соединен с вторым входом второго элемента ИЛИ, вход записи блока соединен с входом шестого элемента НЕ.

4. Система поп.1, отличающаяся тем, что блок асинхронного приема-передачи контролируемого устройства содержит три триггера, элемент И, семь элементов И-НЕ, три магистральных элемента, пять элементов НЕ, четыре элемента задержки, четыре элемента ИЛИ, четыре элемента ИЛИ-НЕ, причем вход-выход направления передачи блока соединен с входом-выходом первого магистрального переключающего элемента, первый вход которого соединен с выходом первого элемента задержки и первым входом первого элемента И-НЕ, выход которого соединен с вторым входом первого магистрального элемента, вход-выход направления передачи блока соединен с входом-выходом второго магистрального элемента, первый вход которого соединен с выходом второго элемента И-НЕ и первым входом первого элемента ИЛИ-НЕ, выход кот.орого соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым установочным входом первого триггера, единичный выход которого соединен с выходом служебного сигнала сопровождения блока с выходом первого элемента НЕ, вход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом второго триггера, единичный выход которого соединен с выходом служебного сигнала сопровождения блока, второй вход второго Магистрального элемента соединен с выходом третьего элемента И-НЕ и выходом служебного сигнала сопровождения блока, первый вход третьего элемента И-НЕ - с входом разрешения приема данных блока, выход Выдан адрес которого соединен с выходом третьего магистрального элемента, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с входом второго элемента задержки и входом управ- пения записью блока, вход записи/чтения которого соединен с первыми входами четвертого элемента И-НЕ, второго элемента ИЛИ-НЕ и пятого элемента И-НЕ, выход -которого соединен с вторым входом второго триггера, нулевой выход которого соединен с входом задержки третьего элемента задержки, выход которого соединен с вторым входом третьего магистрального элемента, стробирующий вход блока соединен с первым входом первого элемента И, выход которого соединен с вторым входом

to

И-НЕ, вход выборки блока - с первым входом седьмого элемента Н-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего триггера, выход которого соединен с вторым входом второго элемента ИЛИ, третий вход которого соединен с адресным входом блока и первым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, адресный вход блока - с вторыми входами третьего и четвертого элементов ИЛИ, с входой третьего элемента НЕ

первого триггера, второй выход которо- J5 и первым входом четвертого элемента

.го соединен с входом первого элемента задержки, вход режима блока соединен с входом четвертого элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ-НЕ и первым входом третьего элемента ИЛИ- НЕ, выход которого соединен с вторым входом первого элемента ИЛИ, вход разрешения приема данных блока соединен с первым входом шестого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с входом разрешения приема данных блока, вход управления записью которого соединен с вторьм входом шестого элемента И-НЕ, третий вход которого соединен с входом режима блока, вход разрешения приема данных которого соединен с вторым входом третьего элемента

ШШ-НЕ, выход которого соединен с вторым установочным входом третьего триггера, вход выборки блока - с третьим входом первого элемента

20 ИЛИ-НЕ, вторым входом пятого элемен та И-НЕ и входом четвертого элемента НЕ, выход которого соединен с вторым входом четвертого элемента ИЛИ-НЕ, вход пятого элемента НЕ со25 единен с входом-выходом направления передачи блока, а выход - с четвертым входом шестого элемента И-НЕ, второй вход первого элемента И-НЕ соединен с входом-выходом направле3Q ния передачи блока и вторым входом четвертого элемента И-НЕ, выход которого соединен с третьим установоч ным входом первого триггера,.выход седьмого элементаИ-НЕ соединенс вто рым входом третьего элемента ИЛИ-НЕ выход третьего элемента НЕ с вторьм входом седьмого элемента И-НЕ.

35

И-НЕ, вход выборки блока - с первым входом седьмого элемента Н-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего триггера, выход которого соединен с вторым входом второго элемента ИЛИ, третий вход которого соединен с адресным входом блока и первым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, адресный вход блока - с вторыми входами третьего и четвертого элементов ИЛИ, с входой третьего элемента НЕ

первым входом четвертого элемента

Ш-НЕ, выход которого соединен с вторым установочным входом третьего триггера, вход выборки блока - с третьим входом первого элемента

ИЛИ-НЕ, вторым входом пятого элемента И-НЕ и входом четвертого элемента НЕ, выход которого соединен с вторым входом четвертого элемента ИЛИ-НЕ, вход пятого элемента НЕ соединен с входом-выходом направления передачи блока, а выход - с четвертым входом шестого элемента И-НЕ, второй вход первого элемента И-НЕ соединен с входом-выходом направления передачи блока и вторым входом четвертого элемента И-НЕ, выход которого соединен с третьим установочным входом первого триггера,.выход седьмого элементаИ-НЕ соединенс вторым входом третьего элемента ИЛИ-НЕ, выход третьего элемента НЕ с вторьм входом седьмого элемента И-НЕ.

Фиг. 5

Фиг. 6а

(П2}

«ia.tt

Фыб

| название | год | авторы | номер документа |

|---|---|---|---|

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения вычисли-ТЕльНОй МАшиНы C Об'ЕКТАМи упРАВлЕНия | 1979 |

|

SU798784A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1171798A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения абонента с магистралью | 1989 |

|

SU1679494A1 |

| Устройство для ввода-вывода информации | 1991 |

|

SU1820375A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах автоматического контроля блоков и устройств дискретного действия при их производстве и эксплуатации. Целью изобретения является расширение функциональных возможностей системы и увеличение полноты контроля. Сущность изобретения заключается в том, что система для контроля электронных устройств, содержащая блок выработки тестовых воздействий и анализа реакции (цифровую вычислительную машину) , соединенную шиной тестовых сигналов с первым блоком магистральных элементов, по первому входу - Запрос прерывания - с блоком прерьшания, по первому выходу - Останов - с первым входом регистра режимов, содержит также два блока магистральных переключающих элементов, блок переадресации, селектор адреса, дешифратор команд, регистр режимов, блок асинхронного приема-передачи ЭВМ, блок асинхронного приема-передачи контролируемого объекта, блок управления, блок прерывания, блок останова по адресу, блок контроля с соответствующими связями. Введение указанных 6jiOKOB позволяет организовать необходимые режимы обмена между ЭВМ и контролируемым устройством. 3 з.п. ф-лы, 8 ил. с S (Л ю tvD 00 о 00

Фиг.вУ

220

221

Фиг. 8а

| Система для контроля электронных устройств | 1980 |

|

SU1005063A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система для контроля и диагностики цифровых узлов | 1980 |

|

SU911531A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1983-05-26—Подача