запуска генератора тактовых импульсо выход которого соединен со вторыми входами четвертого и шестого элементов И и третьим входом седьмого элемента И, выход которого соединен .с суммирующим входом реверсивного счетчика, сдвиговым входом регистра сдвига и первым входом четвертого элемента ИЛИ, выход которого соединен со сдвиговыми входами всех регистров сдвига группы, выходы элементов И первой группы соединены с первыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с адресными входами блока памяти, выходы которого соединены с информационными входами регистра кода отказа, группа выходов информационных разрядов которого соединена с вторыми входами соответствующих элементов ИЛИ группы и .первыми входами соответствующих элементов И второй. группы, выходы которых соединены с. входами дешифратора, выход разряда отказа регистра кода отказа соединен с вторыми входами элементов И второй группы, входом сброса генератора тактовых импульсов, инверсными входами пятого и шестого элементов И и вторым инверсным входом первого элемента ИЛИ, выход пятого элемента И соединен со вторым входом второго элемента ИЛИ, выход шестого элемента И соединен с управляющим входом блока памяти, вычитающим входом реверсивного счетчика, синхронизирующим входом регистра кода отказа и .вторым входом четвертого элемента ИЛИ, нулевой выход триггера ошибки соединен с управляющим входом генератора тактовых импульсов, первые входы каждого 1 -г элемента И третьей группы ( гт 51-1,где - число разрядов регистра сдвига) соединены с единичным выходом -i-ro разряда регистра сдвига, вторые входы каждого 1 -го элемента И третьей группы соединены с нулевым выходом (i+l)-ro разряда

регистра сдвига, единичный 6 -1о разряда регистра сдвига и вы- ходы элементов И третьей группы соединены с соответствующими управляющими входами коммутатора, группы информационных входов которого соединены с выходами соответствующих регистров сдвига группы, выходы коммутатора соединены с вторыми входами соответствующих элементов ИЛИ группы.

2. Устройство по П.1, о т л ичающееся тем, что блок формирования тестов содержит регистр адреса, регистр тестов, блок памяти, элемент ИЛИ, группу элементов И и группу элементов ИЛИ, причем первый вход элемента ИЛИ соединен с первым входом записи адреса блока, второй вход элемента ИЛИ, управляющий вход блока памяти и синхронизирующий вход регистра тестов соедине.н со вторым . входом записиадреса блока, первая группа информационных входов регистра адреса соединена с выходами элементов ИЛИ группы, первые и вторые входы которых соединены с первой

группой входов адреса, блока и выхо дами элементов И группы соответственно, вторая группа входов адреса блока соединена с первыми входами элементов И группы, вторые входы которых соединены с входом режима работы блока нулевые входы регистра адреса и регистра тестов соединены с

входом сброса блока, выходы регистра адреса соединены с адресным выходом блока и входами адреса блока- памяти, выходы которого соединены с информационными входами регистра тестов, информационная и адресная группы выходов которого соединены соответственно -с информационными выходами блока и второй группой информационных входов регистра адреса, первый и второй выходы конца тестирования регистра тестов являются соответственно первым и вторым .выходами конца тестирования блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

1.УСТРОЙСТВО ДЛЯ ТЕСТОВОГО ДИАГНОСТИРОВАНИЯ, содержащее наборное поле, блок формирования тестов, регистр сдвига, дешифратор, блок индикации и генератор тактовых импульсов, причем выход записи адреса и группа выходов адреса наборного поля соединены соответственно с первым входом записи адреса и первой группой Bxo-t, доз адреса блока формирования тестов, информационные выходы которых соединены с входами объектаконтроля, выходы дешифратора соединены с группой входом блока индика.-- ции, отличающееся тем, что, с целью повышения быстродойсвия, в него введены реверсивный счетчик, триггер режима тестирования, триггер ошибки, триггер режима работы, блок памяти, регистр кода отказа, группа регистров сдвига, коммутатор, формирователь одиночного импульса, элемент задержки,.четыре элемента ИЛИ, семь элементов И, , группа элементов ИЛИ и три группы элементов И, причем выходы реверсивного счетчика соединены с входами первого элемента ИЛИ, выход которого соединен с первым инверсным входом первого элемента И, выход которого соединен с первым- в Годом второго эле- мента ИЛИ, выход которого соединен с единичным входом триггера ошиб- , кИу единичный выход которого соединен с входом блока индикации, вторая группа входоВ адреса блока формирования гестов и .информационные входы регистров сдвига группы соединены с выходами объекта кон-хроля, первый выход конца тестирования блока формирования тестов через элемент задержки соединен с первым входом второго элемента И, выход которого соединен с первым входом треть-его элемента ИЛИ, выход которого соединен с единичным входом триггера режима работы, второй выход конца тестирования блока формирования тестов соединен с первым входом третьего элемента И и первыми входами элементов. И первой группы, вторые входы которых соединены с адресными выходами блока формирования тестов,, выход четвертого элемента И соединен с вторым входом записи блока формирования тестов, вход режима работы которого соединен с единичным выходом триггера режима тестирования, вторым входом третьего . элемента И и первым входом пятого ч О элемента И, второй вход которого соедивен с выходом формирователя одиночного импульса, вход которого соединен с первым входом шестого эле мента И и единичным выходом триггера режима работы, нулевой выход которого соединен с первыми входами четвертого и седьмого элементов И, выход режима тестирования наборного поля соединен с единичным входом триггера режима тестирования, нулевой выход которого соединен со вторыми входами второго и седьмого элементов И, выход нулевых установок наборного поля соединен с .:нулевыхвходами всех триггеров И регистров устройства и входом сброса блока формирования тестов, выход третьего элемента И соединен, со вторым входом третьего элемента ИЛИ, выход запуска наборного поля соединен с входом

1

Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования широкого класса объектов радиоэлектроники.

Известно устройство для тестового диагностирования, содержащее генератор тестов, блок дешифрации и блок управления.

Недостатками данного устройства является возможности обнаружения

только одиночных дефектов и отсутствие самоконтроля. Кроме того, с расширением класса объектов контрол для указанного устройства требуется введение существенной избыточности в устройстве для перестройки дешифраторов.

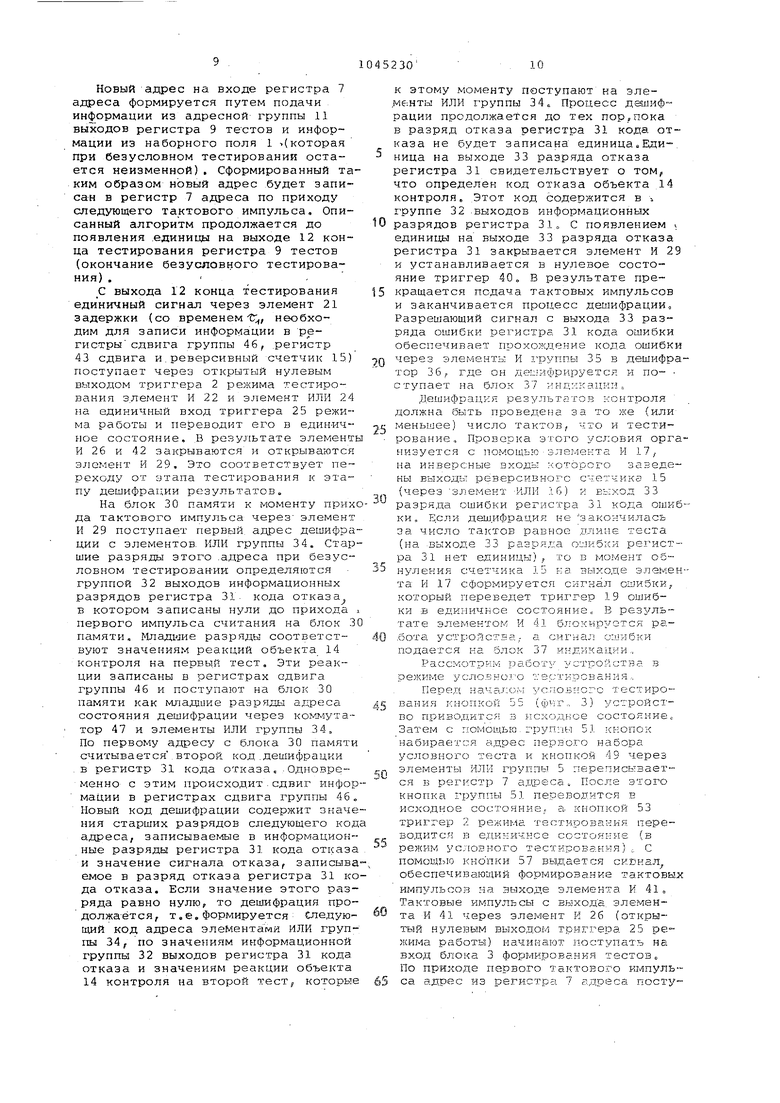

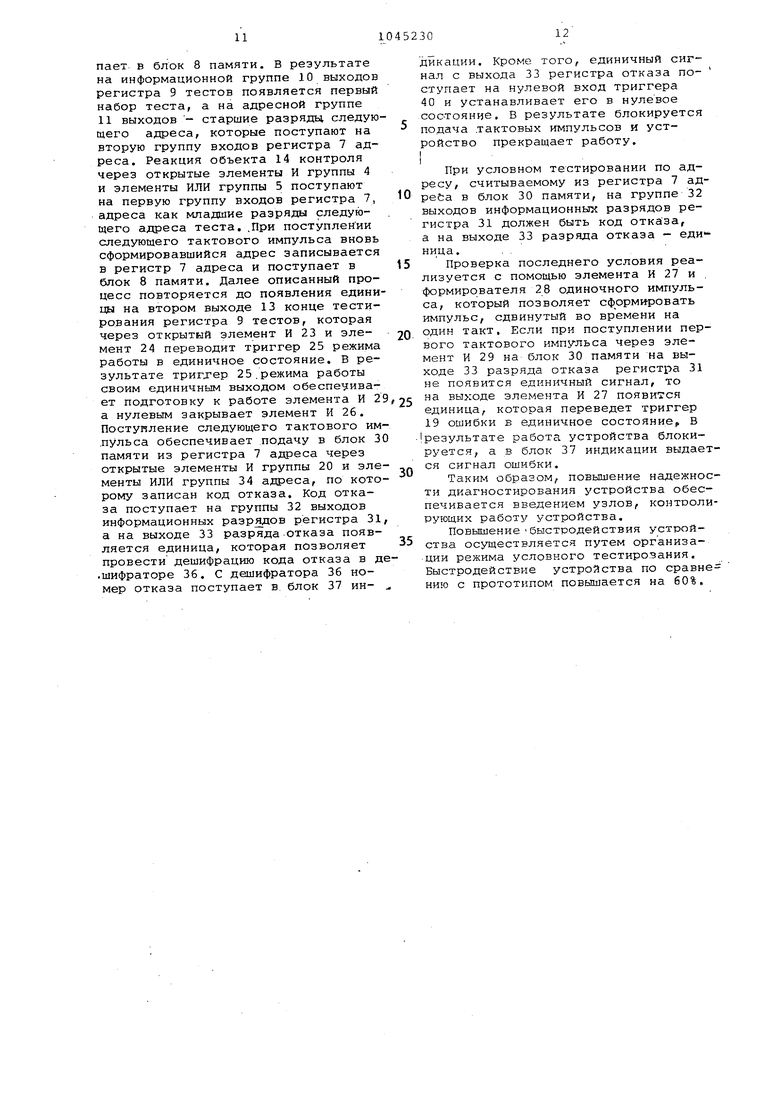

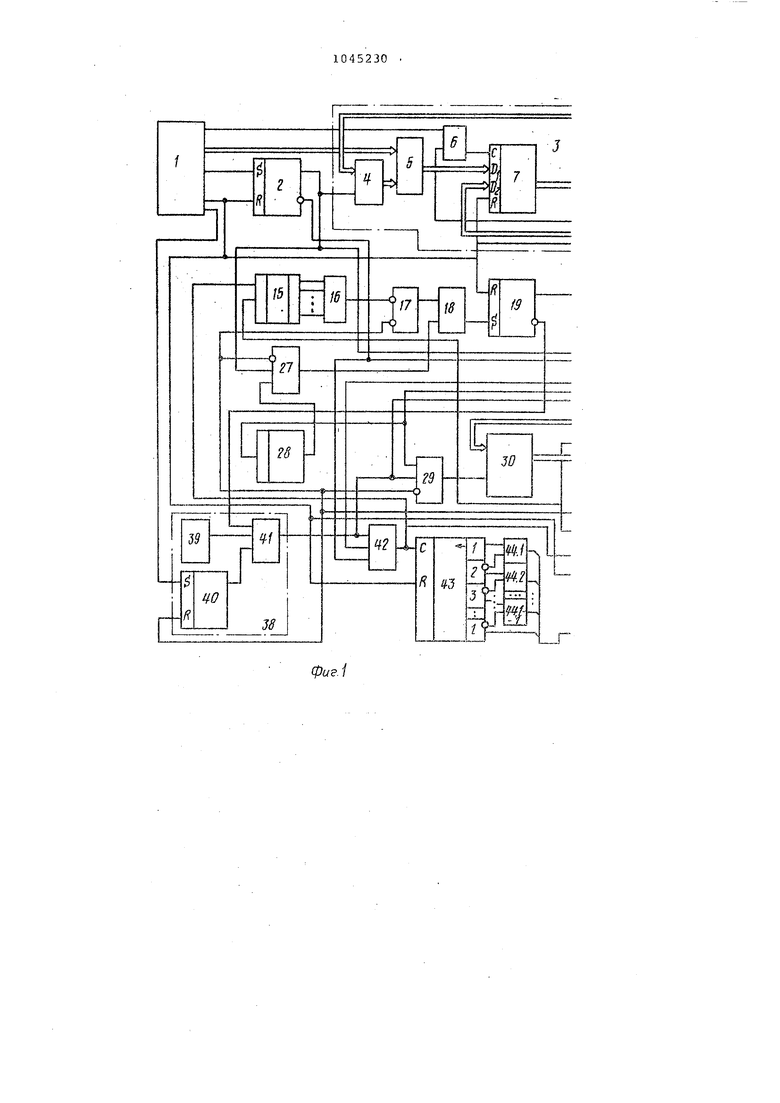

Наиболее близким по технической сущности является устройство для обнаружения неисправностей, содержащее дешифратор, блок индикации. формирователь, тактовых сигналов, регистр сдвига, объект контроля,генератор тестов, сумматор и блок вво да,первый выход которого соединен с первым входом генератора тестов, информационный выход которого соединен с информационным входом объек та контроля, выходы дешифратора сое динены со вторым входом блока индикации 2. Недостатками известного устройства являются возможность реализации только безусловных тестов,которые превосходят по длине и времени реализации условные тесты при одном и том же результате, воз можность обнаружения только одиноч ных отказов, что ограничивает глубину диагностики, ограниченност класса контролируемых объектов,что связано с необходимостью перестрой ки дешифраторов исправности и отказов, а также отсутствие контроля правильности работы устройства диагностйррвания, Цель нзобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для тестового диагностирования, содержащее наборное поле, блок -формирования тестов, регистр сдвига, дешифратор блок индикации и генератор тактовы импульсов, причем выход записи адреса и группа выходов адреса наборного поля соединены соответственно с первым входом записи адреса и пер вой группой входов адреса блока фор мирования тесгов, информационные вы ходы которого соединены с входами объекта контроля,- выхода дешифратора соединены с группой входов блока индикации, введены реверсивный счет чик, триггер режима тестирования, триггер ошибки, триггер режима работы, блок памяти, регистр кода отказа, группа регистров сдвига, коммутатор, формирователь одиночного импульса, элемент задержки, четыре элемента ИЛИ, семь элементов И,груп па элементов ИЛИ и три группы элементов И, причем выходы реверсивног счетчика соединены с входами первого элемента ИЛИ, выход которого, сое динен с первым инверсным входом пер вого элемента И, выход которого сое динен с первым входом второго элемента ИЛИ, выход которого соединен с единичным входом триггера ошибки, единичный выход которого соединен с входом блока индикации, вторая группа входов адреса блока формирования тестов и информационные входы регистров сдвига группы соединены с выходами объекта контроля, первый выход конца тестирования блока формирования тестов через эле мент задержки соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с единичным входом триггера режима работы, второй выход конца тестирования блока формирования тестов соединен с первым входом третьего элемента И и первыми входами элементов И первой группы, вторые входы которых .соединены с адресными выходами блока формирования тестов, выход четвертого элемента И соединен со вторым входом записи адреса блока формирования тестов,вход режима работы которого соединен с единичным выходом триггера режима тестирования, вторым входом третьего элемента И и первым входом пятого элемента И, второй вход которого соединен с выходом формирователя одиночного импульса, вход которого соединен с первым входом шестого элемента И и единичным выходом триггера режима работы,нулевой выход которого соединен с первыми входами четвертого и седьмого элементов И,выход режима тестирова- ния наборного поля соединен с единичным входом три1гера режима тестирования, нулевой выход которого соединен со вторыми входами второго и седьмого элемента И,, выход нулевых установок наборного поля соединен с нулевыми входами всех триггеров и регистров устройства и входом сброса блока формирования тестов, выход третьего элемента И соединен со вторым входом третьего элемента ИЛИ, выход запуска наборного поля соединен с входом запуска генератора тактовых импульсов, выход которого соединен со вторыми входа-ми четвертого и шестого элементов И и третьим входом седьмого элемента И, выход которого соединен с суммирующим входом реверсивного счетчика, сдвиговым входом регистра сдвига и первым входом четвертого элемента ИЛИ, выход которого соединен со %. сдвиговыми входами всех регистров сдвига группы, выходы элементов И первой группы соединены с первыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с адресными входами блока памяти, выходы i oToporo соединены с информационными входами регистра кода отказа, группа выходов информационных разрядов которого соединена со вторыми входами соответствующих элементов ИЛИ группы и первыми входами соответствующих элементов И второй группы, выходы которых соединены с входами дешифратора, выход разряда отказа регистра кода отказа соединен со вторыми входами элементов И второй группы, входом сброса генератора тактовых импульсов. инверсными входами пятого и шес,того элементов И и вторым инверсным входом первого элемента ИЛИ выход пятого элемента И соединен со вторым входом второго элемента .ИЛИ, выход шестого элемента И соединен с управляющим входом блока памяти, вычитающим входом реверсивного счетчика, синхронизирующим вхо дом регистра кода отказа и вторым входом четвертого элемента ИЛИ, нул вой выход триггера ошибки соединен управляющим входом генератора тактовых импульсов, первые входы каждого i-ro элемента И третьей группы (1€ iS t-lf где - число разрядов регистра сдвига) соединены с единич ным выходом i-ro разряда регистра сдвига, вторые входы каждого i-ro элемента И третьей группы соединены с нулевымвыходом (i+l)-ro разряда регистра сдвига, единичный выход 1-го разряда регистра сдвига и выхо ды элементов И третьей группы соединены с соответствующими управляющими входами коммутатора, группы информационных входов которого сое динены с выходами.соответствующих регистров сдвига группы, выходы коммутатора соединены со вторыми входами соответствующих .элементов ИЛИ группы. Кроме того, блок формирования те тов содержит регистр адреса,регистр тестов, блок памяти,элемент ИЛИ, группу элементов И и группу элементов ИЛИ, причем первый вход элемен та ИЛИ соединен с первым входом .за. писи адреса блока, второй вход эле мента ИЛИ, управляющий вход блока памяти и синхронизирующий вход регистра тестов соединены со.вторым входом записи адреса блока, первая группа информационных, входов регис адреса соединена с выходами элементов ИЛИ группы, первые и вторые входы которых соединены с первой группой входов адреса блока и выходами элементов И группы соответственно,, вторая группа входов адреса блока соединена с первыми вхо дами элементов И группы, вторые вхо ды которых соединены с входом режима работы блока, нулевые входы регистра адреса и регистра тестов соединены со входом сброса блока, выходы регистра адреса соединены с адресным выходом блока и входами адреса блока памяти, выходы которо соединены с информационными входам регистра тестов, информационная и адресная группы выходов которого с единены соответственно с информаци ными выходами блока и второй группой информационных входов регист; ра адреса, первый и второй выходы : конца тестирования регистра тестов I являются соответственно первым и вторым выходами конца тестирйвани блока. Управление процессом тестирования и дещифрации ведется в двух режимах; безусловного и условного тестирования. Появилась возможность производить эапись информации, поступающей от широкого класса объектов контроля, при безусловном тестировании, а также выдачу информации при дещифрации в нужной последовательности. Обеспечивается контроль правильности времени окончания дешифрации и блокировка работы устройства при ошибках. Проводится дешифра ция результатов как условного,так и безусловного тестирования. Возможно организовать условное тестирование и при дешифрации результатов условного тестирования подать адрес кода отказа на блок памяти. На фиг.1 и 2 приведена структурная схема устройства для тестового диагностирования; на фиг, 3 - функциональная схема наборного поля;на фиг. 4 - функциональная схема блока индикации. Устройство для тестового диагностирования {фиг. 1 и 2)- содержит наборное поле 1, триггер 2 режима тестирования, блок 3 формирования тестов, содержащий группу 4 элементов И, группу 5 элементов ИЛИ, элемент ИЛИ 6, регистр 7 адреса, блок 8 памяти, регистр 9 тестов, информационную группу 10 и адресную группу 11 выходов регистра 9 тестов, а также первый 12 и второй 13 выходы конца тестирования регистра 9 тестов, объект 14 контроля, реверсивный счетчик 15, первый элемент ИЛИ 16, первый элемент И 17, второй элемент ИЛИ 18, триггер 19 ошибки,первую группу 20 элементов И, элемент 21 задержки, второй 22 и третий 23 элементы И, третий элемент ИЛИ 24, триггер 25 ре.жима работы, четвертый 26 и пятый 27 элементы И, формирователь 28 одиночного импульса, шестовй элемент И 29, блок 30 па- . мяти, регистр 31 кода отказа, группу 32 выходов .информационных разрядов к выход 33 разряда отказа регистра 31 кода отказа, группу 34 элементов ИЛИ, вторую группу 35 элементов И, дешифратор 36, блок 37 индикации, генератор 38 тактовых импульсов,содержащий генератор 39, триггер 40 управления тактовыми импульсами и элемент И 41, седьмой элемент И 42, регистр 43 сдвига, третью группу 44 элементов И, четвертый элемент ИЛИ 45, группу 46 регистров сдвига и коммутатор 47, Наборное поле 1 (фиг, 3) содержит шину 48 питания ( 1 ) , группу кнопок с возвратом посредством второго нажатия, кнопкь, 49 для фор мирования сигнала записи адреса, записывающего адрес первого теста в регистр 7 адреса, выход 50 запис адреса наборного поля, группу 51 кнопок для набора адреса первого теста, группу 52 выходов адреса по ля, кнопку 53 для управления триггером 2 режима тестирования и соответствующий ей выход 54 режима тестирования поля, кнопку 55 общего сброса и соответствующий ей выход 56 нулевых установок блока, кнопку 57 управления триггером 40 и соответствующий ей выход 58 запуска поля. Блок 37 индикации (фиг. 4) обес печивает индикацию ошибочной работы устройства при подаче сигнала на вход 59 и индикацию номера состояния /отказа/ при подаче сигнало на группу 60 входов блока. Устройство содержит средства фор мирования тестовой последовательно ти, дешифрации результатов контрол управления и контроля.. Средства формирования тестовой последовательности включают группу 4 .элементов И, группу 5 элементов ИЛИ, элемент ИЛИ 6, регистр 7 адреса, блок 8 памяти, регистр 9 тестов; средства дешифрации ре- зультатовконтроля - блок 30 памят регистр 31 кода отказа, группу 34 элементов ИЛИ, вторую группу 35 эл ментов И, дешифратор 36, регистр 4 .сдвига, третью группу 44 элементов И, группу 46 регистров сдвига,коммутатор 47 и блок 37 индикациир средства управления - наборное поле 1 , триггер 2 режима тестировани элементы-И 20 , 22 ,23 , 26 , 29. и мент ИЛИ 24, элемент 21 задержки,f триггер 25 режима работы, элемент :ИЛИ.45 и генератор 38-тактовых им пульсов; средства контроля - реверсивный счетчик 15, Формировател 2 одиночного импульса, элементы ИЛ 16 и 18, элементы И 17 и 27 и триг гер 19 оши бк и. В блоках 8 и 30 памяти содержат ся соответственно тесты и коды отказов. Единичное состояние триггера 2 режима вотирования соответствует режиму условного тестирования, нулевое - безусловного тестирования, В регистры группы 46 записываются значения выходных сигналов объек та. 14 контроля в порядке их поступления. Количество регистров в блоке определяется числом выходов объекта 14 контроля, В регистре 43 сдвига при безусло ном тестировании производится запис Iчисла наборов теста s виде однопози ционного кода. С помощью третьей группы 44 элементов И и использования как прямых так и инверсных выходов регистра 43 сдвига формируется сигнал длины теста (числа наборов теста). Этот единичный сигнал в элементах третьей группы .4 формируется только в саMONr старшем разряде, в котором записана единица. Сформированная таким образом единица позволяет производить считывание информации с регистров сдвига группы 46, начиная с реакции объекта 14 контроля на первый набор теста. Например, в регистр 43 сдвига было записано три тактовых импульса. Значит в первых трех разрядах регистра на прямых выходах будут сформированы единицы, а на инвареных - нули. Следовательно, единица на выходе третьей группы 14 элементов И будет сформирована только в третьем разряде. Значит, при дешифрации результатов будут открыты только третьи разряды всех групп информационных входов коммутатора 47 В каждом такте дешифрации с регистров сдвига группы 46 будут поступать реакции объекта 14 контроля на наборы теста в порядке их записи (начиная с первого), Реверсивный счетчик 15 обеспечи- вает cy Ф1Иpoвaниe числа тактов при генерации тестов, и вычитания числа тактов при дешифрации результатов-. Рассмотрим работу устройства в р.ежиме безусловкого тестирования. Перед н-ачалом работы кнопкой 55 наборного ПОЛЯ (фиг, 3) устройство приводится Б исходное состояние,Затем с ПОМОЩЬЮ группы 51 кнопок набирается адрес первого теста и кнопка 49 через группу 5 элементов ИЛИ. переписывается в регистр 7 адреса. После этого управляющей кнопкой 57 выдается сигнал запуска,обеспечквающик формирование .тактовых .импульсов на вЕ11ко.це .элемента И-41. Тактовые импульсы с выхода элем.акта И 41. через открытый элемент И 26 поступаьэт на бло.с 3 формирования тестов, а через открытый элемент И 42 на часть средств дешифрации,обеспечивающих запись реакций объекта 14 контроля в регистр сдвига группы 46, При поступлении первого тактового итлпульса по адресу записанному в регистре 7 адреса из блока 8 памяти считывается информация в регистр 9 тестов. При этом в информационной группе 10 выходов регистра 9 тестов содержится первый набор теста, а в адресной группе 11 выходов регистра 9 тестов -. старшие разряды следующего адреса теста. Одновременно реакция с выходов объекта 14 контроля записывается в регистр сдчига группы 46, а тактовый импульс записывается.в регистр 43 сдвига и добавляет единицы в реверсивный счетчик 15,

Новый адрес на входе регистра 7 адреса формируется путем подачи информации из адресной группы 11 выходов регистра 9 тестов и информации из наборного поля 1 -.(которая при безусловном тестировании остается неизменной), Сформированный таким образом новый адрес будет записан в регистр 7 адреса по приходу следующего тактового импульса. Описанный алгоритм продолжается до появления .единицы на выходе 12 конца тестирования регистра 9 тестов (окончание безусловного тестирования) . выхода 12 конца тестирования единичный сигнал через элемент 21 задержки (со временем tr необходим для записи информации в регистры сдвига группы 46, .регистр 43 сдвига и.реверсивный счетчик 15) поступает через открытый нулевым выходом триггера 2 режима тестирования э.лемент И 22 и элемент ИЛИ 24 на единичный вход триггера 25 режима работы и переводит его в единичное состояние, В результате элементы И 26 и 42 закрываются и открываются элемент И 29, Это соответствует переходу от этапа тестирования к этапу дешифрации результатов,

На блок 30 памяти к моменту прихода тактового импульса через элемент И 29 поступает первый адрес дешифрации с элементов. ИЛИ группы 34, Старшие разряды этого .адреса при безусловном тестировании определяются группой 32 выходов информационных разрядов регистра 31 кода отказа в котором записаны нули до прихода . первого импульса считания на блок 30 памяти. Младшие разряды соответствуют значениям реакций объекта 14 контроля на первы.й тест. Эти реакции записаны в регистрах сдвига группы 46 и поступают на блок 30 памяти как младшие разряды адреса состояния дешифрации через коммутатор 47 и элементы ИЛИ х руппы 34, По первому адресу с блока 30 памяти считывается второй код .дешифрации .в регистр 31 кода отказа,-Одновременно с этим происходит.сдвиг информации в регистрах сдвига группы 46„ Новый код. дешифрации содержит значения старших разрядов следующего код адреса, записываег- ые в информационные разряды регистра 31 кода отказа и значение сигнала отказа, записыва емое в разряд отказа регистра 31 кода отказа. Если значение этого разряда равно нулю, то дешифрация продолжается, т.е.формируется Следующий код адреса элементами ИЛИ группы 34, по значениям информационной группы 32 выходов регистра 31 кода отказа и значениям реакции объекта 14 контроля на второй тест, которые

к этому моменту поступают на эле,ме;нты ИЛИ группы 34 Процесс д&тлфрации продолжается до тех пор.пока в разряд отказа регистра 31 кода отказа не будет записана единица Единица на выходе 33 разряда отказа регистра 31 свидетельствует о том, что определен код отказа объекта 14 контроля. Этот код содержится в i группе 32 выходов информационных разрядов регистра 31, С появлением единицы на выходе 33 разряда отказа регистра 31 закрывается элемент И 2 и устанавливается в нулевое состояние триггер 40, В результате прекращается подача тактовых импульсов и заканчивается процесс деи.ифрациИс Разрешающий с.игнал с выхода. 33 разряда ошибки регистра 31 кода ошибки обеспечивает прохождение кода ошибк через элементы И лруппы 35 в дешифртор 36, где он дешифрируется и поступает на блок 37 инц:-: сац -:н „

Дешифрация результатов контроля ддолжна быть проведена за то же (или меньшее) число тактов, что и тестирование. Проверка этого условия оргнизуется с 1омощью злемекта И 17, на инверсные входы ;(оторого заведены выходк реверсивного счетчика 15 (через злеме -:т -ИЛИ 16) и выход 33 разряда ошибки регистра 31 кода ошики. Если деш.ифрация не закончилась за число тактов равное .плиие теста (на выходе 33 разр.чда ошибки регистра 31 нет единицы), то в момент обнуления счетчика 15 ка выходе элемета И 17 сформируется сигнал ошибки, который переведет триггер 19 ошибки в е.дкничнсе состояние, В результате элементом И 41 блокирзстся ра.бота устройства а сигнал огиибки подается на блок 37 к дикации ,

Рассмотрим работу устройства в режргме усло-ено1ю тесткрсвання-,

Перед нача1;ол: усаовнсгс тестирования кнопкой 55 (фиг,, 3) устройс во приводится 3 исходное состояние,, Затем с помощью группы 5J. кнопок набирается а..црес первого набора условного теста и кнопкой 19 через элементы ИЛИ группы 5 переписьтваегся в регистр 7 арреса. После этого кнопка гру.ппы 51 переводится в исходное состояние, а кнопкой 53 триггер 2 режима тестирования переводится j;i едккичнсе состояние (в режим услоЕкого тестирования) с. С noMoiaJsio jfHonKH 57 выдается , обеспечивающий формирование тактовы импульсов на выходе элемента И 41, Тактовые мпульсы с выхода элемента И 41 через элемент И 26 (открытый нулевым выходом триггера 25 режима работы) начинают iiocTynaTb на вход блока 3 форми.рованкя тестов „ По приходе первого тактового т-лпульса адрес из регистра 7 а.:ареса поступает в блок 8 памяти. В результате на информационной группе 10 выходов регистра 9 тестов появляется первый набор теста, а на адресной группе 11 выходов - старшие разряды следую щего адреса, которые поступают на вторую группу входов регистра 7 адреса. Реакция объекта 14 контроля через открытые элементы И группы 4 и элементы ИЛИ группы 5 поступают на первую группу входов регистра 7, адреса как младшие разряды следующего адреса теста, .При поступлении следующего тактового импульса вновь сформировавшийся адрес записывается в регистр 7 адреса и поступает в блок 8 памяти. Далее описанный процесс повторяется до появления едини цы на втором выходе 13 конце тестирования регистра 9 тестов, которая через открытый элемент И 23 и элемент 24 переводит триггер 25 режима работы в единичное состояние. В результате тритлгер 25.режима работы своим единичным выходом обеспеуивает подготовку к работе элемента И 2 а нулевым закрывает элемент И 26. Поступление следующего тактового имлульса обеспечивает подачу в блок 30 памяти из регистра 7 адреса через открытые элементы И группы 20 и элементы ИЛИ группы 34 адреса, по которому записан код отказа. Код отказа поступает на группы 32 выходов информационных разрядов регистра 31 а на выходе 33 разряда отказа появляется единица, которая позволяет провести дешифрацию кода отказа в де .шифраторе 36. С дешифратора 36 номер отказа поступает в блок 37 индикации. Кроме того, единичный сигнал с выхода 33 регистра отказа поступает на нулевой вход триггера 40 и устанавливает его в нулевое состояние. В результате блокируется подача .тактовых импульсов и устройство прекращает работу. При условном тестировании по адресу, считываемому из регистра 7 адpefca в блок 30 памяти, на группе 32 выходов информационны разрядов регистра 31 должен быть код отказа, а на выходе 33 разряда отказа - еди ница. . . Проверка последнего условия реализуется с помощью элемента И 27 и . формирователя 28 одиночного импульса, который позволяет сформировать импульс, сдвинутый во времени на один такт. Если при поступлении первого тактового импульса через элемент И 29 на блок 30 памяти на выходе 33 разряда отказа регистра 31 не появится единичный сигнал, то на выходе элемента И 27 появится единица, которая переведет триггер 19 ошибки в единичное состояние В результате работа устройства блокируется, а в блок 37 индикации выдается сигнал ошибки. Таким образом, повышение надежности диагностирования устройства обеспечивается введением узлов, КОНТРОЛИРУЮЩИХ работу устройства. Повышение-быстродействия устройства осуществляется путем организации режима условного тестирования. Быстродействие устройства по сравнению с прототипом повышается на 60%,

м

-fu

гп

ж.

гп

/

m

..

55

ТР

.

(риг-2

50

.5/ -о

Я -о

-О

,J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-30—Публикация

1982-05-28—Подача