Изобретение относится к автоматике и контрольно-измерительной технике, предназначено для осуществления операции выборки-хранения аналоговой информации с повышенной точностью и может быть использовано как функциональный элемент микроэлектроники в системах сбора и распределения данных микропроцессорных устройств.

Известно устройство выборки-хранения аналоговой информации, содержащее два операционных усилителя, три переключателя и два конденсатора с идентичными параметрами, а также три резистора и два диода [1].

Это устройство характеризуется повышенной точностью хранения информации, достигаемой за счет выполнения двух идентичных цепей разряда накопительных конденсаторов, подключенных к входам операционного усилителя, однако оно не обеспечивает требуемой более высокой точности хранения аналоговой информации из-за реализуемых недостаточно больших постоянных времени разряда данных конденсаторов.

Из известных устройств наиболее близким по технической сущности является устройство для запоминания аналоговой информации, содержащее первый и второй конденсаторы, первый и второй переключатели, операционный усилитель, а также резистор и аттенюатор, состоящий из двух последовательно соединенных резисторов, при этом выход первого переключателя через резистор соединен с одним из выводов первого конденсатора и неинвертирующим входом операционного усилителя, выход которого, являющийся выходом устройства, соединен с одним из выводов второго конденсатора и свободным выводом одного из резисторов аттенюатора, точка соединения резисторов аттенюатора через второй переключатель соединена с инвертирующим входом операционного усилителя и вторым выводом второго конденсатора, второй вывод первого конденсатора и свободный вывод второго резистора аттенюатора соединены с общей шиной, управляющие входы первого и второго переключателей соединены с управляющим входом устройства, а информационный вход первого переключателя соединен с информационным входом устройства [2].

Данное устройство также отличается высокой точностью хранения аналоговой информации, однако получить более высокую точность хранения информации и в этом устройстве не удается из-за неодинаковых постоянных времени разряда накопительных конденсаторов, реализуемых даже при идентичных параметрах конденсаторов и переключателей.

Целью изобретения является повышение точности хранения информации за счет обеспечения одинаковых и достаточно больших постоянных времени разряда накопительных конденсаторов.

Цель достигается тем, что в устройство для запоминания аналоговой информации, содержащее первый и второй конденсаторы, первый и второй переключатели, операционный усилитель, а также резистор и аттенюатор, при этом выход первого переключателя через резистор соединен с одним из выводов первого конденсатора и неинвертирующим входом операционного усилителя, выход которого, являющийся выходом устройства, соединен с одним из выводов второго конденсатора и входом аттенюатора, первый выход аттенюатора через второй переключатель соединен с инвертирующим входом операционного усилителя и вторым выводом второго конденсатора, второй вывод первого конденсатора соединен с общей шиной, а управляющие входы первого и второго переключателей соединены с управляющим входом устройства, введен третий переключатель, информационный и управляющий входы которого соединены соответственно с информационным и управляющим входами устройства, а выход третьего переключателя соединен с информационным входом первого переключателя и вторым выходом аттенюатора.

Устройство отличается и тем, что в нем аттенюатор выполнен в виде трех резисторов и повторителя напряжения, при этом первый и второй резисторы соединены последовательно и включены между входом и общей шиной аттенюатора, точка соединения первого и второго резисторов подключена к первому выходу аттенюатора и через повторитель напряжения соединена с одним из выводов третьего резистора, второй вывод которого соединен с вторым выходом аттенюатора.

Устройство отличается также и тем, что в нем аттенюатор выполнен в виде трех резисторов, при этом первый и второй резисторы соединены последовательно и включены между входом и общей шиной аттенюатора, точка соединения первого и второго резисторов подключена к первому выходу аттенюатора и через третий резистор соединена с вторым выходом аттенюатора.

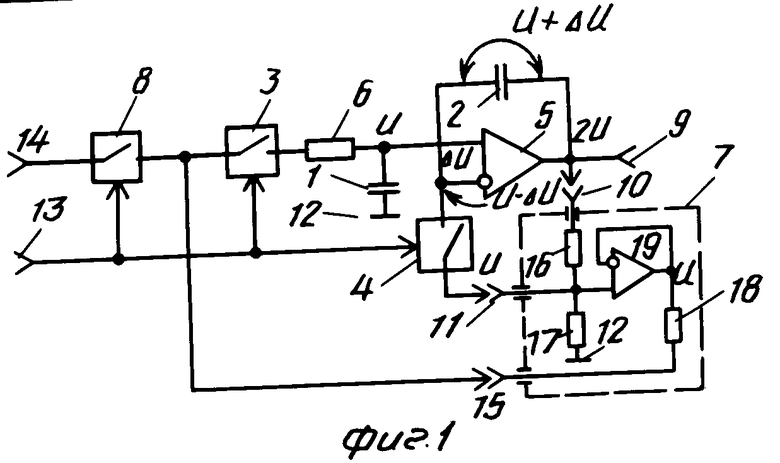

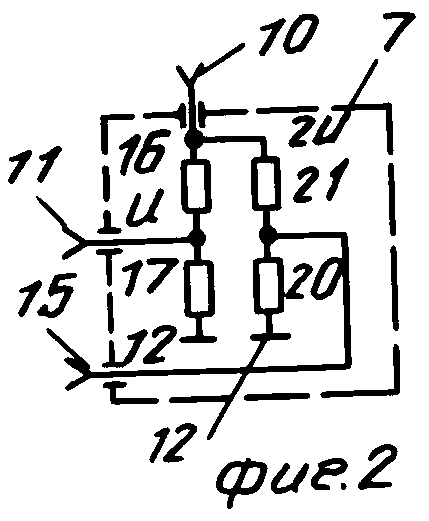

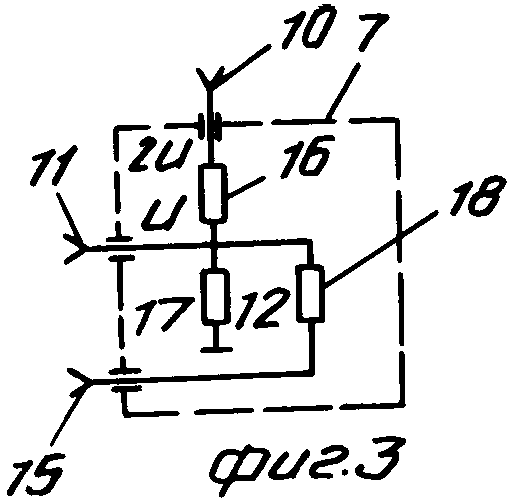

На фиг. 1 представлена структурно-принципиальная схема устройства для запоминания аналоговой информации; на фиг.2, 3 - варианты реализации аттенюатора.

Устройство для запоминания аналоговой информации (фиг. 1) содержит первый и второй накопительные конденсаторы 1 и 2, первый и второй ключи 3 и 4, операционный усилитель 5, нагрузочный резистор 6, аттенюатор 7, а также третий ключ 8.

При этом выход первого ключа 3 через резистор 6 соединен с одним из выводов первого конденсатора 1 и неинвертирующим входом операционного усилителя 5, выход которого, являющийся выходом 9 устройства, соединен с одним из выводов второго конденсатора 2 и входом 10 аттенюатора 7. Первый вход 11 аттенюатора 7 через второй ключ 4 соединен с инвертирующим входом операционного усилителя 5 и вторым выводом второго конденсатора 2. Второй вывод первого конденсатора 1 соединен с шиной нулевого потенциала 12, а управляющие входы первого и второго ключей 3 и 4 соединены с управляющим входом 13 устройства. Информационный и управляющий входы третьего ключа 8 соединены соответственно с информационным и управляющим входами 14 и 13 устройства. Выход третьего ключа 8 соединен с информационным входом первого ключа 3 и вторым выходом 15 аттенюатора 7.

Аттенюатор 7 (фиг.1) содержит первый, второй и третий резисторы 16-18, а также повторитель 19 напряжения. При этом первый и второй резисторы 16 и 17 соединены последовательно, образуют делитель напряжения, и включены между входом 10 и шиной 12. Точка соединения первого и второго резисторов 16 и 17 подключена к первому выходу 11 аттенюатора 7 и через повторитель 19 напряжения соединена с одним из выводов третьего резистора 18, второй вывод которого соединен с вторым выходом 15 аттенюатора.

Аттенюатор 7 (фиг. 2) выполнен в виде соединенного первого, второго, четвертого и пятого резисторов 16, 17, 20 и 21, образующих два делителя напряжения.

Аттенюатор 7 (фиг. 3) выполнен в виде первого, второго и третьего резисторов 16-18. При этом первый и второй резисторы 16 и 17 соединены последовательно, образуют делитель и включены между входом 10 и общей шиной 12 аттенюатора 7. Точка соединения первого и второго резисторов 16 и 17 подключена к первому выходу 11 аттенюатора 7 и через третий резистор 18 соединена с вторым выходом 15 аттенюатора.

Устройство для запоминания аналоговой информации работает следующим образом.

Исходно первый и второй конденсаторы 1 и 2, характеризующиеся номинальными значениями емкости С1 и С2, а также первый, второй и третий ключи 3, 4 и 8, имеющие во включенном состоянии малые сопротивления rвкл.3, rвкл.4 и rвкл.8 и выключенном состоянии большие сопротивления Rвыкл.3, Rвыкл.4 и Rвыкл.8, в первом приближении считают идентичными:

C1 = C2 = C, (1)

rвкл.3 = rвкл.4 = rвкл.8 = rвкл, (2)

Rвыкл.3 = Rвыкл.4 = Rвыкл.8 = Rвыкл. (3)

Первый и второй резисторы 16 и 17 аттенюатора 7 также считают идентичными и их сопротивления R16 = R17 = 2R, а коэффициент передачи повторителя 19 напряжения близок к единице. При этом первый и второй конденсаторы 1 и 2 полагают разряженными.

Под влиянием сигнала источника управляющего напряжения, подключаемого между управляющим входом 13 и шиной 12 устройства, первый, второй и третий ключи 3, 4 и 8 переводятся во включенное состояние. При этом с помощью второго ключа 4 к инвертирующему входу операционного усилителя 5 подключаются первый и второй резисторы 16 и 17 аттенюатора 7, которые образуют цепь отрицательной обратной связи.

При действии напряжения источника сигнала, подключаемого между информационным входом 14 и шиной 12 устройства, через включенные третий и первый ключи 8 и 3 и резистор 6 происходит заряд первого конденсатора 1 с постоянной времени

τ31 = [(Ri + rвкл.8)||R18 + rвкл.1 + R6]C1 ≈

(4)

≈ (Ri + R6 + 2 rвкл) C,

где Ri - внутреннее сопротивление источника сигнала; R18 - сопротивление третьего резистора 18 аттенюатора 7, выбираемое из условия R18 >> (Ri + rвкл), реально R18 = R R17 = R; R6 - сопротивление резистора 6.

R17 = R; R6 - сопротивление резистора 6.

Получаемое на первом конденсаторе 1 напряжение передается на выход операционного усилителя 5 с масштабным коэффициентом, определяющимся цепью отрица- тельной обратной связи (в первом приближении K1= 1 +  = 2, которое с помощью первого и второго резисторов 16 и 17 ослабляется (в два раза) и в виде напряжения обратной связи поступает на первый выход 11 аттенюатора 7 и через включенный второй ключ 4 воздействует на инвертирующий вход операционного усилителя 5. Ослабленные напряжения беспрепятственно передается также на выход повторителя 19 напряжения. При данной ситуации разность напряжений, действующая между выводами третьего резистора 18 аттенюатора 7, оказывается незначительной по величине. В связи с этим влияние сопротивления третьего резистора 18 на процесс заряда первого конденсатора 1 заметно не сказывается.

= 2, которое с помощью первого и второго резисторов 16 и 17 ослабляется (в два раза) и в виде напряжения обратной связи поступает на первый выход 11 аттенюатора 7 и через включенный второй ключ 4 воздействует на инвертирующий вход операционного усилителя 5. Ослабленные напряжения беспрепятственно передается также на выход повторителя 19 напряжения. При данной ситуации разность напряжений, действующая между выводами третьего резистора 18 аттенюатора 7, оказывается незначительной по величине. В связи с этим влияние сопротивления третьего резистора 18 на процесс заряда первого конденсатора 1 заметно не сказывается.

Под влиянием разности напряжений, образуемой между выходом и инвертирующим входом операционного усилителя 5, происходит заряд второго конденсатора 2 с постоянной времени

τ32= (R16 || R17 + rвкл.2) С2 = (R + rвкл)С (5)

С целью обеспечения равных постоянных времени заряда (4), (5) при идентичных параметрах (1), (2) номинальное значение сопротивления резистора 6 определяют из условия

R6 = R - Ri - rвкл (6)

Получаемое напряжение отрицательной обратной связи непрерывно сравнивается с напряжением, накапливаемым первым конденсатором 1, образуя между входами операционного усилителя 5 приращение напряжения ΔU. В связи с тем, что напряжение на инвертирующем входе операционного усилителя 5 меньше напряжения, действующего на неинвертирующем входе, на величину ΔU, второй конденсатор 2 в установившемся режиме заряжается до напряжения, превышающего значение напряжения первого конденсатора 1 на величину этого приращения.

По окончании действия напряжения на управляющем входе 13 первый, второй и третий ключи 3, 4 и 8 переходят в выключенное состояние и устройство в целом переводится в режим хранения накопленной аналоговой информации.

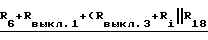

При выключенном третьем ключе 8 напряжение с выхода повторителя 19 через третий резистор 18 беспрепятственно передается на второй выход 15 аттенюатора 7 и далее на информационный вход первого ключа 3 и разность напряжений между его информационным входом и выходом становится такой же (близкой к нулю), что и разность напряжений, действующая между информационным входом и выходом второго ключа 4. В связи с этим первый и второй конденсаторы 1 и 2 начинают постепенно разряжаться с достаточно большими и при идентичных параметрах (1), (3) примерно равными постоянными времени: =

=  C1≈

C1≈  C, (7)

C, (7) =

=  R

R R17+

R17+  C2≈

C2≈  C, (8) где К - коэффициент, характеризующий отношение напряжений, действующих между информационным входом и выходом первого и второго ключей 3 и 4 (этот коэффициент при оговоренных выше условиях весьма близок к единице).

C, (8) где К - коэффициент, характеризующий отношение напряжений, действующих между информационным входом и выходом первого и второго ключей 3 и 4 (этот коэффициент при оговоренных выше условиях весьма близок к единице).

В результате этого разность напряжений ΔU, действующая между входами операционного усилителя 5, во времени изменяется незначительно, поддерживая с достаточно высокой точностью постоянство запомненного выходного напряжения устройства.

При возобновлении сигналов на управляющем и информационном входах 13 и 14 устройства (фиг.1) первый и второй конденсаторы 1 и 2 перезаряжаются с постоянными времени (4) и (5). Причем, если уровень информационного сигнала не превышает уровня хранимого напряжения, то первый и второй конденсаторы 1 и 2 разряжаются, а при обратной ситуации данных сигналов они подзаряжаются до уровня анализируемого сигнала.

Предлагаемое устройство (фиг.1) работает аналогично, если в нем аттенюатор 7 реализован по схемам, представленным на фиг.2,3. Отличие состоит лишь в том, что требуемые напряжения на втором выходе 15 аттенюатора 7 (фиг. 2, а) и сопротивление, эквивалентное сопротивлению третьего резистора 18 (фиг.1), создаются с помощью делителя, состоящего из четвертого и пятого резисторов 20 и 21, аналогично делителю, выполненному на первом и втором резисторах 16 и 17, с теми же номиналами. Достигаемый при этом эффект окажется тем же, если только будет обеспечена идентичность коэффициента К, входящего в выражения (7), (8), для обоих делителей. Однако кажущаяся простота такой реализации аттенюатора 7 (фиг.2), например, для интегрального исполнения является достаточно сложной из-за трудностей выполнения двух точных делителей с идентичными параметрами.

В случае реализации аттенюатора 7 по схеме, представленной на фиг.3, третий резистор 18 подключается к первому выходу 11, на котором действует требуемое значение напряжения. При этом несколько ухудшаются условия заряда первого и второго конденсаторов 1 и 2 (фиг.1), так как существует взаимосвязь зарядных цепей. Однако, когда не требуется высокой точности обработки сигналов, такой вариант реализации аттенюатора 7 (фиг.3) может широко использоваться на практике.

Предлагаемое устройство по сравнению с известными техническими решениями, в том числе и с устройством-прототипом, которое в настоящее время является лучшим спроектированным образцом и которое в связи с этим принимаем за базовый объект, отличается повышенной точностью хранения аналоговой информации. Существенное повышение точности хранения информации достигается за счет обеспечения одинаковых и достаточно больших постоянных времени разряда накопительных конденсаторов путем создания разности потенциалов между информационным входом и выходом первого и второго ключей 3 и 4, близкой к нулю. Это позволяет увеличить их эквивалентные сопротивления в выключенном состоянии реально в десятки или сотни раз.

Выигрыш в точности хранения аналоговой информации определим теоретически.

Изменение выходного напряжения устройства в режиме хранения информации во времени t математически описывается следующим образом:

Uвых(t)=  Ue

Ue -

-  Uвых(t)-(U+ΔU)

Uвых(t)-(U+ΔU) Ko, (9) где U и U + ΔU - напряжения, действующие на первом и втором конденсаторах 1 и 2 в момент времени, когда устройство переходит в режим хранения информации; Δt - текущее время, отсчитываемое с момента перехода устройства в режим хранения информации; Ко - коэффициент передачи операционного усилителя 5.

Ko, (9) где U и U + ΔU - напряжения, действующие на первом и втором конденсаторах 1 и 2 в момент времени, когда устройство переходит в режим хранения информации; Δt - текущее время, отсчитываемое с момента перехода устройства в режим хранения информации; Ко - коэффициент передачи операционного усилителя 5.

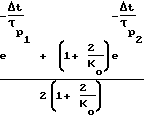

Соотношение (9) представим в другом виде:

Uвых(t)=  U

U e

e +

+  1+

1+

. (10)

. (10)

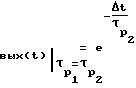

В начальный момент времени, когда Δt= = 0,

Uвых(o)= U =

=  . (11)

. (11)

Полагая, что по свойствам операционного усилителя 5 ΔU =  , выражение (11) позволяет найти:

, выражение (11) позволяет найти:

Uвых(0) = 2U (12)

и =

=  . (13)

. (13)

С учетом соотношений (12) и (13) уравнение (10) приобретает вид:

Uвых(t)= U (14)

(14)

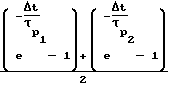

Отсюда находим погрешность хранения информации в предлагаемом устройстве

δUвых(t)=  -1 =

-1 =  (15)

(15)

Так как  ≪ 1, то соотношение для погрешности хранения информации (15) принимает удобный для практического использования вид:

≪ 1, то соотношение для погрешности хранения информации (15) принимает удобный для практического использования вид:

δUвых(t)=  . (16)

. (16)

При условии равенства постоянных времени разряда (7), (8) выражение (16) упрощается:

δU - 1. (17)

- 1. (17)

Выражение (16) может характеризовать и погрешность хранения информации в устройстве-прототипе, если в нем постоянные времени разряда  (7) и

(7) и  (8) заменить на соответствующие постоянные времени разряда

(8) заменить на соответствующие постоянные времени разряда  и τp2*. В устройстве-прототипе только второй ключ 4 находится под разностью потенциалов, близкой к нулю, поэтому постоянная времени разряда первого конденсатора

и τp2*. В устройстве-прототипе только второй ключ 4 находится под разностью потенциалов, близкой к нулю, поэтому постоянная времени разряда первого конденсатора = (R6 + Rвыкл.1 + Ri), C1 ≈ Rвыкл C, (18)

= (R6 + Rвыкл.1 + Ri), C1 ≈ Rвыкл C, (18)

а постоянная времени разряда второго конденсатора  соответствует постоянной времени разряда (8) предлагаемого устройства (

соответствует постоянной времени разряда (8) предлагаемого устройства ( =

= ) . В связи с этим погрешность хранения информации в устройстве-прототипе

) . В связи с этим погрешность хранения информации в устройстве-прототипе

δU . (19)

. (19)

Выигрыш в точности хранения информации, который обеспечивает предлагаемое устройство по отношению к устройству-прототипу, определим на основании сравнения соотношений (17) и (19):

B =  0

0 _ 1

_ 1 . (20)

. (20)

Пусть Δt = 10 с, С = 10-6 Ф(1); rвкл = 103 Ом (2); Rвыкл = 108 Ом (3); К = 0,99; Ко = 105, R =5 ˙103 Ом; Ri = 100 Ом, тогда R6 = 3,9 кОм (6); τ31= τ32= 6 ˙10-3 с (4), (5),  100 с (18);

100 с (18);  =

= 104 с (7), (8); δU

104 с (7), (8); δU = 0,1% (17); δUвых(t)*= 4,808% (19); В = 48,08 (20).

= 0,1% (17); δUвых(t)*= 4,808% (19); В = 48,08 (20).

Таким образом, предложенное устройство является эффективным и может быть использовано как функциональный элемент микроэлектроники при обработке как низкочастотной, так и высокочастотной информации в высокоточных измерительных и других системах.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2006970C1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1495853A1 |

| Аналоговое запоминающее устройство | 1988 |

|

SU1635222A1 |

| Устройство для определения приращений аналогового сигнала | 1985 |

|

SU1288722A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1730683A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1615808A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

Изобретение относится к автоматике и контрольно-измерительной технике, предназначено для осуществления операции выборки-хранения аналоговой информации с повышенной точностью и может быть использовано как функциональный элемент микроэлектроники в системах сбора и распределения данных микропроцессорных устройств. Целью изобретения является повышение точности устройства. Цель достигается за счет введения третьего ключа. Аттенюатор состоит из повторителя напряжения, ограничительного элемента на резисторе и делителе напряжения. Аттенюатор может быть выполнен также на двух делителях напряжения. 2 з.п.ф-лы, 3 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-09-30—Публикация

1991-02-25—Подача