Шuг,f

Изобретение относится к автоматике и контрольно-измерительной техники, оно может быть использовано в устройствах аналоговой и аналого-цифровой обработки информации с преимущественным выпол- нением в виде полупроводниковой интегральной схемы (И С).

Цель изобретения - повышение точности устройства.

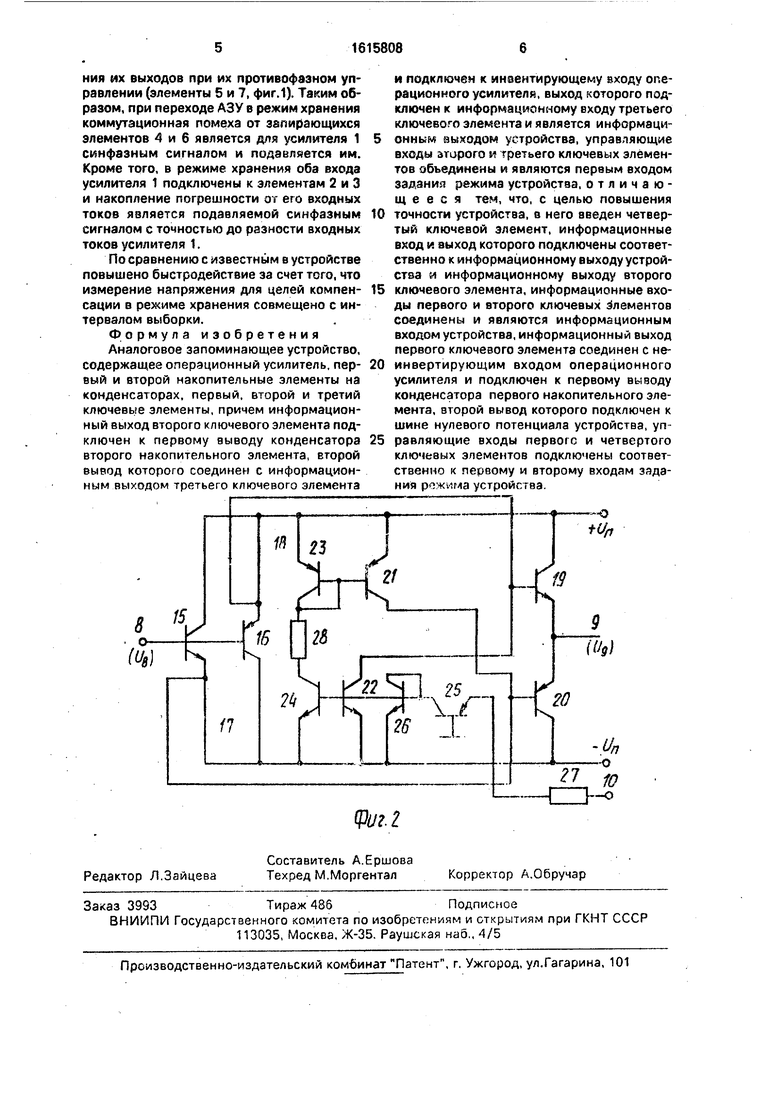

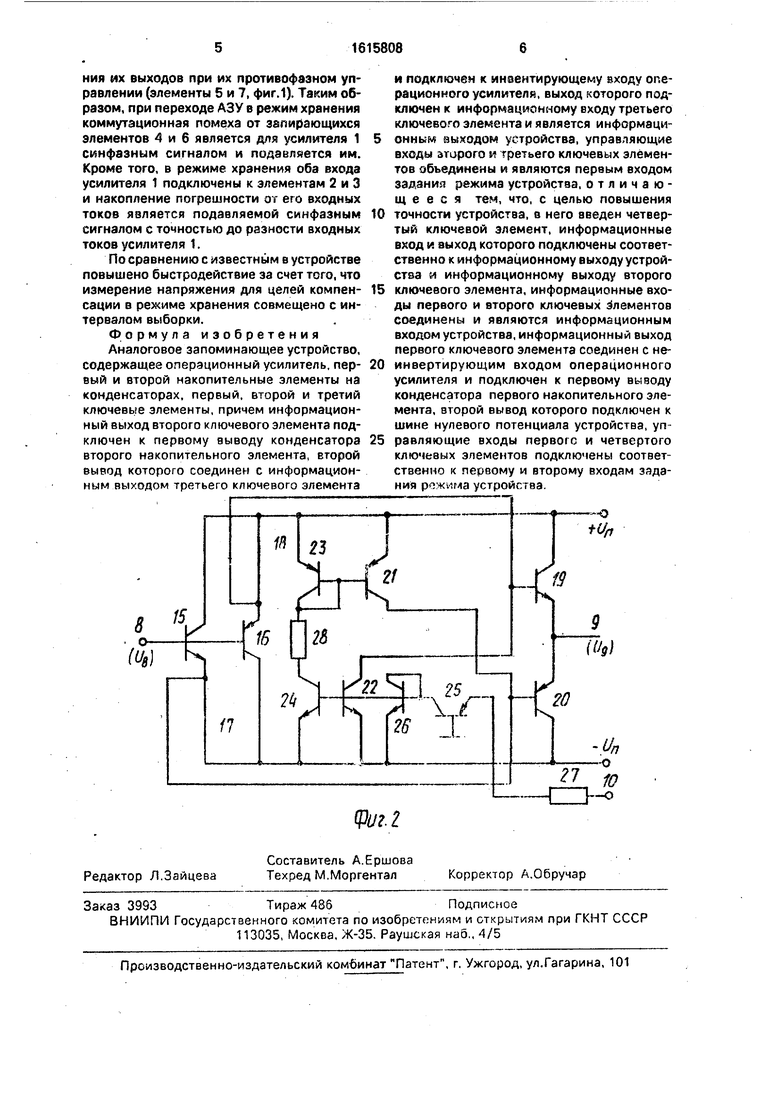

На фиг. 1 представлена схема устройст- ва; на фиг.2 -ключевой элемент.

Устройство содержит операционный усилитель 1, первый и второй накопительные элементы 2 и 3 на конденсаторах, первый, второй, третий и четвертый ключевые элементы 4-7, информационные входы 8 и выходы 9 и управляющие входы 10 ключевых элементов, информационные вход 11 и выход 12 устройства, первый и второй входы 13 и 14 задания режима устройства, пер- вый и второй эмиттерные повторители 15 и 16 на транзисторах, первый и второй источники 17 и 18 тока, двухтактный змиттерный повторитель на транзисторах 19 и 20, токо- задающие элементы 21 и 22 на транзисто- pax, первый и вtopoй отражательные элементы 23 и 24 на транзисторах, управляющий элемент 25 на транзисторе, третий отражательный элемент 26 на транзисторе, первый и второй токоограничительные эле- менты 27 и 28 на резисторах. Элементы 15, 19, 22, 24 и 26 выполнены на транзисторах п-типа, элементы 16, 20, 21, 23, 25.выполнены на транзисторах р-типа.

Аналоговое запоминающее устройство (АЗУ) работает следующим образом.

В режиме выборки сигнала Uii элементы 4-6 открыты, элемент 7 закрыт. В режиме хранения элементы 4-6 закрыты, элемент 7 открыт. Открытое состояние ключевого эле- мента (фиг,2) воспроизводится, когда на входе 10 присутствует напряжение Лог. О. При этом, элемент 25 закрыт и, следовательно, элементы 21, 22, 23, 24 и 26 также находятся в состоянии отсечки тока, При этом напряжение передается через транзистор 15 первого повторителя со смещением -ибэ015, а через транзистор 16 второго повторителя - со смещением + ибэотб. В зависимости от полярности сигнала UB одно из этих напр яжений пропускается не выход 9 соответствующим транзистором 19 или 20 оконечного повторителя со смещением на -ибэ019 или + ибэ020 , так что

U8 -f tk

JUe+(U Ue ( ибэ01в- Ufeoig) при Us о , ,,,

- ибэоп + Ur,) при Ua о ,

Активный ключевой элемент в этом режиме характеризуется высоким входным сопроУивлением и малым выходным сопротивлением, а вносимое напряжение смещения 1к не превышает ± 0,03 мВ. Закрытое состояние ключа (фиг.2) воспроизводится, когда на входе 10 присутствует напряжение Лог.1. В этом случае базозмиттерный переход транзистора 25 открыт, и величине тока управления транзисторар и 21 и 22 отбирается из источников 17 и 18, вследствие чего напряжения на базах транзисторов 20 и 19 соответственно близки « и -Un и оконечный повторитель переходит в закрытое состояние. Активный ютюч в этом режиме характеризуется высоким входным и высоким выходным сопротивлением.

С учетом рассмотренного действия и характеристик активного ключевого элемента в режиме выборки в устройстве (фиг.1) элементы 2 и 3 форсированно заряжаются до соответствующих напряжений Ua и Уз, которые можно рассчитывать следующим образом:

U2 Ul1 + ik4(2)

из Ul2 + 1к6 - (Uti + 1к5) Ul1 + 1к4 + I - - (и11 + 1к5)И-(1к4-1к5),(3)

так как включением элемента 6 усилитель 1 переводится в режим повторителя,

где Ui2 U2 + t - 1кб Uii + к4 + I - кб. (4) Здесь и в дальнейшем IKI обозначает напряжение смещения, вносимое 1-м активным ключевым элементом в открытом состоянии, I - приведенное напряжение смещения усилителя 1.

При переходе в режим хранения напряжение U2 сохраняет свое значение согласно выражению (2), а усилитель 1 переводится в режим запоминания накопленного напряжения из с учетом дополнительного смещения, создаваемого включенным элементом 7, когда элементы 5 и и выключились, т,е. напряжения Уз + 1к7. В этом режиме выходное напряжение АЗУ соответствует входному Un с некоторой погрешностью

U12 Ua + I - (из + 1к7) Un + к4 + i - (I - + 1к4 - 1к5) - 1к7 и 11 + (1к5 - 1к7)(5)

Полезный эффект достигается следующим образом.

При интегральном выполнении ключе- вых элементов АЗУ ожидаемая величина разности 1к5 - к7 по меньшей мере на порядок меньше входящих в разность величин, учитывая, что в конце переходного процзсса выборки все ключевые элементы находятся практически в одинаковом режиме в отношении напряжений между точками 8 и 9, Как следует из выражений (2) - (Б), величина I в режиме хранения подавлена. Коммутационная г1омеха для ключевых элементов возникает в режиме их запирания, кроме того, она существенно подавляется в точке соединения их выходов при их противофазном управлении (элементы 5 и 7, фиг.1). Таким образом, при переходе АЗУ в режим хранения коммутационная помеха от запирающихся элементов 4 и 6 является для усилителя 1 синфазным сигналом и подавляется им. Кроме того, в режиме хранения оба входа усилителя 1 подключены к элементам 2 и 3 и накопление погрешности от его входных токов является подавляемой синфазным сигналом с точностью до разности входных токов усилителя 1.

По сравнению с известным в устройстве повышено быстродействие за счет того, что измерение напряжения для целей компен- сации в режиме хранения совмещено с интервалом выборки.

Формула изобретения Аналоговое запоминающее устройство, содержащее операционный усилитель, пер- вый и второй накопительные элементы на конденсаторах, первый, второй и третий ключевые элементы, причем информационный выход второго ключевого элемента подключен к первому выводу конденсатора второго накопительного элемента, второй вывод которого соединен с информационным выходом третьего ключевого элемента

и подключен к инаентирующему входу операционного усилители, выход которого подключен к информационному входу третьего ключевого элемента и является информационным выходом устройства, управляющие входы зторого и третьего ключевых элементов объединены и являются первым входом задания режима устройства, отличающееся тем, что, с целью повышения точности устройства, в него введен четвертый ключевой элемент, информационные вход и выход которого подключены соответственно к информационному выходу устройства и информационному выходу второго ключевого элемента, информационные входы первого и второго ключевых Элементов соединены и являются информационным входом устройства, информационный выход первого ключевого элемента соединен с неинвертирующим входом операционного усилителя и подключен к первому выводу конденсатора первого накопительного элемента, второй вывод которого подключен к шине нулевого потенциала устройства, управляющие входы первого и четвертого ключевых элементов подключены соответственно к первому и второму входам задания рожигла устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Аналоговое запоминающее устрой-CTBO | 1978 |

|

SU809390A1 |

| Двухтактный усилитель | 1988 |

|

SU1617627A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Устройство аналоговой памяти | 1986 |

|

SU1377916A1 |

| Электронный коммутатор | 1984 |

|

SU1188874A2 |

| Устройство выборки-хранения | 1988 |

|

SU1691896A1 |

| Аналоговое запоминающее устройство | 1988 |

|

SU1522289A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1084898A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано в устройствах аналоговой и аналого-цифровой обработки информации с преимущественным выполнением в виде полупроводниковой интегральной схемы. Цель изобретения - повышение точности устройства. Поставленная цель осуществляется за счет того, что коммутационная помеха, возникающая для ключевых элементов 5,7, в режиме их запирания существенно подавляется в точке соединения их выходов при их противофазном управлении. При переходе устройства в режим хранения коммутационная помеха от запирающих элементов 4,6 является для усилителя 1 синфазным сигналом и подавляется им. В режиме хранения оба входа усилителя 1 подключены к накопительным элементам 2,3 и накопление погрешности от его входных токов является подавляемой синфазным сигналом с точностью до разности входных токов усилителя 1. Кроме того, измерение напряжения в виде аналога для целей компенсации в режиме хранения совмещено с интервалом выборки. 2 ил.

Авторы

Даты

1990-12-23—Публикация

1989-04-06—Подача