Изобретение относится к цифровой вычислительной технике и может быть использовано при построении быстродействующих вычислительных устройств, работающих в знакоразрядной избыточной двоичной системе счисления с алфавитом  , 1, 0.

, 1, 0.

Цель изобретения - увеличение быстродействия преобразователя.

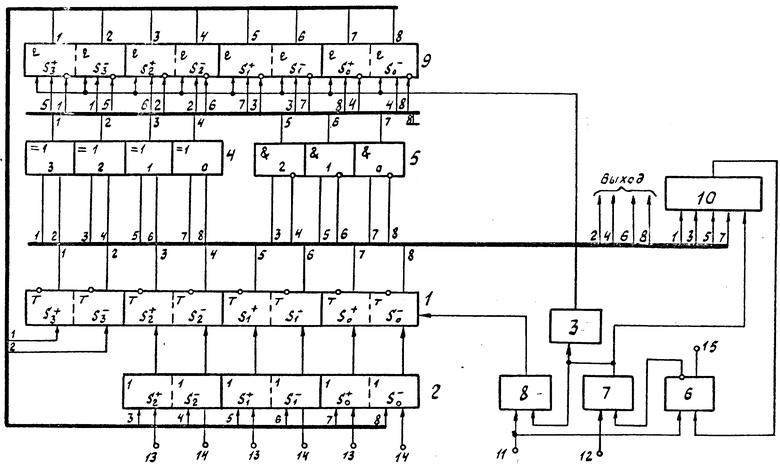

На чертеже представлена блок-схема преобразователя.

Преобразователь содержит регистр 1, группу 2 элементов ИЛИ, элемент 3 задержки, группу 4 элементов неравнозначности, первую группу 5 элементов И, триггер 6, первый элемент И 7, элемент ИЛИ 8, вторую группу 9 элементов И, второй элемент И 10, вход 11 сброса, тактовый 12, информационные 13 и 14 входы, контрольный выход 15.

Преобразователь реализует вариант преобразования, позволяющий получить двоичный код параллельно во всех разрядах путем выполнения конечного числа итераций, не превышающего разрядности преобразуемого числа.

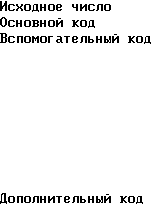

Для получения дополнительного двоичного кода дописывают слова к старшим разрядам исходного числа ноль в знаковом разряде. Пусть А - число в знакоразрядной системе счислений, А = 0, аn-1, аn-2...аo, где а '"∈ (1, 0, 1), i = 0, n-1.

Представляют А в виде двух слагаемых D и  и разлагают их по степеням основания:

и разлагают их по степеням основания:

A= D+ =

=  dj*2j+

dj*2j+

*2k где dj∈(0,1),

*2k где dj∈(0,1),  (

( ),I - подмножество номеров разрядов числа А, которые имеют положительный количественный эквивалент; К - подмножество номеров разрядов числа А, имеющих отрицательный количественный эквивалент.

),I - подмножество номеров разрядов числа А, которые имеют положительный количественный эквивалент; К - подмножество номеров разрядов числа А, имеющих отрицательный количественный эквивалент.

Добавляют и вычитают из А число  , получают А = D +

, получают А = D +  +

+  -

-  или А = D * 2

или А = D * 2  -

-  . Разлагают последнее выражение для А по степеням основания:

. Разлагают последнее выражение для А по степеням основания:

A=  dj*2j+2*

dj*2j+2*

*2k -

*2k -

*2k или, учитывая, что

*2k или, учитывая, что  = -1,

= -1,

A=  dj*2j+

dj*2j+

*2k+1+

*2k+1+  fк*2k.

fк*2k.

Сумму первого и третьего слагаемых, содержащих только разряды с положительным количественным эквивалентом, обозначают через В. Код В представляет собой двоичную запись числа А, в котором все цифры ai =  заменены на 1. Второе слагаемое обозначают как Р. Оно представляет собой двоичный код, состоящий из 0 и 1, причем

заменены на 1. Второе слагаемое обозначают как Р. Оно представляет собой двоичный код, состоящий из 0 и 1, причем

Pi+1=

случае,

случае,

Каждая итерация заключается в нахождении кодов В - основного и Р - вспомогательного и вычисления их суммы

Al = Bl-1 + Pl-1, где l - номер итерации.

Так как положительные и отрицательные единицы сгруппированы в разные слагаемые, то сложение происходит без переносов между соседними разрядами. На каждой итерации вспомогательный код Р сдвигается влево на один разряд, и если отрицательные единицы не будут взаимно уничтожены с единицами основного кода, то они выталкиваются из знакового разряда, поэтому число итераций алгоритма не превышает n. Отсюда следует и его конечность.

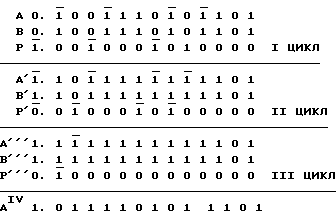

Логическое формирование основного и дополнительного кодов может быть выполнено по табл. 1 непосредственно по числу А. Если после l-й итерации код Al содержит отрицательные единицы, то по нему вновь формируются коды В и Р и цикл повторяется. Признаком окончания процесса является отсутствие отрицательных единиц в полученном коде. Этот код будет дополнительным двоичным кодом исходного знакоразрядного числа. Пример:

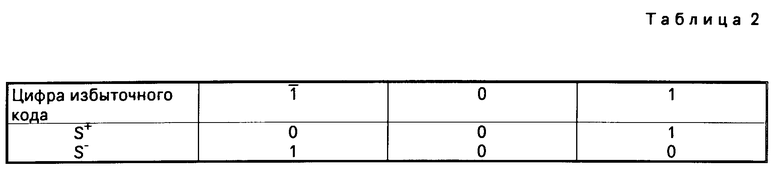

Кодировка цифр  , 0, 1 знакоразрядного кода осуществляется двумя разрядами S+ и S- в соответствии с табл. 2.

, 0, 1 знакоразрядного кода осуществляется двумя разрядами S+ и S- в соответствии с табл. 2.

Работа преобразователя заключается в следующем.

Одиночный сигнал сброса, пришедший на вход 11, обнуляет регистр 1 и устанавливает триггер 6 в ноль. По окончании импульса сброса в регистр 1 через элементы группы ИЛИ по информационным входам 13 (S+) и 14 (S-) записывается знакоразрядный код. С выходов разрядов регистра 1 значения разрядов кода поступают на входы элементов неравнозначности группы 4 для выработки разрядов основного кода В и на элементы И первой группы 5 для выработки разрядов вспомогательного кода Р. Разряды основного и вспомогательного кодов формируются согласно логическим выражениям

bi=  (S

(S (S

(S

Pi+1= (S

(S

Сформированные разряды кодов поступают на элементы И второй группы 9, причем i-й разряд основного кода поступает на вход i-го элемента И группы 9, а i-й разряд вспомогательного кода поступает на вход (i+1)-го элемента И группы 9. На выходе i-го элемента группы 9 получается i-й разряд кода А, вычисляемый по формуле

ai = bi. Pi-1.

Очередной тактирующий импульс 12, пройдя через схемы И 7 и ИЛИ 8, обнуляет регистр 1, задержанный тактирующий импульс с выхода элемента 3 задержки разрешает прохождение сигналов на выход элементов И группы 9. Учитывая конечность времени распространения сигналов по группам схем, несмотря на то, что регистр 1 обнулен, на выходах элементов И группы 9 сохраняется текущее значение кода А, который через элементы ИЛИ группы 2 записывается в регистр 1. Сигналы с выходов регистра 1 подаются также на входы элемента И 10. Этот элемент проверяет отсутствие отрицательных единиц в коде, записанном в регистре 1. Сигнал на его выходе служит признаком окончания формирования двоичного дополнительного кода. Элемент И 10 реализует функцию

,...,

,...,

=1

=1

Если при поступлении на вход элемента И 10 тактирующего импульса с выхода элемента и 7 на его выходе появляется сигнал, то он устанавливает в единичное состояние триггер 6, который прекращает поступление тактирующих импульсов 12 на преобразователь через элемент И 7. В регистре 1 хранится дополнительный двоичный код исходного знакоразрядного числа, а сигнал с единичного выхода 15 триггера 6 служит признаком окончания перевода.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2047919C1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для суммирования | 1977 |

|

SU734678A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении быстродействующих вычислительных устройств, работающих в знакоразрядной избыточной двоичной системе счисления с алфавитом 1,1,0. Цель изобретения - увеличение быстродействия преобразователя. Преобразователь содержит регистр 1, группу 2 элементов ИЛИ, элемент 3 задержки, группу 4 элементов неравнозначности, первую группу 5 элементов И, триггер 6, первый элемент И 7, элемент ИЛИ 8, вторую группу 9 элементов И, второй элемент И 10, вход 11 сброса, тактовый 12, информационные 13 и 14 входы, контрольный выход 15. 2 табл. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД, содержащий регистр, выходы разрядов которого являются информационными выходами преобразователя и соединены с входами соответствующих элементов неравнозначности группы, первую группу элементов И, первый элемент И, первый вход которого является тактовым входом преобразователя, элемент задержки, отличающийся тем, что, с целью повышения быстродействия, в него введены триггер, элемент ИЛИ, второй элемент И, вторая группа элементов И и группа элементов ИЛИ, первые и вторые входы элементов ИЛИ группы являются информационными входами преобразователя, выходы соединены с входами соответствующих разрядов регистра, начиная с второго разряда, входы элементов И первой группы подключены к выходам соответствующих разрядов регистра, начиная с второго, выходы элементов неравнозначности группы и выходы элементов И первой группы соединены соответственно с первыми и вторыми входами соответствующих элементов И второй группы, выход первого элемента И второй группы соединен с входом первого разряда регистра, выходы элементов И, начиная с второго, второй группы соединены с третьими входами соответствующих элементов ИЛИ группы, выход первого элемента И соединен с входом элемента задержки, первым входом элемента ИЛИ и первым входом второго элемента И, вторые входы которого подключены к выходам соответствующих разрядов регистра, выход второго элемента И соединен с S-входом триггера, R-вход которого объединен с вторым входом элемента ИЛИ и является входом сброса преобразователя, инверсный выход триггера соединен с вторым входом первого элемента И, прямой выход - контрольным выходом преобразователя, выход элемента ИЛИ соединен с входом загрузки регистра, выход элемента задержки - с третьими входами элементов И второй группы.

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1990-01-30—Подача