Изобретение относится к запоминающим устройствам динамического типа, выполненным в виде больших интегральных схем (БИС), и может быть использовано в современных ЭВМ и устройствах памяти.

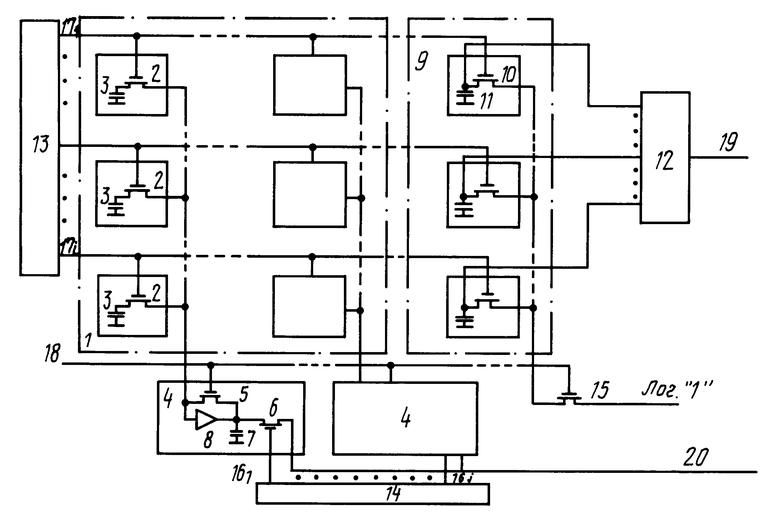

На чертеже приведена функциональная схема устройства.

Устройство содержит матричный накопитель 1, построенный на однотранзисторных элементах памяти, включающий запоминающие транзисторы 2 элементов памяти, запоминающие конденсаторы 3 элементов памяти, усилители 4 записи-считывания, построенные на первых 5 и вторых 6 транзисторах, конденсаторах 7 и операционных усилителях 8, динамический регистр 9, выполненный на транзисторах 10 и конденсаторах 11, элемент И 12, дешифраторы 13, 14 строк и столбцов соответственно, ключ на транзистор 15, шину 16 выбора столбцов, шину 17 выбора строк, шину 18 управления, выход 19 запроса на регистрацию, шину 20 ввода-вывода данных.

Устройство работает в режимах записи, считывания, регенерации.

В режиме записи сигналом с выхода дешифратора строк 13 выбираются все элементы памяти строки, например элемент 171. Сигналом с выхода дешифратора столбцов, например элементом 161, открывается транзистор 6 соответствующего усилителя записи-считывания 4.

Информационные сигналы с запоминающих конденсаторов 3 через открытые запоминающие транзисторы 2 всех элементов памяти выбранной строки матричного накопителя 1 поступают на входы операционных усилителей 8 усилителей записи-считывания 4 и после усиления запоминаются на конденсаторах 7. Внешний информационный сигнал 0 (1) поступает по шине 20 через транзистор 5 на конденсатор 3 однотранзисторного элемента памяти, находящиеся на пересечении выбранной строки и выбранного столбца. Одновременно происходит перезапись информации во все элементы памяти выбранной строки, что равносильно регенерации строки. В элемент памяти динамического регистра 9, соответствующего выбранной строке, через транзисторы 15 и 10 записываются уровень логической "1".

В режиме считывания сигналом с выхода дешифратора строк 13, 171 выбираются все элементы памяти одной строки, включая соответствующий элемент памяти динамического регистра 9. Информационные сигналы с запоминающих конденсаторов 3 через открытые запоминающие транзисторы 2 всех элементов памяти выбранной строки матричного накопителя 1 поступают на входы операционных усилителей 8 усилителей записи-считывания 4 и после усиления запоминаются на конденсаторах 7. Сигнал с выхода дешифратора столбцов 14 (например, 161) открывает один из транзисторов 6 и информация с соответствующего конденсатора 7 поступает на выход устройства по шине 20. Затем импульсом, поступающим по шине управления 18, информация с конденсаторов 7 через транзисторы 5 и запоминающие транзисторы 2 переписывается на запоминающие конденсаторы 3 всех запоминающих элементов памяти выбранной строки. При этом в соответствующий элемент динамического регистра 9 через транзисторы 15 и 10 записывается уровень логической "1". Таким образом, при считывании информации из любой ячейки матричного накопителя происходит регенерация информации во всех запоминающих элементах выбранной строки, включая запоминающий элемент динамического регистра 9.

При длительном необращении к какой-либо строке происходит снижение уровня напряжения на конденсаторе 11 и на выходе элемента И 12 появляется сигнал низкого уровня запрос устройства на регенерацию. Постоянная времени элемента памяти динамического регистра 9 выбирается меньшей постоянной времени элемента памяти матричного накопителя 1, чтобы избежать потерю информации на величину, достаточную на проведение регенерации, что зависит от количества строк в каждом конкретном типе оперативного запоминающего устройства.

В режиме регенерации дешифратор столбцов 14 блокирован и шина ввода-вывода 20 находится в отключенном состоянии. Сигналом с выхода дешифратора строк 13, например 171, выбираются все элементы памяти одной строки, включая соответствующий элемент памяти динамического регистра 9. Информационные сигналы с запоминающих конденсаторов 3 через открытые запоминающие транзисторы 2 всех элементов памяти выбранной строки матричного накопителя поступают на входы операционных усилителей 8 усилителей записи-считывания 4 и после усиления запоминаются на конденсаторах 7. Затем импульсом, поступающим по шине управления 18 через транзисторы 5 и запоминающие транзисторы 2, переносится на запоминающие конденсаторы 3. При этом в соответствующий элемент памяти динамического регистра 9 записывается логическая "1". Регенерация остальных строк происходит аналогично. Следующий цикл регенерации инициируется сигналом запроса на регенерацию устройства.

Процент повышения пpоизводительности предлагаемого устройства зависит от конкретной программы. Если в программе обращение к ячейкам оперативного запоминающего устройства (ОЗУ) происходит последовательно по адресам, то принудительная регенерация не будет проводиться совсем, т.е. потери времени на регенерацию практически будут равны нулю. Для "неблагоприятных" программ потери времени на регенерацию останутся такими же.

В среднем применение предлагаемого устройства позволяет снизить потери времени на регенерацию на 2% В реальных условиях эти потери обычно меньше, так как в скомпанованных программах большая часть обращений к оперативным запоминающим устройствам происходит последовательно по адресам ячеек ОЗУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Интегральное запоминающее устройство | 1974 |

|

SU523455A1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

Изобретение относится к запоминающим устройствам динамического типа, выполненным в виде больших интегральных схем, и может быть использовано в современных ЭВМ и устройствах памяти. В устройство введены динамический регистр, ключ на транзисторе и элемент И. 1 ил.

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матричный накопитель с элементами памяти, усилители записи-считывания, дешифратор столбцов, дешифратор строк, выходы которого подключены к затворам соответствующих запоминающих транзисторов элементов памяти, истоки которых через запоминающие конденсаторы элементов памяти соединены с шиной нулевого потенциала устройства, стоки всех запоминающих транзисторов элементов памяти каждого столбца соединены общей шиной и подключены к входу операционного усилителя соответствующего усилителя записи-считывания и к истоку первого транзистора, сток которого подключен к выходу операционного усилителя, к истоку второго транзистора и через конденсатор к шине нулевого потенциала, выходы дешифратора столбцов подключены к затворам соответствующих вторых транзисторов, стоки которых объединены шиной ввода-вывода данных устройства, затворы первых транзисторов объединены шиной управления устройства, отличающееся тем, что, с целью повышения производительности оперативного запоминающего устройства, в него введены динамический регистр, ключ на транзисторе и элемент И, выход которого является выходом запроса на регенерацию устройства, а входы подключены к истокам соответствующих запоминающих транзисторов динамического регистра и через конденсаторы к шине нулевого потенциала устройства, стоки запоминающих транзисторов динамического регистра объединены и соединены с истоком транзистора, сток которого соединен с шиной логической единицы устройства, а затвор подключен к шине управления устройства, затворы запоминающих транзисторов динамического регистра подключены к соответствующим выходам дешифратора строк.

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-11-10—Публикация

1991-01-02—Подача