Предлагаемое изобретение относится к области вычислительной техники, а именно к цифровой обработке сигналов и данных, решению задач математической физики и САПР, и может найти применение в конвейерных потоковых машинах и многопроцессорных вычислительных системах.

Известно устройство суперкомпьютер RS/6000 SP (см. Андреев А. Обзор архитектуры суперкомпьютеров серии RS/6000 SP корпорация IBM//http: //parallel.ru/computers/reviews/sp2 overview.html).

Суперкомпьютер SP корпорации IBM - масштабируемая массивно-параллельная вычислительная система "общего назначения", представляющая собой набор рабочих станций RS/6000, соединенных высокопроизводительным коммутатором.

Недостатком этого устройства является то, что коммутационная сеть имеет многостадийную (multistage) или непрямую (indirect) структуру.

Причина недостатков состоит в том, что коммутирующая плата непосредственно связана каждая с каждой четырьмя каналами. Для большого количества узлов необходимы промежуточные коммутационные платы, что увеличивает стадийность сети и, как следствие, существенно замедляет скорость обмена информацией.

Известно устройство параллельного процессора BBN Butterfly (см. А.Р.Ларраби, К. Э.Пенник, С.М.Стерн. Параллельный процессор BBN Butterfly.//В кн. Программирование на параллельных вычислительных системах. Под ред. Р.Бэбба II. - М.: Мир, 1991. - с. 57).

Система Butterfly представляет собой сильносвязанную ЭВМ типа MIMD с общей памятью. Система состоит из процессорных узлов и коммутатора типа "бабочка".

Недостатком этого устройства является жесткая топология межпроцессорных обменов по схеме "бабочка", в основном, используемая при реализации алгоритма БПФ и других методов дискретных преобразований, но затрудняющая реализацию межпроцессорного обмена при других задачах важных классов, например математическая физика, САПР и моделирование. Кроме того, существует вероятность возникновения конфликтов в процессе передачи информации, для разрешения которых необходимо уменьшить скорость транспортировки данных.

Причина недостатков - ориентация процессора на определенный тип задач.

Наиболее близким к предлагаемому изобретению является базовый узел вычислительной системы Supernode (см. Вычислительные процессы и системы. /Под редакцией Г. И.Марчука. "Наука". Выпуск 7. -М.: Главная редакция физико-математической литературы, 1990. -с. 62-63), содержащий восемнадцать транспьютеров, 16 из которых являются рабочими и выполняют весь объем вычислений. Каждый из транспьютеров подключен к коммутатору.

Недостатком этого устройства является низкое быстродействие на определенном классе задач (при реализации сильносвязанных задач, когда число обменов между процессорами, в данном случае транспьютерами, сопоставимо с числом операций, выполняемых в процессорах, реальная производительность Supernode будет существенно ниже пиковой).

Причина недостатков состоит в том, что обработка информации в транспьютерах выполняется в параллельном коде, а обмен информацией идет в последовательном коде. Транспьютеры будут находиться в состоянии ожидания данных от других транспьютеров и чем больше будет степень связанности задачи (отношение числа пересылок к числу операций), тем ниже реальная производительность.

Задача, на решение которой направлено заявляемое изобретение, заключается в создании вычислительного устройства многопроцессорной системы, реальная производительность которого близка к пиковой на широком классе задач, в том числе и для сильносвязанных задач.

Технический результат, достигаемый при осуществлении изобретения, состоит в том, что обработка информации и обмен информацией осуществляются согласованно (для одинакового числа разрядов и одинаковой тактовой частоты). Обработка информации ведется в знакоразрядном коде старшими разрядами вперед, что позволяет повысить тактовую частоту за счет того, что в результате обработки операндов в знакоразрядном коде перенос распространяется на один разряд. Кроме того, за счет аппаратной синхронизации операндов упрощается программирование.

Для достижения указанного технического результата в устройство, содержащее коммутатор, вместо транспьютеров введены процессоры умножения ПУ и процессор сложения ПС, реализующие обработку информации в знакоразрядном коде, причем, информационные знакоразрядные входы макропроцессора подключены к первым входам коммутатора, выходы которого соединены с первыми и вторыми информационными знакоразрядными входами процессоров, третьи входы которых соединены с вторыми входами макропроцессора, первые выходы процессоров являются выходами результатов макропроцессора и соединены с вторыми входами коммутатора, третьи входы которого соединены с вторыми выходами процессоров, третьи выходы которых являются выходами сигнала отказа макропроцессора.

Причинно-следственная связь между совокупностью существенных признаков заявляемого изобретения и достигаемым техническим результатом заключается в следующем: введение в устройство новых типов процессоров, осуществляющих обработку информации в знакоразрядном последовательном коде и соединенных между собой внутренней пространственной коммутационной системой по полному графу, позволяет повысить быстродействие вычислений при решении сильносвязанных задач за счет структурной (аппаратной) реализации крупных математических операций, использование знакоразрядного кода позволяет повысить быстродействие вычислений в несколько раз, например, в случае использования четверичного избыточного кода для представления чисел быстродействие увеличивается в два раза по сравнению с двоичной системой, согласованная обработка и передача информации позволяет уменьшить общее время решения сильносвязанных задач, аппаратная реализация крупных математических задач позволяет упростить программирование задач различных проблемных областей.

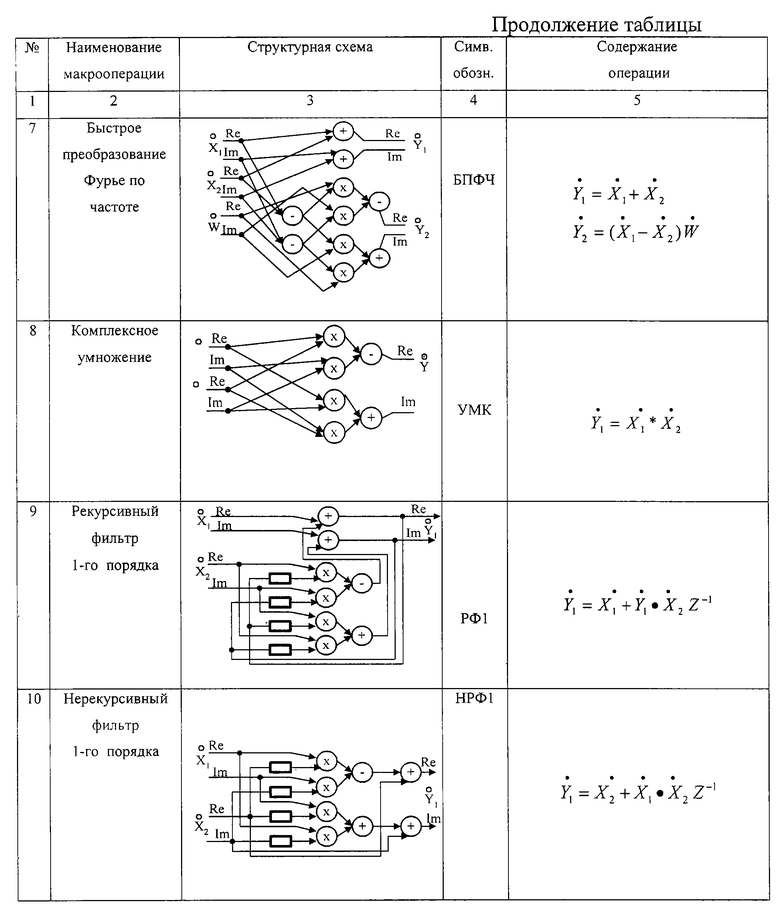

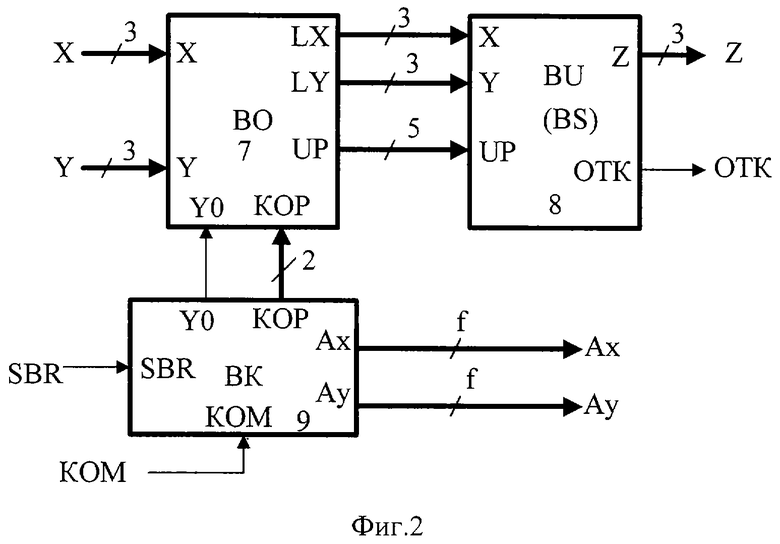

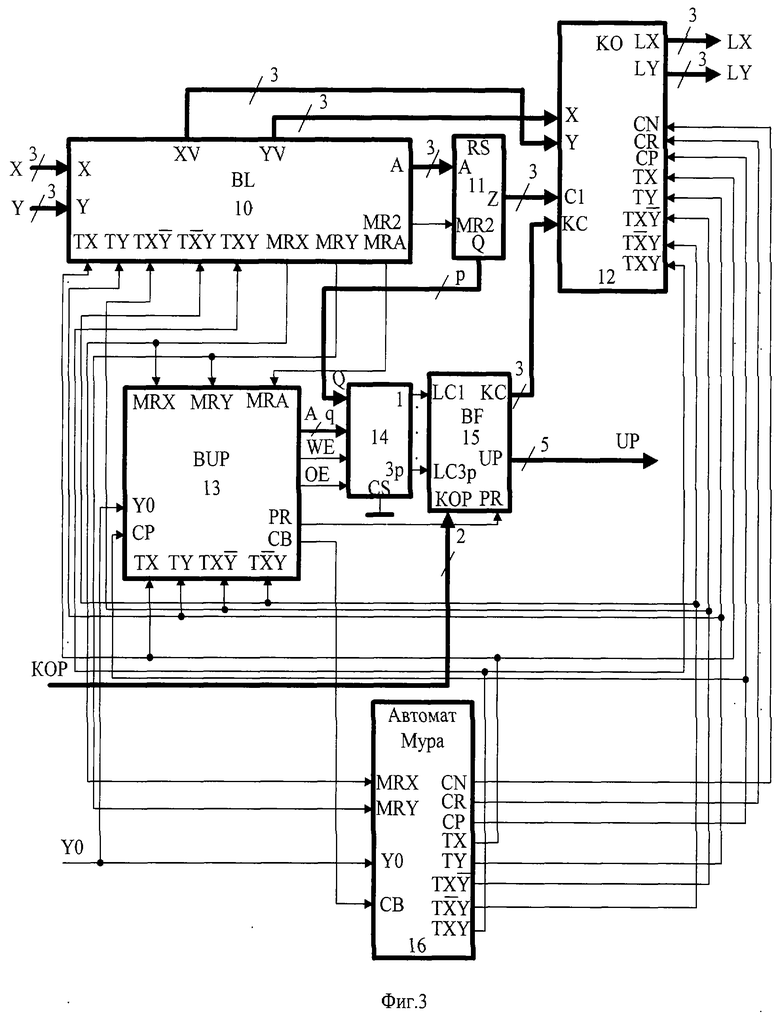

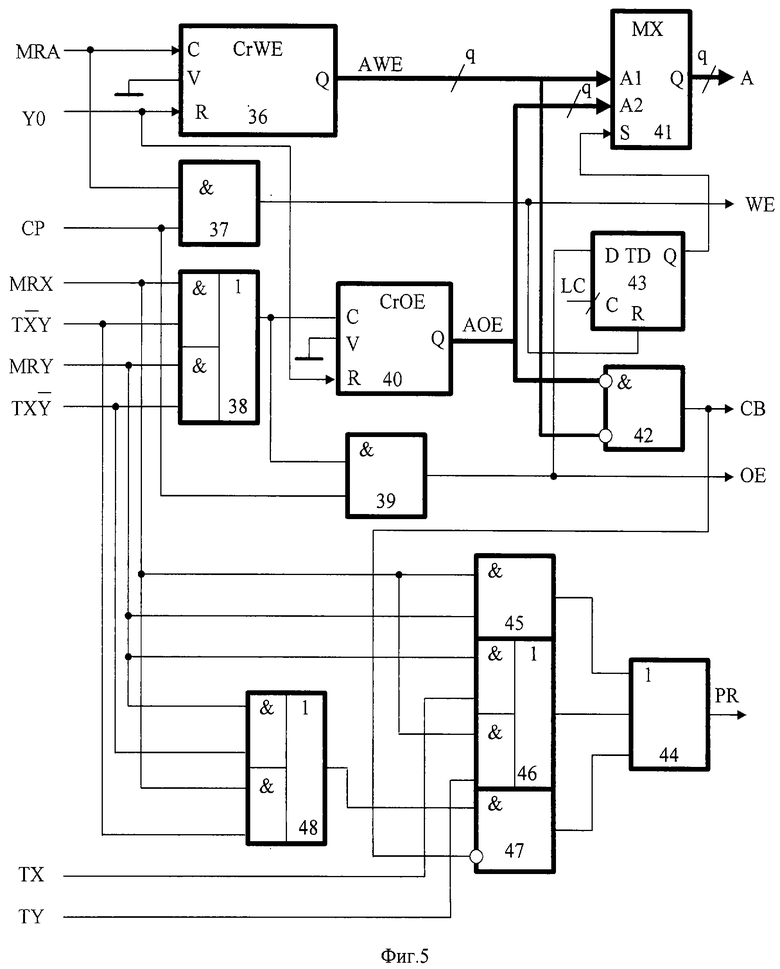

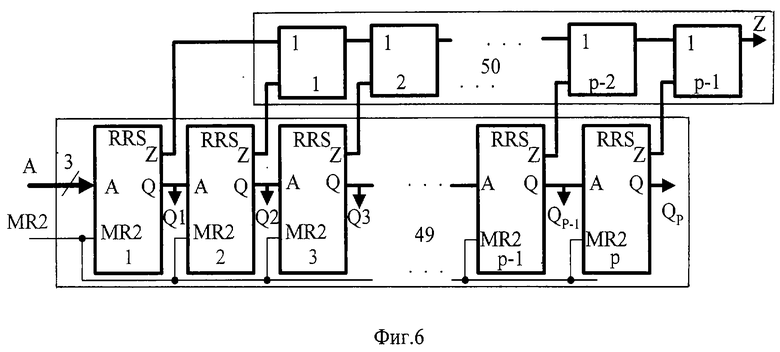

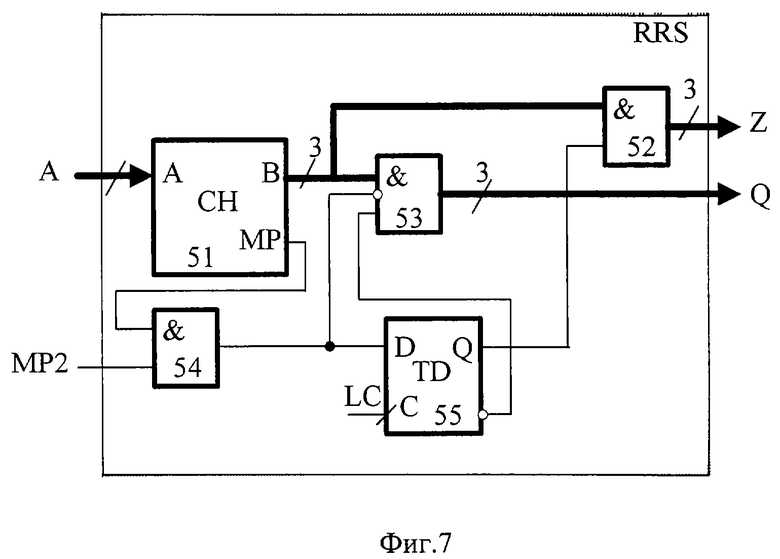

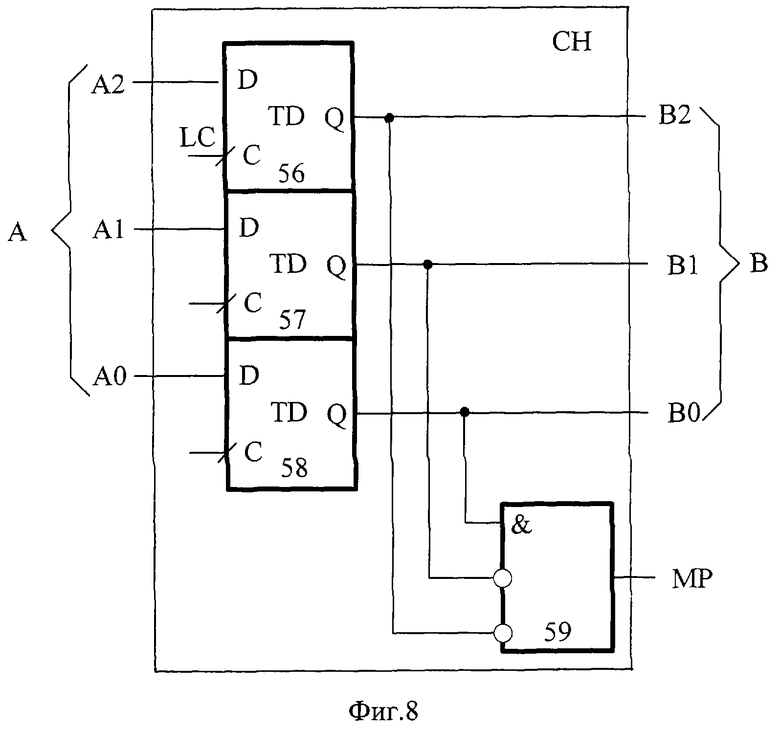

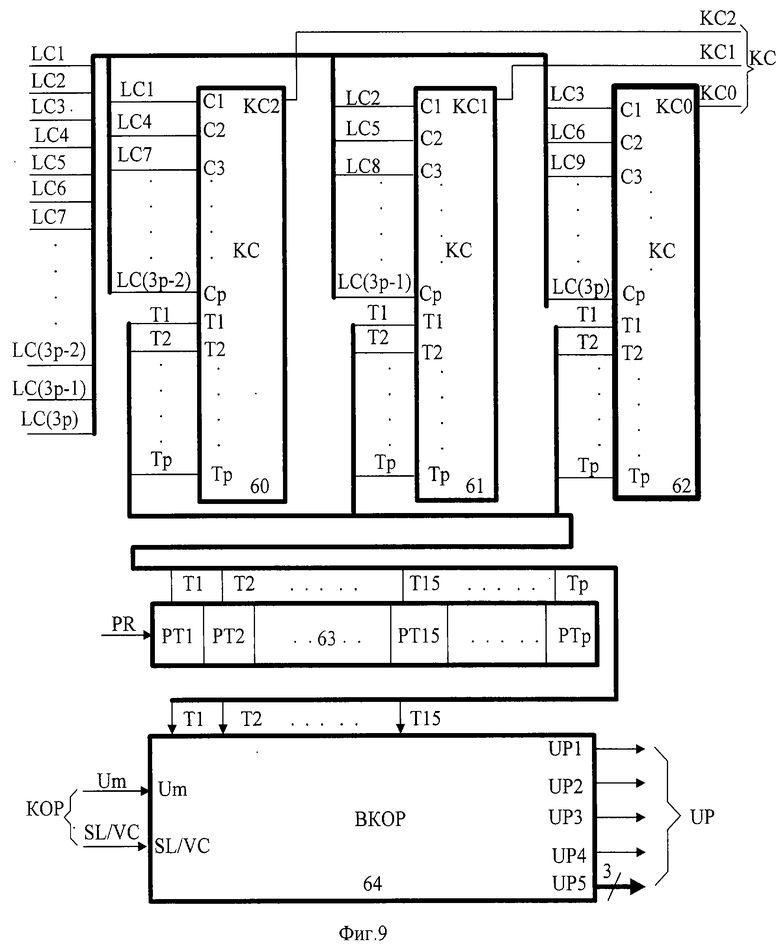

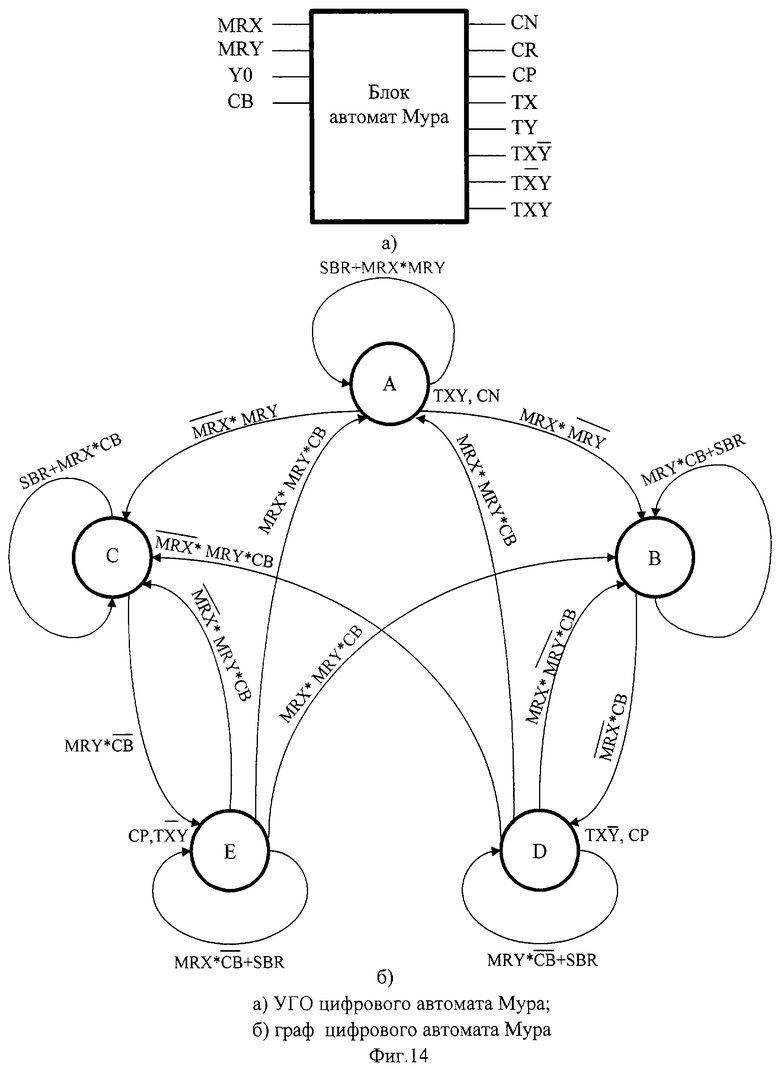

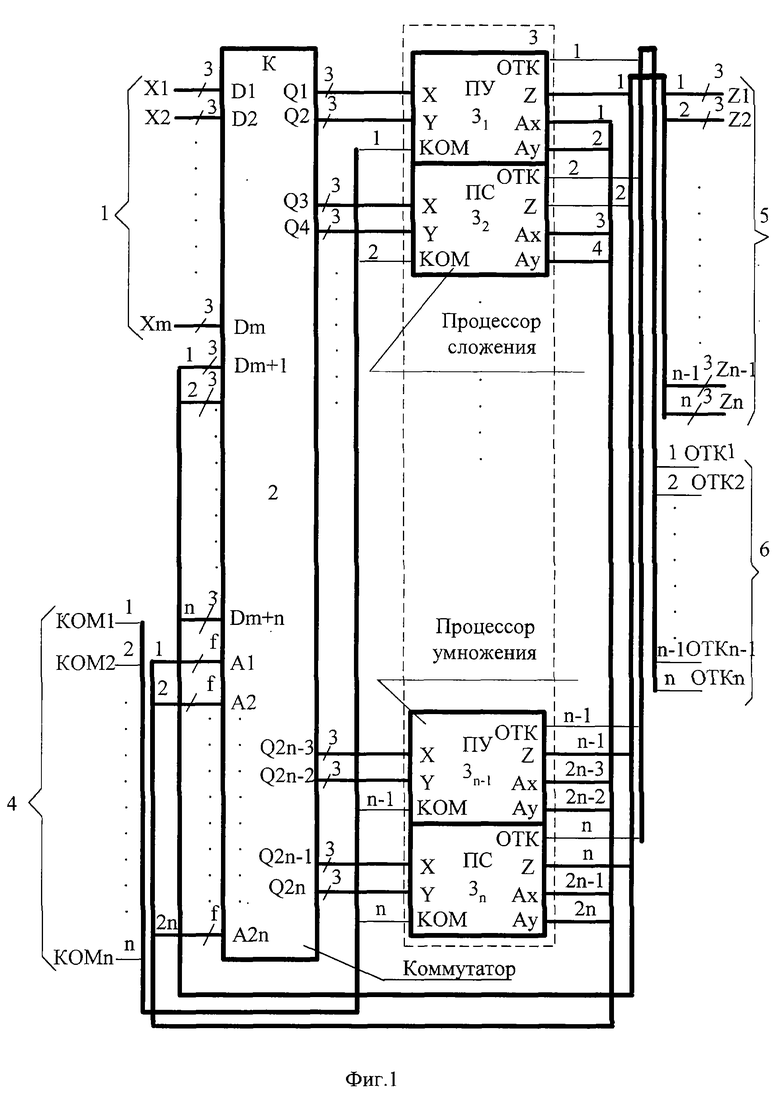

Изобретение поясняется чертежами, где на фиг.1 представлена блок-схема устройства макропроцессора МАП, на фиг.2 - процессор умножения ПУ (процессор суммирования ПС), на фиг.3 - блок операндов ВО, на фиг.4 - входной блок BL, на фиг.5 - блок управления памятью BUP, на фиг.6 - регистр синхронизации RS, на фиг. 7 - разряд регистра синхронизации RRS, на фиг.8 - ячейка разряда регистра синхронизации СН, на фиг.9 - преобразователь кода BF, на фиг.10 - блок преобразователя кода КС, на фиг.11 - блок кода операции ВКОР, на фиг.12 - выходной коммутатор КО, на фиг.13 - блок команд ВК, на фиг.14-блок автомат Мура.

Устройство содержит входы 1, по которым поступают знакоразрядные коды операндов X1-Хm, коммутатор 2, блок 3 процессоров (31-3n), входы 4, по которым поступают команды KOM1-KOMn на входы процессоров, выходы 5 устройства - выходы результатов Z1-Zn блока процессоров, выходы 6 устройства - выходы отказа ОТK1-ОТКn блока процессоров.

Процессор умножения ПУ (процессор суммирования ПС) (фиг.2) содержит блок 7 операндов ВО, блок 8 умножения (суммирования), блок 9 команд ВК.

Блок 7 операндов (фиг.3) содержит входной блок 10, регистр 11 синхронизации, выходной коммутатор 12, блок 13 управления памятью, блок 14 памяти, преобразователь 15 кода, блок 16 автомат Мура.

Входной блок 10 (фиг.4) содержит два элемента И17, 18, три элемента И-ИЛИ 19, 20, 21, шесть элементов И22-27, два элемента ИЛИ-И 28, 29, элемент ИЛИ 30, два элемента И31, 32, два триггера TD 33, 34, элемент И-ИЛИ 35.

Блок 13 управления памятью (фиг.5) содержит счетчик 36 адреса записи, элемент И37, элемент И-ИЛИ38, элемент И39, счетчик 40 адреса чтения, мультиплексор 41, элемент И 42, триггер TD 43, элемент ИЛИ 44, элемент И45, элемент И-ИЛИ 46, элемент И47, элемент И-ИЛИ 48.

Регистр 11 синхронизации (фиг.6) содержит блок 49 разрядов регистра синхронизации RRS 491÷49р, блок 50 элементов ИЛИ 501÷50p-1.

Разряд регистра синхронизации (фиг. 7) содержит ячейку 51 разряда регистра синхронизации, три элемента И52-И54, триггер TD 55.

Ячейка 51 разряда регистра синхронизации (фиг.8) содержит три триггера TD 56÷58, элемент И59.

Преобразователь 15 кода (фиг.9) содержит три блока КС60-62 преобразователя кода, распределитель 63 тактовых импульсов, блок 64 кода операции.

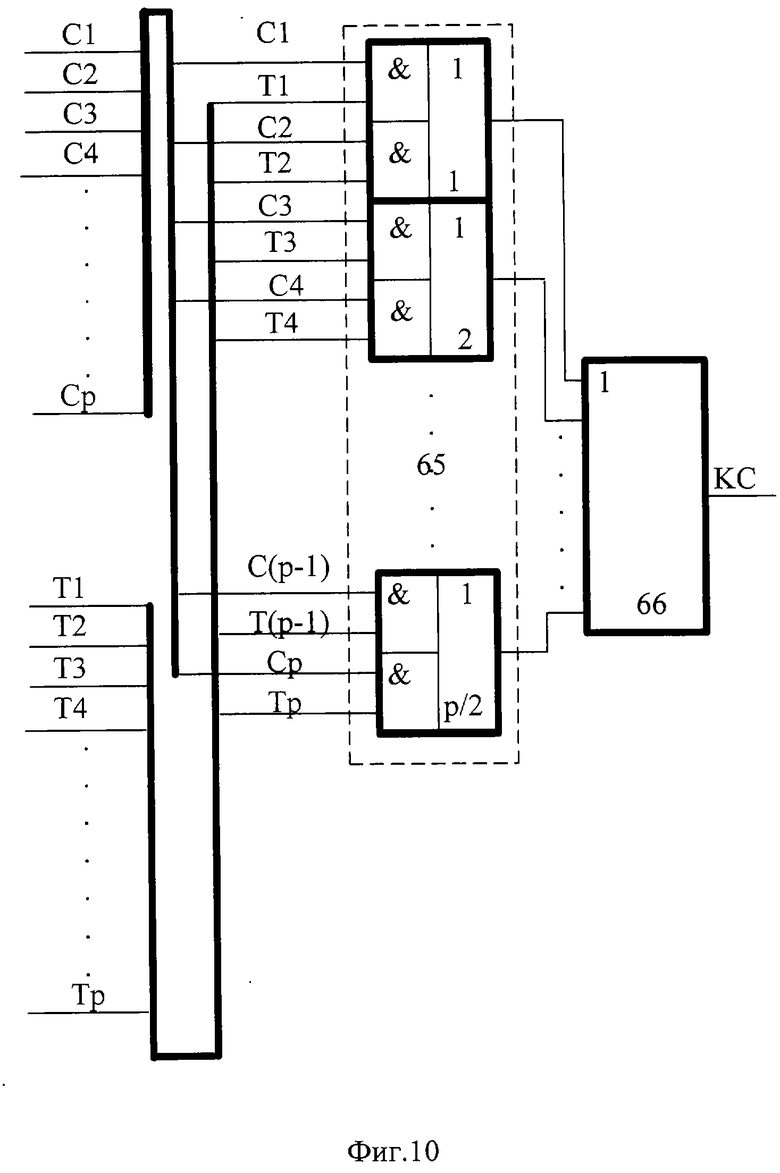

Блок преобразователя кода КС (фиг.10) содержит блок 65 элементов И-ИЛИ  , элемент ИЛИ 66.

, элемент ИЛИ 66.

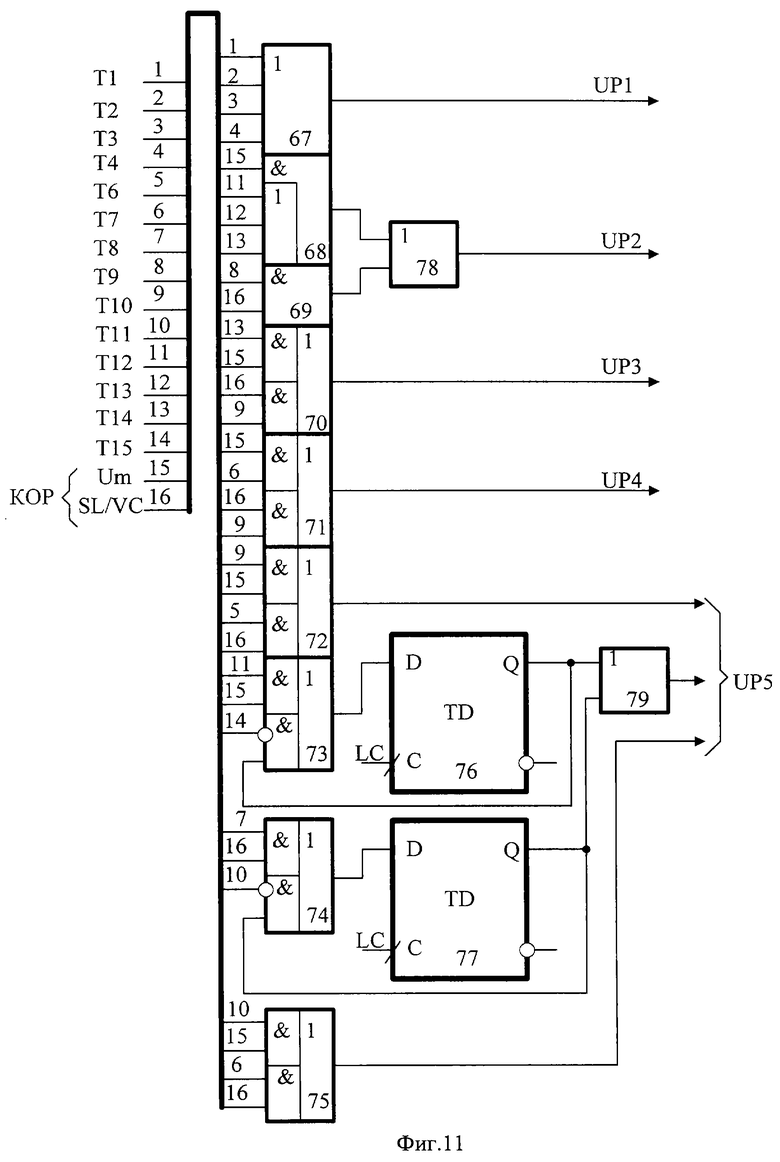

Блок 64 кода операции (фиг.11) содержит элемент ИЛИ67, элемент ИЛИ-И 68, элемент И69, шесть элементов И-ИЛИ 70-75, два триггера TD 76, 77, два элемента ИЛИ 78, 79.

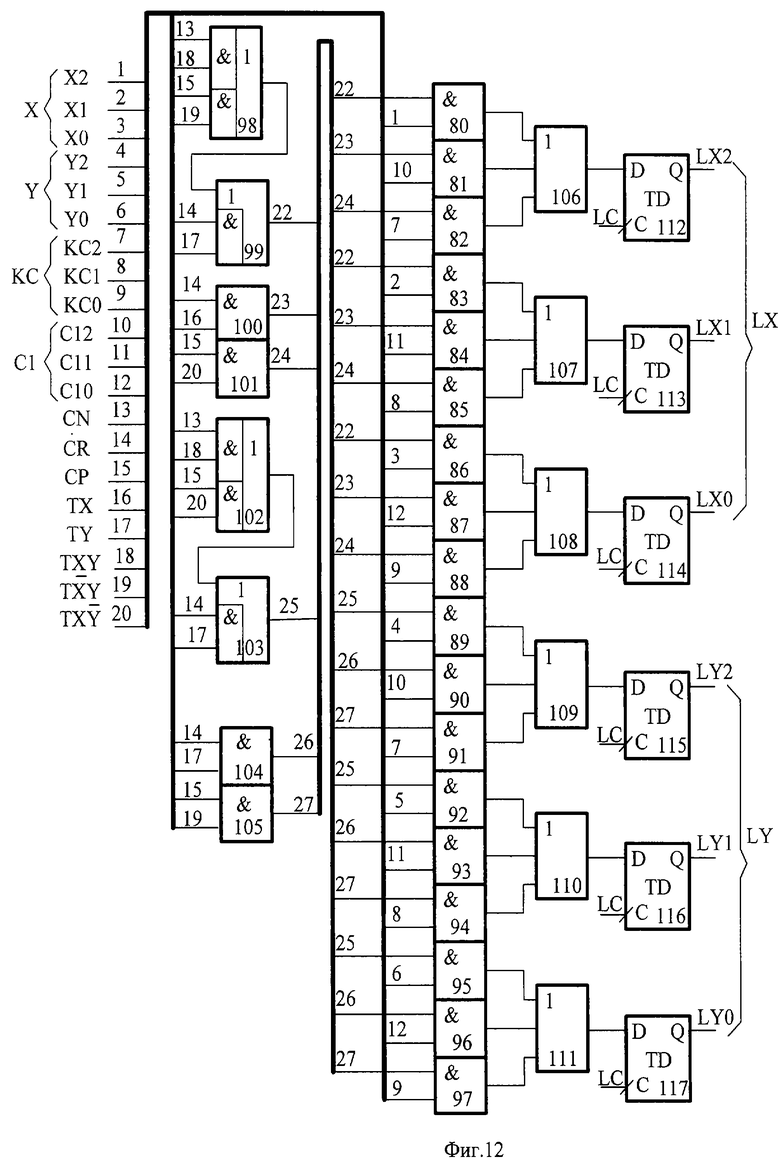

Выходной коммутатор 12 (фиг.12) содержит восемнадцать элементов И80-97, два элемента И-ИЛИ 98, 99, два элемента И100, 101, два элемента И-ИЛИ 102, 103, два элемента И104, 105, шесть элементов ИЛИ 106-111, шесть триггеров TD 112-117.

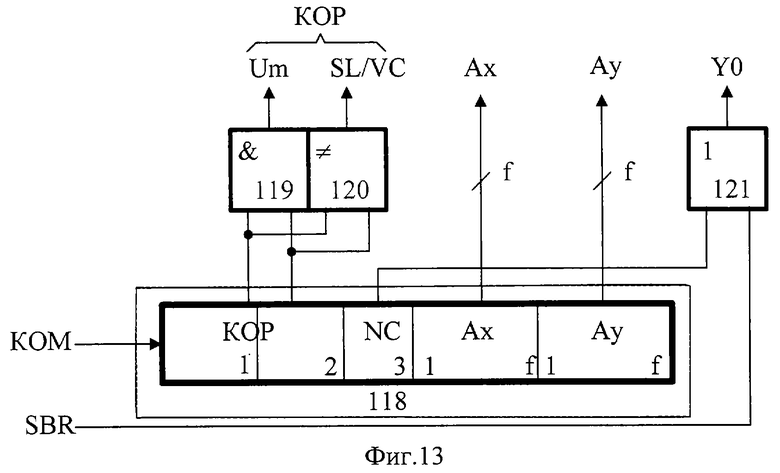

Блок 9 команд (фиг.13) содержит регистр 118 команд, элемент И119, элемент неравнозначности 120, элемент ИЛИ 121.

Блок 16 автомат Мура (фиг.14) содержит граф цифрового автомата Мура и его условное графическое обозначение УГО.

Входы 1 знакоразрядных операндов X1-Хm устройства подключены к первым входам Dl-Dm коммутатора 2 (фиг.1), знакоразрядные выходы которого соединены с первыми Х и вторыми Y знакоразрядными входами блока 3 процессоров ПУ и ПС, третьи входы КОМ которых соединены с вторыми входами 4 устройства, первые выходы процессоров блока 3 соединены с вторыми входами Dm+1-Dm+n коммутатора 2 и являются выходами 5 результатов Zl-Zn устройства, третьи входы адресов А1-А2n коммутатора 2 соединены с вторыми выходами Ах и Ау блока 3 элементарных процессоров, третьи выходы которых являются выходами 6 сигналов отказа ОТК1-ОТКn устройства.

Первый Х и второй Y входы процессоров ПУ (ПС) (фиг.2) соединены соответственно с первым и вторым знакоразрядными входами блока 7 операндов, первый LX и второй LY знакоразрядные выходы которого соединены соответственно с первым и вторым входами блока 8 умножения (суммирования), третий вход UP которого соединен с третьим выходом блока 7 операндов, третий вход Y0 и четвертый вход КОР которого соединены соответственно с первым Y0 и вторым КОР выходами блока 9 команд, первый SBR и второй КОМ входы которого соединены соответственно с третьим SBR и четвертым КОМ входами элементарного процессора, первый знакоразрядный выход Z и второй выход ОТК блока 8 умножения (суммирования) соединены соответственно с первым и вторым выходами процессора, третий выход Ах и четвертый выход Ау которого соединены соответственно с третьим Ах и четвертым Ау выходами блока 9 команд.

Первый Х и второй Y знакоразрядные входы блока 7 операндов (фиг.3) соединены с первым и вторым знакоразрядными входами блока 10, первый знакоразрядный выход А и второй выход MR2 которого соединены соответственно с первым и вторым входами регистра 11 синхронизации, выход Z которого соединен с первым знакоразрядным входом С1 выходного коммутатора 12, второй Х и третий Y знакоразрядные входы которого соединены с третьим XV и четвертым YV выходами входного блока 10, пятый, шестой, седьмой выходы которого соединены соответственно с первым, вторым, третьим входами блока 13 управления памятью, первый, второй, третий выходы которого соединены соответственно с первым, вторым, третьим входами блока 14 памяти, информационные входы Q которого соединены с выходами Q регистра 11, выходы блока 14 памяти соединены с информационными входами LCl-LC3p преобразователя 15 кода, первый управляющий вход PR которого соединен с четвертым выходом блока 13 управления памятью, третий вход КОР блока соединен с вторым управляющим входом КОР преобразователя 15 кода, первый знакоразрядный выход КС которого соединен с четвертым знакоразрядным входом КС выходного коммутатора 12, первый LX и второй LY знакоразрядные выходы которого являются первым и вторым выходами блока, третьим выходом которого является второй выход UP преобразователя 15 кода, четвертый вход Y0 блока соединен с первым входом автомата Мура 16 и четвертым входом блока 13 управления памятью, пятый выход СВ которого соединен с вторым входом автомата Мура 16, с первого по восьмой выходы которого соединены соответственно с пятого по двенадцатый входами выходного коммутатора 12, третий и четвертый входы автомата Мура 16 соединены соответственно с пятым и шестым выходами входного блока 10, с третьего по седьмой входы которого соединены соответственно с четвертого по восьмой выходами автомата Мура 16, с третьего по седьмой выходы которого соединены соответственно с пятого по девятый входами блока 13 управления памятью.

Первый Х знакоразрядный вход входного блока 10 (фиг.4) соединен с входами элемента И 17 и первыми входами элементов И-ИЛИ 19-21 и элементов И22-24, второй Y знакоразрядный вход блока соединен с входами элемента И 18 вторыми входами элементов И-ИЛИ 19-21 и первыми входами элементов И 25-27, третий вход ТХ блока соединен с третьими входами элементов И-ИЛИ 19-21 и первым входом элемента ИЛИ-И 28, четвертый вход TY блока соединен с первым входом элемента ИЛИ-И 29 и четвертыми входами элементов И-ИЛИ 19-21, выходы которых являются первым выходом А блока, выход элемента И 17 соединен с первыми входами элементов И31, 32, 35 и вторым входом элемента ИЛИ-И 28, выход элемента И 18 соединен с вторыми входами элементов ИЛИ-И 29, И31, 32 и И-ИЛИ35, выход которого является вторым выходом MR2 блока и соединен с первыми R входами триггеров 33, 34, вторые D входы которых соединены соответственно с выходами элементов И31 и И32, пятый вход блока соединен с третьим входом элемента ИЛИ-И28, шестой вход блока соединен с третьим входом элемента ИЛИ-И29, седьмой вход блока соединен с вторыми входами элементов И22-27, выходы которых являются третьим XV и четвертым YV выходами блока, выходы триггеров 33, 34 соединены с третьим и четвертым соответственно входами элемента И35, выходы элементов ИЛИ-И 28, 29 соединены с входом элемента ИЛИ 30, выход которого является пятым выходом MRA блока, выходы элементов И 17, И 18 являются соответственно шестым MRX и седьмым MRY выходами блока.

Первый вход MRA блока 13 управления памятью (фиг.5) соединен со счетным входом счетчика 36 адреса записи и первым входом элемента И37, второй MRX и третий MRY входы блока соединены соответственно с первым и вторым входами элемента И-ИЛИ 38, выход которого соединен с первым входом элемента И 39 и счетным входом счетчика 40 адреса чтения, вход R установки в ноль которого соединен с четвертым входом Y0 блока и с входом R установки в ноль счетчика 36, выход которого соединен с первым входом элемента И 42 и с первым входом А1 мультиплексора 41, выход которого является выходом А блока, пятый вход СР блока соединен с вторым входом элемента И 39 и вторым входом элемента И 37, выход которого соединен с вторым выходом WE блока и входом R триггера 43, третий выход ОЕ блока соединен с выходом элемента И 39 и входом D триггера 43, выход которого соединен с управляющим входом S мультиплексора 41, второй вход А2 которого соединен с выходом счетчика 40 и вторым входом элемента И 42, четвертый выход PR блока соединен с выходом элемента ИЛИ 44, с первого по третий входы которого соединены соответственно с выходами элементов И 45, И-ИЛИ 46, И 47, первый вход элемента И 47 соединен с выходом элемента И 42 и пятым выходом СВ блока, шестой вход ТХ которого соединен с первым входом элемента И-ИЛИ 46, второй вход которого соединен с первыми входами элементов И 45 и И-ИЛИ 48 и третьим входом блока MRY, третий вход элемента И-ИЛИ 46 соединен с вторыми входами элементов И 45 и И-ИЛИ 48 и вторым входом MRX блока, седьмой вход TY блока соединен с четвертым входом элемента И-ИЛИ 46, второй вход элемента И 47 соединен с выходом элемента И-ИЛИ 48, третий вход которого соединен с третьим входом И-ИЛИ 38 и с восьмым входом  блока, девятый вход

блока, девятый вход  которого соединен с четвертыми входами элементов И-ИЛИ 48 и 38.

которого соединен с четвертыми входами элементов И-ИЛИ 48 и 38.

Первый знакоразрядный вход А регистра 11 синхронизации (фиг.6) соединен с первым входом А первого разряда блока 49 разрядов регистра синхронизации, выход Z которого соединен с первым входом первого элемента ИЛИ блока 50, второй вход которого соединен с первым выходом Z второго разряда блока 49, второй выход Q каждого из разрядов блока 49 соединен с первым входом А следующего за ним разряда блока 49, все вторые входы MR2 разрядов блока 49 соединены с вторым входом MR2 регистра синхронизации, каждый первый выход Z разрядов блока 49, начиная со второго, соединен соответственно с вторым входом элементов ИЛИ, начиная с ИЛИ1 блока 50, выход каждого элемента ИЛИ блока 50 соединен с первым входом следующего за ним элемента ИЛИ, выход последнего элемента ИЛИр-1 блока 50 является выходом Z регистра синхронизации, выходы Q каждого из разрядов блока 49 являются параллельным выходом Q регистра синхронизации.

Знакоразрядный вход А разряда регистра синхронизации (фиг.7) соединен с входом ячейки 51, первый выход которой соединен с первыми входами элемента И52 и элемента И53, второй вход которого соединен с выходом элемента И54 и входом триггера 55, первый выход которого соединен с вторым входом элемента И52, выход которого является первым выходом Z разряда регистра синхронизации, второй выход ячейки 51 соединен с первым входом элемента И54, второй вход которого соединен с вторым входом MR2 разряда регистра синхронизации, второй выход триггера 55 соединен с третьим входом элемента И53, выход которого является вторым выходом Q разряда регистра синхронизации.

Знакоразрядный вход А ячейки регистра синхронизации (фиг.8) соединен с информационными входами триггеров 56-58, прямые выходы которых являются выходом В ячейки и соединены с входом элемента И59, выход которого является вторым выходом МР ячейки.

Информационные входы LCl-LC(3p) преобразователя кода 15 (фиг.9) соединены с информационными входами (С1-Ср) блоков 60, 61, 62 преобразователя так, что входы (С1-Ср) блока 60 соединены соответственно с входами LC1, LC4, LC7, . ..,LC(3p-2) преобразователя, входы С1-Ср блока 61 соединены соответственно с входами LC2, LC5, LC8,...,LC(3p-l) преобразователя, входы С1-Ср блока 62 соединены соответственно с входами LC3, LC6, LC9,...,LC(3p) преобразователя, вход PR преобразователя кода соединен с входом распределителя 63 тактовых импульсов, выходы Т1-Тр которого соединены с входами Т1-Тр блоков 60, 61, 62 преобразователя, выходы КС2, КС1, КС0 блоков 60, 61, 62 являются первым информационным выходом КС преобразователя, выходы Т1-Т15 распределителя 65 тактовых импульсов соединены с входами Т1-Т15 блока 64 кода операции, входы Um, SL/VC которого соединены с входом КОР преобразователя, выходы блока 64 являются вторым управляющим выходом преобразователя.

Информационные входы С1-Ср блока преобразователя кода КС (фиг.10) соединены соответственно с первыми и вторыми входами всех элементов И-ИЛИ блока 65, третьи и четвертые входы которых соединены соответственно с входами тактовых импульсов Т1-Тр блока, выходы элементов И-ИЛИ блока 65 соединены с входами элемента ИЛИ66, выход которого является выходом КС блока преобразователя кода.

Входы Т1-Т4 тактовых импульсов блока 64 кода операции (фиг.11) соединены с входами элемента ИЛИ 67, выход которого является первым выходом UP1 блока, первый вход элемента ИЛИ-И 68 соединен с входом КОР (Um) блока и с первыми входами элементов И-ИЛИ70, 71, 72, 73, 75, вторые входы элементов И-ИЛИ 70, 71, 72, 75 соединены с входом КОР (SL/VC) блока и с первыми входами элементов И 69, И-ИЛИ 74, второй вход элемента ИЛИ-И 68 соединен с входом Т 12 тактового импульса и с вторым входом элемента И-ИЛИ 73, третий вход которого соединен с входом Т 15 тактового импульса блока, вход Т 13 тактового импульса которого соединен с третьим входом элемента ИЛИ-И 68, четвертый вход которого соединен с третьим входом элемента И-ИЛИ 70 и с входом Т 14 тактового импульса блока, вход Т9 тактового импульса которого соединен с вторым входом элемента И69, выход которого соединен с первым входом элемента ИЛИ78, второй вход которого соединен с выходом элемента ИЛИ-И 68, выход элемента ИЛИ 78 является вторым UP2 выходом блока, четвертый вход элемента И-ИЛИ 70 соединен с третьими входами элементов И-ИЛИ 71, 72 и входом Т 10 тактового импульса блока, вход Т7 тактового импульса блока соединен с четвертым входом элемента И-ИЛИ 71 и третьим входом И-ИЛИ 75, четвертый вход которого соединен с входом Т11 тактового импульса блока и вторым входом элемента И-ИЛИ 74, третий вход которого соединен с входом Т8 тактового импульса блока, вход Т6 тактового импульса которого соединен с четвертым входом элемента И-ИЛИ 72, выходы элементов И-ИЛИ 70 и 71 соединены соответственно с третьим UP3 и четвертым UP4 выходами блока, выход элемента И-ИЛИ 73 соединен с входом триггера 76, прямой выход которого соединен с четвертым входом элемента И-ИЛИ 73 и первым входом элемента ИЛИ 79, второй вход которого соединен с прямым выходом триггера 77 и четвертым входом элемента И-ИЛИ 74, выход которого соединен с входом триггера 77, выходы элементов И-ИЛИ 72, ИЛИ 79, И-ИЛИ 75 являются пятым UP 5 выходом блока.

Знакоразрядный вход Х выходного коммутатора 14 (фиг.12) соединен с первыми входами элементов И80, 83, 86, знакоразрядный вход Y коммутатора соединен с первыми входами элементов И 89, 92, 95, знакоразрядный вход КС коммутатора соединен с первыми входами элементов И 82, 85, 88, 91, 94, 97, знакоразрядный вход С1 коммутатора соединен с первыми входами элементов И 81, 84, 87, 90, 93, 96, первый вход элемента И-ИЛИ 98 соединен с первым входом элемента И-ИЛИ102 и входом CN коммутатора, вход CR которого соединен с первыми входами элементов И-ИЛИ 99, 103, И 100, 104, второй вход И-ИЛИ 98 соединен с первыми входами элементов И 101, 105, вторым входом элемента И-ИЛИ 102 и входом СР коммутатора, вход ТХ которого соединен с вторым входом элемента И100, вход TY коммутатора соединен с вторыми входами элементов И-ИЛИ 99, 103, И104, третьи входы элементов И-ИЛИ 98, 102 соединены с входом TXY коммутатора, вход  которого соединен с четвертым входом элемента И-ИЛИ 98 и вторым входом И105, вход

которого соединен с четвертым входом элемента И-ИЛИ 98 и вторым входом И105, вход  коммутатора соединен с вторым входом элемента И 101 и четвертым входом И-ИЛИ 102, выход которого соединен с третьим входом элемента И-ИЛИ 103, выход элемента И-ИЛИ 98 соединен с третьим входом элемента И-ИЛИ 99, выход которого соединен с вторыми входами элементов И80, 83, 86, выход элемента И100 соединен с вторыми входами элементов И81, 84, 87, выход элемента И101 соединен с вторыми входами элементов И82, 85, 88, выход элемента 103 соединен с вторыми входами элементов И89, 92, 95, выход элемента И104 соединен с вторыми входами элементов И90, 93, 96, выход элемента И105 соединен с вторыми входами элементов И91, 94, 97, выходы элементов И80, 81, 82 соединены с входами элемента ИЛИ106, выход которого соединен с входом триггера 112, выходы элементов И 83, 84,85 соединены с входами элемента ИЛИ 107, выход которого соединен с входом триггера 113, выходы элементов И86, 87, 88 соединены с входами ИЛИ 108, выход которого соединен с входом триггера 114, выходы элементов И 89-91 соединены с входами элемента ИЛИ 109, выход которого соединен с входом триггера 115, выходы элементов И92-94 соединены с входом элемента ИЛИ 110, выход которого соединен с входом триггера 116, выходы элементов И95-97 соединены с входами элемента ИЛИ 111, выход которого соединен с входом триггера 117, выходы триггеров 112-114 являются первым выходом LX коммутатора, вторым выходом LY которого являются выходы триггеров 115-117.

коммутатора соединен с вторым входом элемента И 101 и четвертым входом И-ИЛИ 102, выход которого соединен с третьим входом элемента И-ИЛИ 103, выход элемента И-ИЛИ 98 соединен с третьим входом элемента И-ИЛИ 99, выход которого соединен с вторыми входами элементов И80, 83, 86, выход элемента И100 соединен с вторыми входами элементов И81, 84, 87, выход элемента И101 соединен с вторыми входами элементов И82, 85, 88, выход элемента 103 соединен с вторыми входами элементов И89, 92, 95, выход элемента И104 соединен с вторыми входами элементов И90, 93, 96, выход элемента И105 соединен с вторыми входами элементов И91, 94, 97, выходы элементов И80, 81, 82 соединены с входами элемента ИЛИ106, выход которого соединен с входом триггера 112, выходы элементов И 83, 84,85 соединены с входами элемента ИЛИ 107, выход которого соединен с входом триггера 113, выходы элементов И86, 87, 88 соединены с входами ИЛИ 108, выход которого соединен с входом триггера 114, выходы элементов И 89-91 соединены с входами элемента ИЛИ 109, выход которого соединен с входом триггера 115, выходы элементов И92-94 соединены с входом элемента ИЛИ 110, выход которого соединен с входом триггера 116, выходы элементов И95-97 соединены с входами элемента ИЛИ 111, выход которого соединен с входом триггера 117, выходы триггеров 112-114 являются первым выходом LX коммутатора, вторым выходом LY которого являются выходы триггеров 115-117.

Первый вход КОМ блока 9 команд (фиг.13) соединен с входом регистра 118 команд, первый и второй выходы которого соединены с первым и вторым входами элементов И 119 и неравнозначности 120, выходы которых являются первым выходом КОР блока, второй вход SBR которого соединен с первым входом элемента ИЛИ 121, второй вход которого соединен с третьим выходом регистра 118 команд, выход элемента ИЛИ 121 соединен с вторым выходом Y0 блока, третьим АХ и четвертым AY, выходами которого являются соответственно четвертый и пятый выходы регистра 118 команд.

Блок автомат Мура (фиг.14) содержит граф цифрового автомата Мура и его условное графическое обозначение (УГО).

Макропроцессор МАП включает в себя n процессоров, работающих в формате с плавающей запятой, где n=4÷256, и коммутатор (К), обеспечивающий соединение по полному графу п процессоров и m входных информационных каналов, по которым подаются входные операнды X. Соответственно, имеется n выходных информационных каналов результатов Z и n каналов настройки команд, обеспечивающих одновременную запись n команд в элементарные процессоры.

Функционально процессоры разделены на n/2 аддитивных ЭП и n/2 мультипликативных ПУ.

Структура макропроцессора реализована по принципу модульного наращивания и соответствующих секций коммутатора К.

Коммутатор предназначен для построения программируемых коммутационных систем на основе принципа коммутации каналов.

Операнды, поступающие на информационные входы X, представлены в последовательном знакоразрядном коде, в котором ведется обработка в операционном устройстве.

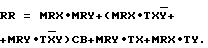

Для примера рассмотрим кодировку цифр четверичного знакоразрядного кода и маркера числа, представленные в табл.1.

Как видно из данных таблицы, для представления каждой цифры требуется три двоичных разряда. Это обусловливает последовательную передачу числовой информации в четверичном знакоразрядном коде по трем проводам. Каждая цифра может быть представлена как Хn(Х2Х1Х0), где Х2 - старший бит цифры.

Цифры входных операндов Х(Х1Х2...Хm) и результата Z(Z1Z2...Zn) для четверичного кода принимают значения (±1,±2,±3).

Работа макропроцессора начинается с загрузки команды в каждый процессор. Команда поступает на блок 9 команд ВК (фиг.2) и записывается в регистр 118 (фиг. 13). Команда содержит два разряда кода операции, разряд начальной синхронизации NC и два адреса Ах и Ау, разрядность которых определяется как f=] log2(n+m)[. Команда дешифрируется: код операции выдается как операция умножения для ПУ и операция сложения/вычитания для ПС и поступает на вход КОР ВО, NC - начальная установка совместно с начальным сбросом SBR образуют сигнал "установка в 0" и поступает на вход Y0 ВО. Адреса, по которым выбираются операнды в процессорах по входам Х и Y, поступают на входы А1-А2n коммутатора 2. В соответствии с адресом, поступившим из ВК каждого процессора, в коммутаторе 2 коммутируется связь поступления операндов с входа коммутатора на входы Х и Y каждого процессора. В процессорах операнды поступают на вход блока 7 операндов.

Блок операндов ВО (фиг.3) служит для синхронизации рассогласованных потоков операндов с помощью памяти, в которой накапливаются опережающие операнды. Рассогласование операндов на входах Х и Y процессоров возникает за счет того, что операнды могут быть результатом вычислений на различных по длине цепочках процессоров, каждый из которых обладает операционной задержкой.

В ВО используются три режима синхронизации:

- синхронизация операндов начальная - CN;

- синхронизация операндов на регистре синхронизации - CR;

- синхронизация операндов на буферной памяти - СР.

Для синхронных операндов блок работает в режиме CN. В этом случае операнды с выхода входного блока 10 ВL поступают на выходной коммутатор КО.

При величине рассинхронизации, меньшей длины Р операндов, ВО работает в режиме CR (Р лежит в пределах 16-32). Опережающий операнд задерживается в регистре синхронизации до прихода запаздывающего операнда, откуда поступает на выходной коммутатор КО синхронно с запаздывающим операндом.

При рассинхронизации на величину, большую длины Р операнда, ВО работает в режиме с памятью СР. Опережающий операнд в этом случае задерживается в блоке памяти, откуда синхронно с запаздывающим операндом подается на выходной коммутатор через преобразователь кода BF.

Синхронизация операндов, поступающих на вход ВО, осуществляется следующим образом. Во входном блоке 10 вырабатываются маркеры MRX и MRY обоих операндов по мере их поступления, которые поступают на вход блока 16 автомата Мура. Здесь в соответствии с очередностью поступления маркеров MRX и MRY и по состоянию памяти - свободная СВ или занято  вырабатываются режимы работы ВО - CN, CR, СР и сигналы, свидетельствующие об очередности поступления операндов TXY - оба операнда поступили одновременно, ТХ - операнд Х поступил первым и находится в регистре синхронизации,

вырабатываются режимы работы ВО - CN, CR, СР и сигналы, свидетельствующие об очередности поступления операндов TXY - оба операнда поступили одновременно, ТХ - операнд Х поступил первым и находится в регистре синхронизации,  - операнд Х поступает в память при отсутствии операнда Y,

- операнд Х поступает в память при отсутствии операнда Y,  - операнд Y поступает в память при отсутствии Х и TY - операнд Y поступил первым и находится в регистре сихронизации. В соответствии с этими сигналами во входном блоке 10 вырабатываются сигналы MRA - маркер опережающего операнда, MR2 - маркер запаздывающего операнда. В случае, если операнды пришли одновременно, по сигналу TXY на выход выдаются операнды XV, YV, с приходом одного из операндов вырабатывается опережающий операнд А, который поступает на регистр 11 синхронизации RS. Регистр синхронизации (фиг.6) представляет собой сдвиговый регистр, по которому цифра за цифрой продвигается опережающий операнд. Разряд регистра (фиг.7) содержит ячейку СН, представляющую собой три триггера (фиг. 8), в которую записывается очередная цифра операнда, и триггер 55, который управляет продвижением операнда по регистру. До прихода запаздывающего операнда цифры опережающего операнда продвигаются по разрядам регистра с выхода Q каждого разряда на вход А каждого последующего разряда. В случае прихода маркера MR2 запаздывающего операнда в каждом разряде регистра (фиг. 7) на элементе И 54 осуществляется опрос на совпадение маркеров обоих операндов. В случае совпадения триггер 55 устанавливается в единичное состояние и прерывает дальнейшее продвижение цифр опережающего операнда по выходу Q регистра. Открывается путь следования операнда через элемент И 52 на выход Z. Все выходы Z разрядов (фиг.6) через элементы ИЛИ блока 50 подсоединены к выходу Z регистра. Следовательно, при появлении запаздывающего операнда опережающий операнд может быть подан на выход Z регистра с любого разряда. Опережающий операнд с регистра 11 синхронизации (фиг.3) с выхода Z поступает на вход С1 выходного коммутатора 12. А запаздывающий Х или Y операнд с входного блока 10 с выхода XV или YV поступает соответственно на вход Х или Y блока КО.

- операнд Y поступает в память при отсутствии Х и TY - операнд Y поступил первым и находится в регистре сихронизации. В соответствии с этими сигналами во входном блоке 10 вырабатываются сигналы MRA - маркер опережающего операнда, MR2 - маркер запаздывающего операнда. В случае, если операнды пришли одновременно, по сигналу TXY на выход выдаются операнды XV, YV, с приходом одного из операндов вырабатывается опережающий операнд А, который поступает на регистр 11 синхронизации RS. Регистр синхронизации (фиг.6) представляет собой сдвиговый регистр, по которому цифра за цифрой продвигается опережающий операнд. Разряд регистра (фиг.7) содержит ячейку СН, представляющую собой три триггера (фиг. 8), в которую записывается очередная цифра операнда, и триггер 55, который управляет продвижением операнда по регистру. До прихода запаздывающего операнда цифры опережающего операнда продвигаются по разрядам регистра с выхода Q каждого разряда на вход А каждого последующего разряда. В случае прихода маркера MR2 запаздывающего операнда в каждом разряде регистра (фиг. 7) на элементе И 54 осуществляется опрос на совпадение маркеров обоих операндов. В случае совпадения триггер 55 устанавливается в единичное состояние и прерывает дальнейшее продвижение цифр опережающего операнда по выходу Q регистра. Открывается путь следования операнда через элемент И 52 на выход Z. Все выходы Z разрядов (фиг.6) через элементы ИЛИ блока 50 подсоединены к выходу Z регистра. Следовательно, при появлении запаздывающего операнда опережающий операнд может быть подан на выход Z регистра с любого разряда. Опережающий операнд с регистра 11 синхронизации (фиг.3) с выхода Z поступает на вход С1 выходного коммутатора 12. А запаздывающий Х или Y операнд с входного блока 10 с выхода XV или YV поступает соответственно на вход Х или Y блока КО.

Если запаздывающий операнд задерживается более, чем на длину операнда, то опережающий операнд с выхода Q регистра синхронизации записывается в блок 14 памяти. Осуществляется это следующим образом.

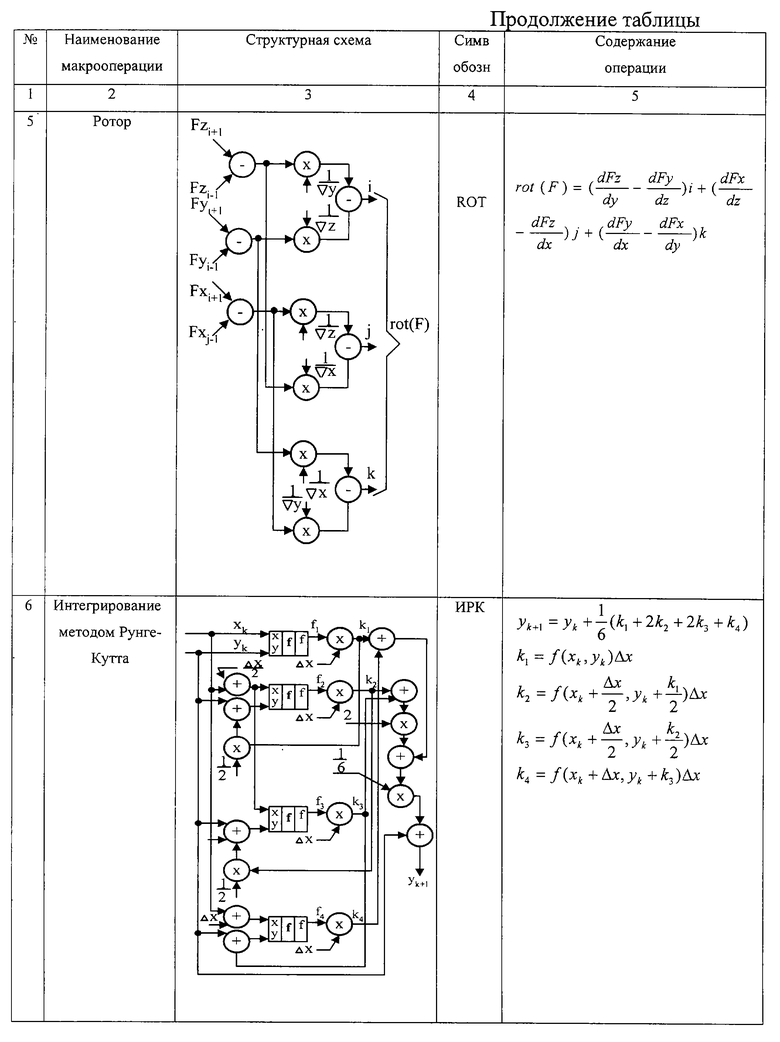

Блок 13 управления памятью BUP (фиг.5) осуществляет запись и чтение операндов блока 14 памяти. В режиме синхронизации с памятью СР с приходом маркера MRA опережающего операнда счетчик 36 записи вырабатывает очередной адрес AWE записи операнда, поступающего с RS в память, и вырабатывается сигнал записи WE. С приходом маркера запаздывающего операнда с помощью элемента И-ИЛИ 38 на счетчике 40 чтения СrОЕ вырабатывается адрес АОЕ чтения из памяти соответствующего операнда. Мультиплексор 41 пропускает адрес AWE записи или адрес АОЕ чтения с помощью триггера 43 в зависимости от наличия сигнала соответственно записи WE или чтения ОЕ. Разрядность Q адресов AWE и АОЕ определяется как q=]log2L[, где L - объем памяти. Сигнал свободная память СВ вырабатывается на элементе И42 в случае, если оба счетчика записи и чтения находятся в нулевом состоянии. Сигнал пуск распределителя PR вырабатывается на элементах 44-48 в соответствии с логическим выражением:

Блок 14 памяти осуществляет запись операндов, поступающих с RS, при появлении сигнала записи WE по соответствующему адресу А. При наличии сигнала ОЕ чтения и соответствующего адреса А осуществляется чтение операнда из памяти, который поступает на вход преобразователя 15 кода BF параллельным кодом, причем, все цифры, а в данном случае рассматривается четверичная кодировка, когда цифра представлена тремя битами, вытянуты в одну цепочку. Следовательно, при длине входного операнда, равной Р, на выходе блока памяти будет операнд длиной 3Р. Цель преобразователя кода BF состоит в преобразовании параллельного входного операнда LCl-LC3p в последовательный четверичный код, когда на выход блока в каждом такте поступает четверичная цифра числа. Следовательно, для считывания всех цифр операнда потребуется Р тактов.

Преобразователь 15 кода (фиг.9) содержит три блока 60-62 преобразователя кода КС (фиг.10) и распределитель 63 тактовых импульсов. Поступающий на вход преобразователя последовательный операнд записывается в три блока КС таким образом, что первая цифра LC1-LC3 записывается на первые входы С1 каждого из трех блоков КС, вторая цифра LC4-LC6 - на входы С2 трех блоков КС и т.д., так, в результате оказывается, что все старшие биты всех цифр операнда расположены в блоке 60 КС, вторые биты - в блоке 61 КС и третьи, младшие, расположены в блоке 62 КС. По сигналу ПУСК распределителя PR осуществляется запуск распределителя 63 тактовых импульсов. Распределенные такты поступают на входы каждого из блоков КС и считывают последовательно цифры входного операнда. По Т1 считывается первая цифра в виде трех битов, поступающих на выход КС преобразователя с выходов КС2, КС1, КС0, по Т2 - вторая цифра и т. д. до Р-ой цифры. Считывание битов цифр показано на блоке КС (фиг.10). С выхода КС преобразователя цифры поступают на вход КС выходного преобразователя.

В блоке 64 кода операции в соответствии с кодом операции Um умножения или SL/VC сложения/вычитания по распределенным тактам вырабатываются управляющие сигналы UP для работы блоков умножения BU и сложения BS (фиг.11).

Таким образом, в каждом ЭП с выходов блоков операндов на входы Х и Y блока BU (BS) поступают синхронно оба операнда и управляющие сигналы UP, сформированные в соответствии с заданным кодом операции. В блоках операнды обрабатываются, и результаты вычисления поступают на выходы Z процессоров и далее на выходы МАП и на входы коммутатора. Так осуществляется обработка потока операндов, поступающего на входы МАП.

Блоки заявляемого устройства могут быть реализованы средствами вычислительной техники отечественного производства. Так, в качестве блока умножения BU в процессоре используется устройство умножения, описанное в патенте 2148270 на изобретение от 27.05.98 г., опубликованное в Бюл. 12 от 27.04.2000 г. , в качестве блока суммирования BS в процессоре используется суммирующее устройство, описанное в патенте 2069009 от 10.11.96 г., опубликованное в Бюл. 31 от 10.11.96 г., в качестве коммутатора может быть использован матричный коммутатор, описанный в патенте 2103729 на изобретение от 05.08.94 г., опубликованное в Бюл. 3 от 27.01.98 г.

Блок автомата Мура - это стандартный блок, схемная реализация которого в соответствии с представленным графом на фиг.14 может быть реализована на элементах серии 1531, 1533, 1554.

Остальные блоки устройства, в том числе и коммутатор, могут быть также реализованы на элементах серий 1531, 1533, 1554.

Введение в устройство процессоров, обрабатывающих информацию в знакоразрядном коде и соединенных соответствующим образом, позволяет, во-первых, обеспечить высокую реальную производительность при решении широкого класса задач и обеспечивает для сильносвязанных задач производительность, максимально приближенную к пиковой.

Во-вторых, использование процессоров, состоящих из блоков умножения, блоков суммирования, каждый из которых содержит блоки операндов для синхронизации поступающих на входы операндов, и блоков команд, упрощает программирование, вследствие того, что автоматически решается проблема синхронизации данных (программисту не требуется решать эту проблему).

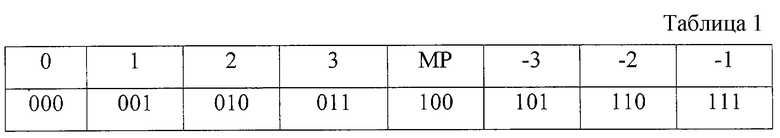

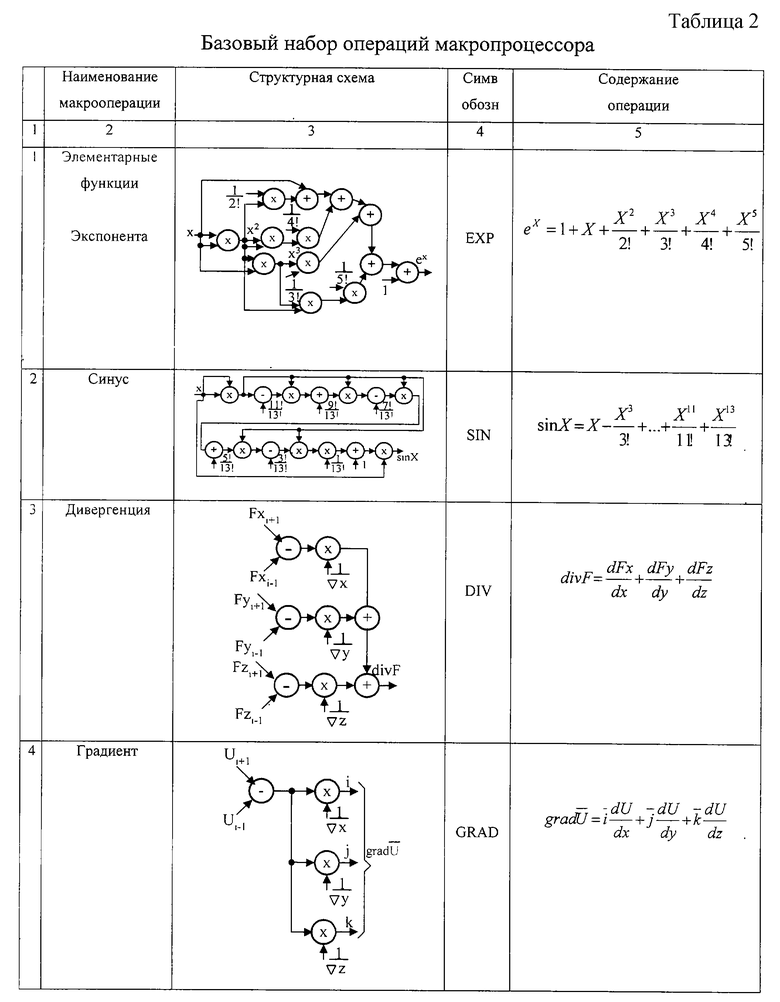

В-третьих, структура МАП позволяет реализовать в рамках универсальной вычислительной системы различные вычислительные структуры, эффективно реализующие крупные математические операции различных проблемных областей, таких как экспонента, синус, дивергенция, градиент, интеграл, фильтр, комплексное умножение и др. (см. табл.2), в результате чего пользователь имеет возможность вызывать крупные математические операции, т.е. реализовать программирование задач на более высоком уровне.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| МАТРИЧНЫЙ КОММУТАТОР | 1994 |

|

RU2103729C1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЕННОЙ ПАМЯТИ | 2001 |

|

RU2210804C2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| Микропроцессор | 1989 |

|

SU1756897A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в том, что обработка информации и обмен информацией осуществляются согласованно. Устройство содержит группу процессоров и коммутатор, причем процессоры реализуются в двух вариантах: процессор сложения, содержащий блок операндов, блок команд и блок сложения в знакоразрядном коде; и процессор умножения, содержащий блок операндов, блок команд и блок умножения в знакоразрядном коде. 2 табл., 14 ил.

Макропроцессор, предназначенный для построения многопроцессорных систем, содержащий группу процессоров и коммутатор, соединяющий входы и выходы процессоров, а также внешние входы и выходы макропроцессора по полному графу, отличающийся тем, что обработка информации в процессорах макропроцессора осуществляется в последовательном знакоразрядном коде, обеспечивающем согласование темпа обработки и темпа передачи данных, при этом процессоры макропроцессора реализуются в двух вариантах: процессор сложения, содержащий блок операндов, блок команд и блок сложения в знакоразрядном коде; и процессор умножения, содержащий блок операндов, блок команд и блок умножения в знакоразрядном коде, причем информационные знакоразрядные входы макропроцессора подключены к первым входам коммутатора, выходы которого соединены с первыми и вторыми информационными знакоразрядными входами процессоров, третьи входы которых соединены с вторыми входами макропроцессора, первые выходы процессоров являются выходами результатов макропроцессора и соединены с вторыми входами коммутатора, третьи входы которого соединены с вторыми выходами процессоров, третьи выходы которых являются выходами сигнала отказа макропроцессора.

| Вычислительные процессы и системы/ Под ред | |||

| Г.И.Марчука | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| - М.: Наука, Главная редакция физико-математической литературы, 1990 | |||

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| US 5903771 A, 11.05.1999 | |||

| DE 3545923 A1, 17.07.1986. | |||

Даты

2003-08-20—Публикация

2001-01-05—Подача