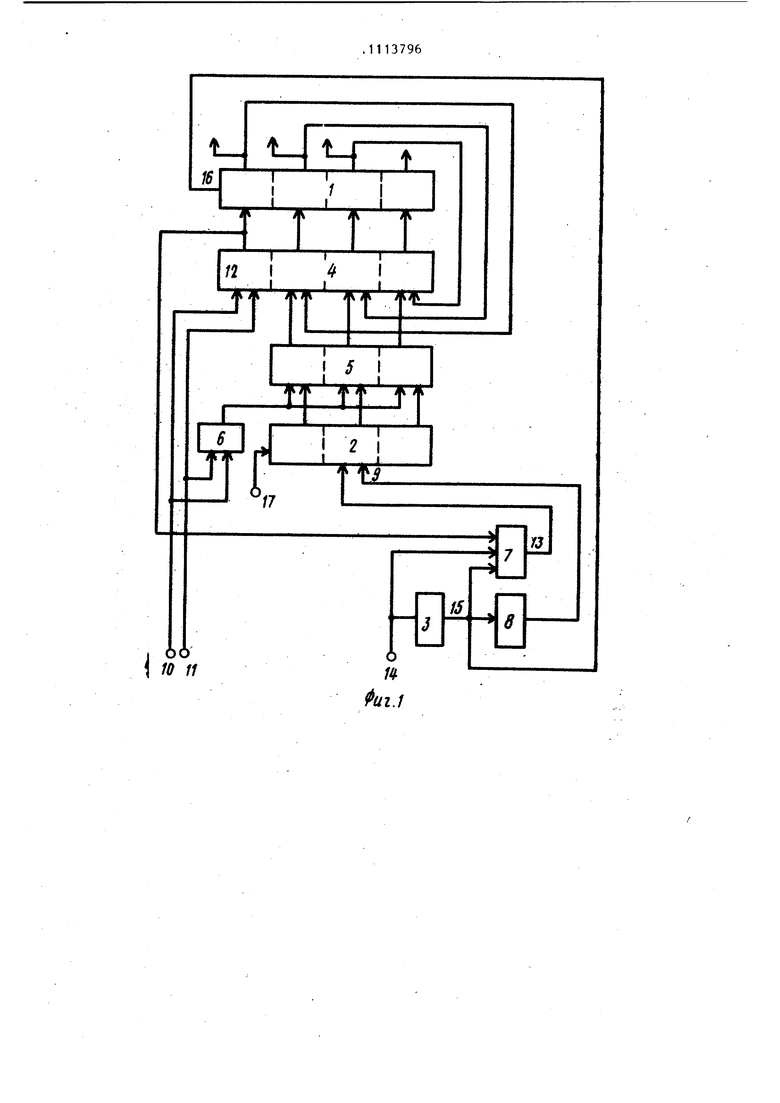

111 Изобретение относится к цифровой вычислительной технике и может быть использовано в управляющих, моделирующих и вычислительных Машинах и устройствах, работающих в знакоразрядной системе счисления с основаниями 1, О, 1. Известно устройство для перевода чисел из знакоразрядного кода в обычную систему счисления, содержащее ступени шифраторов ц. Недостаток известного устройства низкое быстродействие, определяемое последовательным распространением сиг нала заема. Наиболее близким по технической сущности к предлагаемому является устройство для преобразования из знакоразрядного кода в дополнительньй двоичный код, содержащее два регистра, элемент задержки, причем преобразование осуществляется путем заполнения двух регистров соответственно положительными и отрицательными разрядами избыточного числа и получения дополнительного кода их разности на вькодах сумматора 23. Недостатки этого устройства - низкое быстродействие и сложность оборудования. Низкое быстродействие обус ловлено тем, что на первом этапе преобразования осуществляется заполнение регистров последовательно посту пакицими разрядами числа, а на второмвычитание параллельных кодов и формирование результата на выходе устройства. Сложность оборудования обусловлена необходимостью применения параллельного сумматора для объединения положительной и отрицательной частей избыточного кода в одно двоичное число. Целью изобретения является увеличение быстродействия и упрощение оборудования. Поставленная цель достигается тем, что в преобразователь последовательного знакоразрядного кода в допол нительный двоичный код, содержащий первый и второй регистры и элемент задержки, вход которого соединен с тактовым входом преобразователя, а выход элемента задержки соединен с тактовым входом первого регистра, введены ;группа элементов НЕРАВНОЗНАЧНОСТЬ, группа элементов И, элемент запрета, элемент И и элемент НЕ, выход которого соединен с тактовым входом второго 6 регистра, выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с выходом элемента запрета, запрещающий вход которого соединен с входом отрицательных значений разрядов преобразователя и с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ группы, второй вход которого соединен с входом положительных значений разрядов преобразователя и с разрешающим входом элемента запрета, а выход перво-, го элемента НЕРАВНОЗНАЧНОСТЬ группы соединен с первым входом элемента И, выход которого соединен с входом сброса второго регистра, информационный вход которого соединен с входом единицы преобразователя, выходы которого являются выходами йервого регистра, информационные входы которого соответственно соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ группы, первый вход i -го элемента которой , где И - число разрядов входного кода) соединен с выходом (t-D-ro элемента И группы, а второй вход i-го элемента НЕРАВНОЗНАЧНОСТЬ группы соединен с выходом (i-1)-ro разряда первого регистра, тактовый вход которого соединен с выходом элемента задержки, входом элемента НЕ и вторым входом элемента И, третий вход которого соединен с тактовым входом преобразователя. На фиг.1 изображена блок-схема предлагаемого преобразователя последовательного знакоразрядного кода в дополнительный двоичный код, на фиг.2 - временные диаграммы, иллюстрирующие работу преобразователя. Предлагаемый преобразователь содержит первый регистр 1 и второй регистр 2, элемент задержки 3, группу элементов НЕРАВНОЗНАЧНОСТЬ 4, группу элементов И 5, элемент запрета 6, элемент И 7 и элемент НЕ 8, выход которого соединен с тактовым входом 9 второго регистра. Вход отрицательных разрядов 10 и вход положительных разрядов 11 преобразователя соединены с входами первого элемента НЕРАВНОЗНАЧНОСТЬ 12 группы. Вход сброса второго регистра соединен с выходом 13 элемента И 7. Тактовый вход 14 преобразователя и выход 15 элемента задержки соединены с входами элемента И 7. Тактовый вход 16 первого регистра соединен с вьпсодом 15 элемен31та задержки 3. Вход единицы 17 преобразователя соединен с входом первого разряда второго регистра 2. Предлагаемый преобразователь реализует вариант преобразования, позво лякиций формировать дополнительный код числа по мере получения его знакоразрядного представления, не затра чивая дополнительного времени на сум мирование после приема информации в регистры. При наличии знакоразрядного представления числа (старшие разряды чис ла находятся слева) для получения дополнительного двоичного кода достаточно в исходном коде дописать еле ва ноль в дополнительном разряде, а затем над разрядами, стоящими левее каждой отрицательной единицы, до любой ближайшей единицы включительно, выполнить инверсные преобразования, а над остальными - прямые преобразования согласно табл.1. Таблица 1 64 довательно формировать области инверсного преобразования по мере запол нения регистра 1 разрядами, причем с поступлением отрицательной цифры 1 осуществляется инверсное преобразование текущей области разрядов и фиксируется начало следующей области. При поступлении положительной цифры 1 инверсное преобразование текущей области не осуществляется, но так же, как и при отрицательной цифре 1, осуществляется фиксация начала новой области инверсного преобразования. Кодировка цифр 1,0,1 знакоразрядного кода осуществляется отрицательными разрядами S и положительными разрядами S входного числа в соответствии с табл.2. Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 1990 |

|

RU2022337C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД, содердащий первый и второй регистры и элемент задержки, вход которого соединен с тактовым входом преобраэователя, a выход элемента задержки соединен с тактовым входом первого регистра, отличающийся тем, что, с целью повьшения быстродействия, в него введены группа элементов НЕРАВНОЗНАЧНОСТЬ, группа элементов И, элемент запрета, элемент И и элемент НЕ, выход которого соединен с тактовым входом второго регистра, выходы которого соединены с первыми входами элементов И группы, вторые входы ко.торых соединены с выходом элемента запрета, запрещающий вход которого соединен с входом отрицательных значений разрядов преобразователя и с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ группы, второй вход которого соединен с входом положительных значений раарядов преобразователя и с разрешающим входом элемента запрета, a выход первого элемента НЕРАВНОЗНАЧНОСТЬ группы соединен с первым входом элемента И, выход которого соединен с входом сброса второго регистра, информационный вход которого соединен с входом единицы преобразователя, выходы которого являются выходами первого ре- /Л гистра, информационные входы которого соответственно соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ группы, первый вход i -ffo элемента которой

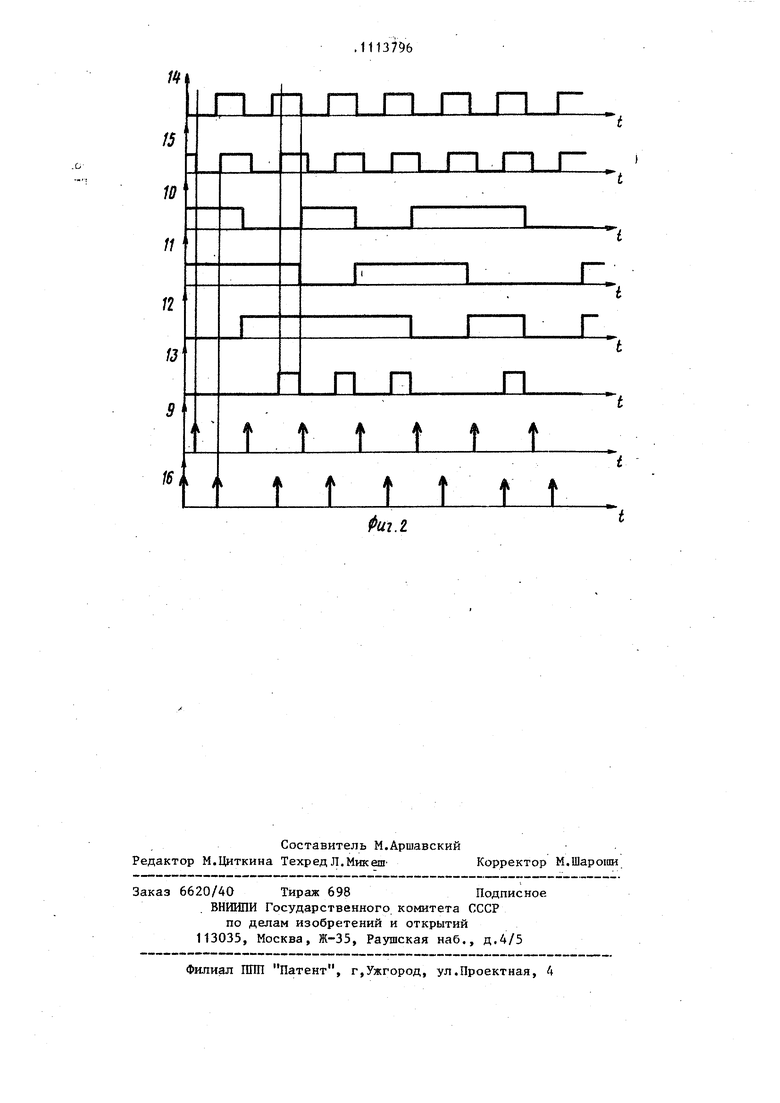

Полученное представление дополнительным кодом исходно Пример. Дополните разр Исходное 00100111010 число Области инверсного преобразованияДополнительный110111101100 код При последовательном пост знакоразрядного кода, начина старших разрядов, необходимо Работа предлагаемого преобразователя иллюстрируется эпюрами, представленными на фиг.2. Номера слева от зпюр соответствуют номерам позиций на фиг.1, в которых рассматриваются соответствующие напряжения. На входы 10 и 11 устройства поступают разряды S и S соответственно (зпюры 10 и t1 на фиг.2), синхронизированные частотой { на тактовом входе 14 устройства (эпюра 14). На выходе 15 элемента задержки 3 формируется задержанная серия -f j (эпюра 15), управлякицая занесением информации в первый регистр 1 непосредственно, а во второй регистр 2 - через элемент НЕ 8. Так как занесение в оба регистра осуществляется по положительному фронту импульсов на тактовом входе, то включением элемента НЕ 8 достигается занесение инфорнации сигнала сначала во второй ретистр 2, затем в первый регистр 1. Сигналы занесения информации в регистры 1 и 2 показаны на эпюрах 16 и 9 соответственно. 11 Первый 4гистр 1 осуществляет запись и хранение информации, содержащейся на выходах группы элементов НЕРАВНОЗНАЧНОСТЬ 4. Совокупность первого регистра 1 и группы элементов НЕРАВНОЗНАЧНОСТЬ А образует сдвиговый последовательный регистр с возможностью записи прямых либо инверсных значений сдвигаемых разрядрв. Второй регистр 2 является последо вательным сдвиговым регистром, заполняемым цифрами 1, поступающими с входа единицы преобразователя на информационный вход второго регистра 2. Обнуление второго регистра (эпюра 13) осуществляется элементом И 7 в конце такта после занесения информации в первый регистр при наличии 1 или Т в текущем разряде преобразуемого слова. В итоге второй регистр 2 представляет собой регистр-маску, количество возбужденных разрядов которого в момент поступления цифры Т соответствует щирине области инверс- кого преобразования. Признак инверсного преобразований формируется элементом ЗАПРЕТ 6, сигнал с выхода которого разрешает прохождение содер. жимого второго регистра 2 через груп-30 На пу элементов И 5 на группу элементов НЕРАВНОЗНАЧНОСТЬ 4. Первый элемент НЕРАВНОЗНАЧНОСТЬ группы 4 обоими входами соединен с входами отрицательных 10 и положительных 11 разрядов устройства и осуществляет формирование модуля цифры (прямое преобразование по табл.1, эпюра 12). Разрядность второго регистра 2 и группы элементов 5 равна количеству цифр преобразуемого избыточного знакоразрядного числа без учета дополнительного разряда, а разрядность первого регистра 1 и группы элементов НЕРАВНОЗНАЧНОСТЬ 4 64 на единицу больше, т.е. с учетом дополнительного разряда, который должен в виде кода О поступать первым по входам 9 и 10. Дополнительный код преобразуемого числа формируется на выходах первого регистра 1, являющихся выходами устройства. Быстродействие предлагаемого устройства при одинаковых тактовых частотах выше быстродействия устройства-прототипа на величину времени выполнения операции вычитания в параллельном сумматоре, так как дополнительный код появляется на выходе первого регистра 1 не позже такта по--, ступления последней .цифры преобразуемого знакоразрядного числа. Для сравнения затрат оборудования необходимо принять во внимание сложность в прототипе П -разрядного параллельного сумматора, с одной стороны, и, с другой стороны, сложность в предлагаемом устройстве совокупности элемента И 7, элемента НЕ 8, эле- мента ЗАПРЕТ 6, ,П Разрядной группы элементов И 5, , С + О-разрядной группы элементов НЕРАВНОЗНАЧНОСТЬ 4 и одного разряда первого регистра 1. элементах типа, ЭСЛ при интегральном исполнении на каждый разряд сумматора требуется 108 вентилей (серия 100ИМ180), т.е. всего 108п вентилей. На каждый элемент- НЕРАВНОЗНАЧНОСТЬ требуется 22 вентиля, т.е. на группу 4-22 (п+1) вентиль. На группу элементов 5 необходимо 14 П вентилей, а на все оставшиеся элементы - еще дополнительно вентилей, т.е. все (ЗбП+102) вентиля. Следовательно, предлагаемое устройство проще на (72П-102) вентиля, что при разрядности и , например, равной 32 разрядам, составляет 2200 вентилей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| A.Avizienis Binary compatible signeddigit arithmetic AF/PS Conf | |||

| Proc | |||

| V | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Рельсовое скрепление | 1923 |

|

SU663A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| A.Avizienis Arythmetic Microsystems for the Synthesis of function generators Proceedings of the IEEE, V | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Прибор для подогрева воздуха отработавшими газам и двигателя | 1921 |

|

SU320A1 |

Авторы

Даты

1984-09-15—Публикация

1983-06-30—Подача