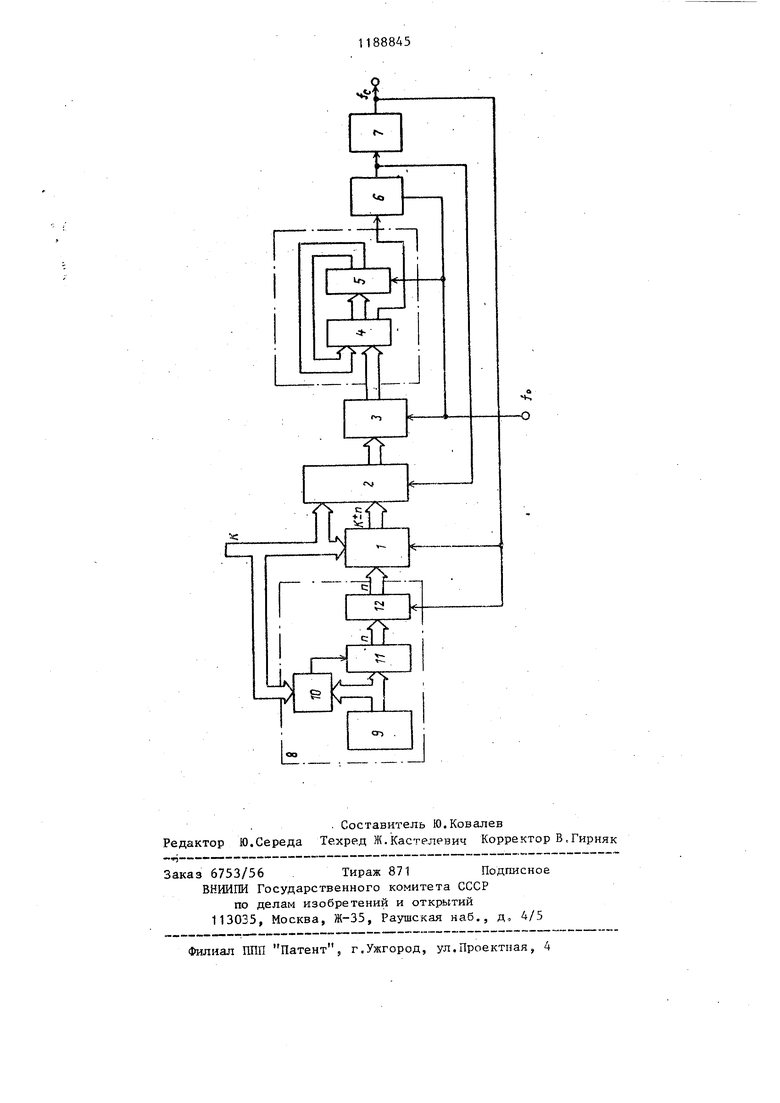

Изобретение относится к радиоте-хнике и может использоваться для формирования сетки частот в радиопередающих и радиоприемных устройствах, а также в устройствах синхрониэации. Цель изобретения - уменьшение уро вня дискретных побочных составляющих в спектре выходного сигнала. На чертеже изображена структурная электрическая схема предлагаемого цифрового синтезатора частот. Цифровой синтезатор частот содержит первый сумматор 1, мультиплексор 2, первый регистр 3 памяти, второй сумматор 4, второй регистр 5 памяти, третий регистр 6 памяти, делитель 7 частоты на два, формирователь 8 кода. При этом формирователь 8 кода содержит генератор 9 случайных чисел, компаратор 10, блок 11 ключей, четвертый регистр 12 .памяти Цифровой синтезатор частоты работает следующим образом. Компаратор 10 сравнивает число К - код синтезируемой частоты с числом N , вырабатьшаемым генератором 9, и открывает блок 11 ключей для прохождения на вход четвертого регистра 12 только тех случайных чисел п из множества чисел N,которые меньше или равны К (п К). По выход ным импульсам цифрового синтезатора частот, поступающим на вход синхронизации четвертого регистра 12, числа п записываются в четвертый регистр 12, В результате этого для каждого нового периода выходной частоты на выходе формирователя 8 кода формируется новое случайное число п k. Режим работы первого сумматора 1 (сложение или вычитание) задается выходньм сигналом с делителя 7 частоты. В положительный полупериод выходного сигнала делителя 7 частоты на выходе первого сумматора 1 формируется код числа К + п, а в отрицательный полупериод - код числа К - п. Таким образом, на первый и второй входы мультиплексора 2 непрерывно поступают коды чисел К ± п .и К. Пока сигнал переноса первого суммато ра 1 равен нулю, на управляющий вход мультиплексора 2 в каждый такт работы цифрового накопителя, выполненног в виде второго сумматора 4 и второго регистра 5, будет поступать нуль, и на выход мультиплексора 2 пропускается код числа К, который по тактовым импульсам записывается в первый регистр 3. Код числа К суммируется во втором сумматоре 4 с выходным кодом второго регистра 5, код суммы подается на вход второго регистра 5, и следующим тактовым импульсом записывается во второй регистр 5. В результате этого во втором регистре 5 с тактовой частотой f происходит накопление кода числа, поступающего с выхода первого регистра 3. Когда значение суммы на выходе второго сумматора 4 достигает или превышает величину емкости Р второго регистра 5, во втором сумматоре 4 образуется остаток L (О L К), а на выходе переноса второго сумматора появляется сигнал переноса, равный единице. В следующий такт работы в третий регистр 6- записывается единица переноса, а в первый регистр 3 код числа К, во второй регистр 5 - остаток второго сумматора 4, на выходе мультиплексора 2 в зависимости от знака полупериода выходного сигнала делителя 7 частоты пропускается либо код числа К + п, либо код числа К - п . На выходе второго сумматора 4 получается код числа К + п, а СИ1- нал переноса на выходе второго сумматора 4 становится равным нулю. Таким образом, емкость R цифрового накопителя после каждого переполнения изменяется относительно номинального значения R в различных полупериодах выходного синтезируемого колебания ( RQ п - в положительный полупериод, Rp - п - в отрицательный полупериод) по определенНому закону. Причем среднее значение емкости.равно номинальному, а поэтому средняя выходная частота импульсов переполнения, снимаемых с выхода третьего регистра 6, определяется по формуле f. После деления на два в делителе 7 частоты на выходе цифрового синтезатора частот формируется выходной импульсный сигнал типа меандр с частотой Если К кратно R V. , lu 111/1 лс каждого переполнения исходное значение остат3ка L сохраняется неизменным и требуемьй коэффициент преобразования будет реализован то частоты но. Если К не KpaCHo.Rp, то значения L после каждого переполнения изменя ются в пределах О - L f К, и требуе мый коэффициент преобразования частоты реализуется неточно, так как импульс переполнения формируется с некоторой временной погрешностью 4Т ) лежащей в интервале от О до /.. относительно его расположения в гипотемической импульсной пос ледовательности So(t) с периодом 45 I/P , что приводит к появлению диск/ п ретных побочных составляющих в спектре синтезируемого колебания; В предлагаемом цифровом синтезаторе частот за счет того, что емкость R цифрового накопителя изменяется относительно номинального значения RJ в различных полупериодах выходного колебания по определенному закону, происходит уменьшение уровня дискретных побочных составляющих благодаря увеличению их количества при неизменной суммарной мощности за счет случайного распределения импульсов сигнала помехи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1231570A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой накопитель (его варианты) | 1984 |

|

SU1261111A2 |

| Цифровой накопитель с дробной переменной емкостью | 1987 |

|

SU1481756A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Цифровой накопитель с дробной переменной емкостью | 1986 |

|

SU1374426A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197043A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

1. ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные первый сумматор, мульти.плексор, первый регистр памяти, второй сумматор и второй регистр памяти, поразрядные выходы которого подключены к второй группе входов второго сумматора, а также третий регистр памяти, сигнальный вход которого подключен к выходу переноса второго сумматора, тактовые входы первого, второго и третьего регистров памяти объединены и являются входом опорного сигнала цифрового синтезатора частот, первый вход первого сумматора объединен с вторым входом мультиплексора и является кодовым входом цифрового синтезатора частот, выход третьего регистра памяти подключен к управляющему входу мультиплексора. отличающийся тем, что, с целью уменьшения уровня дискретных побочных составляющих в спектре выходного сигнала, в него введены формирователь кода и делитель частоты на два, при этом выход формирователя кода подключен к второму входу первого сумматора, кодовый вход формирователя кода подключен к первому входу первого сумматора, вход синхронизации формирователя кода объединен с управляющим входом первого сумматора и подключен к выходу делителя частоты на два, вход которого соедиi нен с выходом третьего регистр.а памяти, 2. Синтезатор по п,1, о т л и ч аю щ и и с я тем, что формирователь кода содержит последовательно соединенные генератор случайных чисел, блок ключей и четвертый регистр памяти, а также компаратор, первый вход которого является кодовым входом 00 00 формирователя кода, второй вход компаратора подключен к выходу генератора случайных чисел и к входу блока оо 4 ключей, а выход компаратора соединен с управляющим входом блока ключей, сд выход и тактовый вход четвертого регистра памяти являются соответственно выходом и входом синхронизации формирователя кода.

| Патент США № 3882403, кл.328-14, 06.05.75 | |||

| Цифровой накопитель | 1982 |

|

SU1058069A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-10-30—Публикация

1984-03-29—Подача