Изобретение относится к вычислительной технике и технике связи и может быть применяться в системах цифровой связи, использующих сверточные коды.

Известен пороговый декодер сверточного кода, содержащий объединенные по входу кодер и корректор ошибок, а также анализатор синдрома, выходы которого через пороговый элемент и блок запрета коррекции подключены к входам корректора ошибок и анализатора синдрома (1).

Недостатком известного порогового декодера является низкая достоверность декодирования.

Наиболее близким по технической сущности к предлагаемому устройству является пороговый декодер сверточного кода, содержащий генератор тактовых импульсов, формирователь временного интервала, пороговый счетчик, первый и второй кодеры, корректор ошибок, первый и второй сумматоры по модулю два, первый и второй элементы ИЛИ, элемент "ЗАПРЕТ", формирователь синдрома, пороговый элемент, анализатор синдрома (2).

Недостатком известного устройства является низкая достоверность, обусловленная тем, что на основе анализа синдрома производится только обнаружение трехкратных ошибок, а не их исправление.

Цель предлагаемого изобретения состоит в повышении достоверности декодирования за счет исправления большей части трехкратных ошибок.

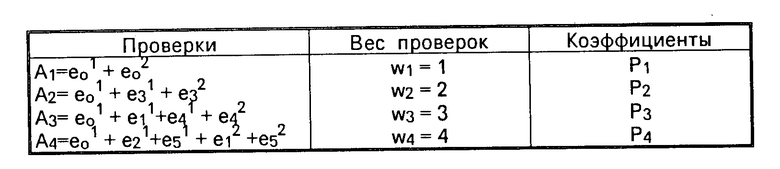

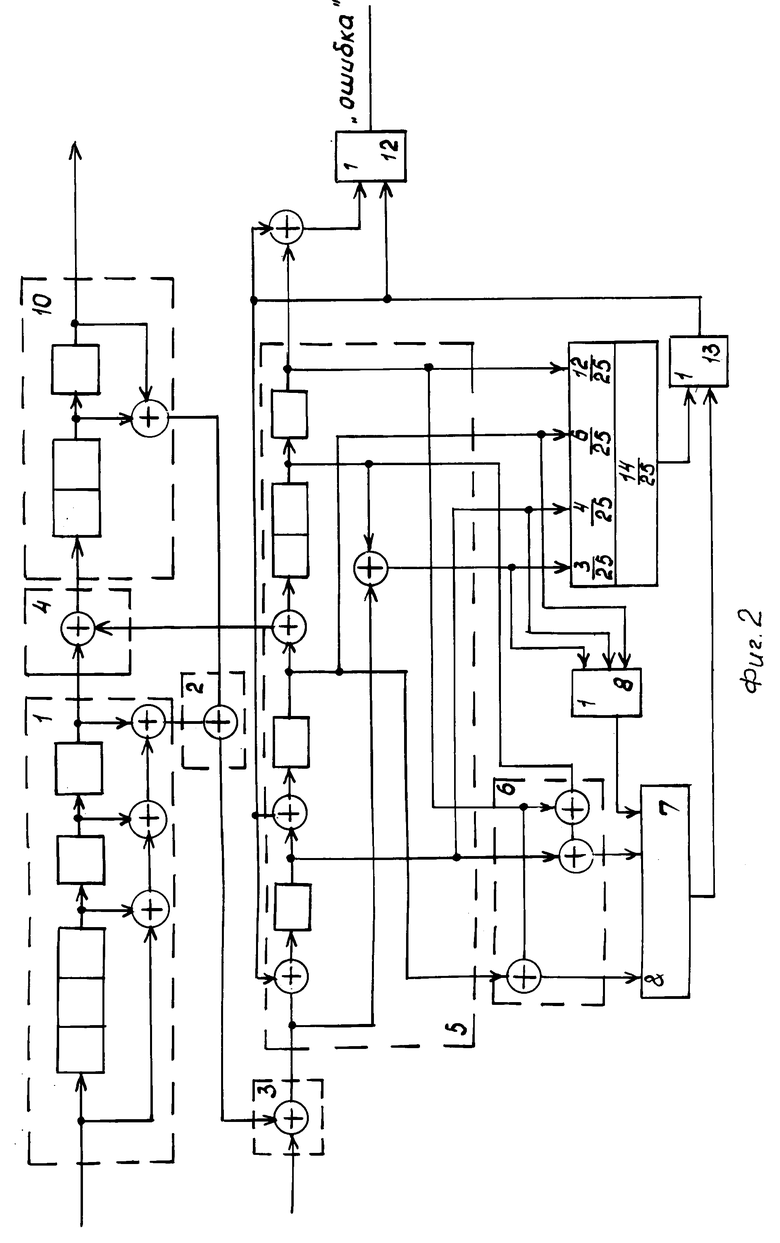

На фиг. 1 представлена структурная схема предлагаемого порогового декодера сверточного кода; на фиг. 2 - пример его конкретной реализации.

Пороговый декодер сверточного кода содержит (фиг. 1) первый кодер 1, первый сумматор по модулю два 2, формирователь 3 синдрома, корректор 4 ошибок, анализатор 5 синдрома, формирователь сигнала проверок, решающую схему 7, четвертый элемент ИЛИ 8, пороговый элемент 9, второй кодер 10, второй сумматор по модулю два 11, первый элемент ИЛИ 12, третий элемент ИЛИ 13, генератор тактовых импульсов 14, элемент "ЗАПРЕТ" 15, пороговый счетчик 16, формирователь временного интервала 17, второй элемент ИЛИ 18, блок 19 умножения на весовые коэффициенты.

Первый кодер 1 предназначен для формирования по информационным символам проверочной последовательности. В качестве первого кодера 1 используется регистр сдвига, связанный с сумматорами по модулю два. Первый выход первого кодера 1 соединен с первым входом корректора 4 ошибок, второй выход - с первым входом первого сумматора по модулю два 2.

Первый сумматор по модулю два 2 предназначен для формирования проверочной последовательности квазиортогонального сверточного кода. Первый вход соединен с вторым выходом первого кодера 1, второй вход - с вторым выходом второго кодера 10, а выход - с вторым входом формирователя синдрома 3.

Формирователь 3 синдрома служит для формирования синдромной последовательности из принятой проверочной последовательности и проверочной последовательности, сформированной на приемной стороне. В качестве формирователя синдрома используется сумматор по модулю два. Первый вход формирователя 3 синдрома является проверочным входом устройства, второй вход подключен к выходу первого сумматора по модулю два 2, а выход - к первому входу анализатора 5 синдрома.

Корректор 4 ошибок также представляет собой сумматор по модулю два.

Анализатор 5 синдрома предназначен для обнаружения ошибок в информационных и проверочных символах и представляет собой регистр сдвига с обратными связями и сумматорами по модулю два, состав и количество которых определяется порождающими многочленами ортогонального сверточного кода. Первый вход соединен с выходом формирователя 3 синдрома, второй вход - с выходом четвертого элемента ИЛИ 13, первый выход - с формирователем 6 проверок, второй выход - с входами третьего элемента ИЛИ 8 и блоком умножения на весовые коэффициенты 19, третий выход - с первым входом второго сумматора по модулю два 11.

Формирователь сигнала 5 проверок предназначен для формирования проверок, ортогональных относительно символов, поступающих по проверочному каналу.

В качестве формирователя 6 проверок используются три сумматора по модулю два. Вход соединен с первым выходом анализатора 5 синдрома, а выход - с первым входом решающей схемы 7.

Решающая схема 7 предназначена для принятия решения о достоверности принятых символов. В качестве решающей схемы 7 используется элемент И, первый вход которого соединен с выходом формирователя 6 проверок, второй вход - с выходом третьего элемента ИЛИ 8, а выход - с вторым входом четвертого элемента ИЛИ 13.

Третий элемент ИЛИ 8 предназначен для формирования разрешающего сигнала "1" на второй вход решающей схемы 7 из системы проверок А2, А3, А4, поступающих на его вход с второго выхода анализатора 5 синдрома.

Пороговый элемент 9 предназначен для принятия решения о достоверности принятых символов. Уровень срабатывания порогового элемента 9 выбирается, исходя из структуры проверок. В качестве порогового элемента 9 для случая принятия решения о достоверности принятых информационных символов по взвешенным проверкам может быть использован суммирующий триггер Шмитта (3). Выход порогового элемента 9 соединен с первым входом четвертого элемента ИЛИ 13.

Второй кодер 10 предназначен для формирования добавочных разрядов в порождающем многочлене квазиортогонального сверточного кода, позволяющих увеличить вес начального кодового слова квазиортогонального сверточного кода. Он представляет собой регистр сдвига, связанный с сумматорами по модулю два, число разрядов которого и связи обусловлены видом дополнительного многочлена квазиортогонального сверточного кода. Вход соединен с выходом корректора 4 ошибок, а первый выход является информационным выходом устройства.

Четвертый элемент ИЛИ 13 предназначен для объединения сигналов коррекции с выходов порогового элемента 9 и решающей схемы 7. Выход четвертого элемента ИЛИ 13 соединен с вторыми входами корректора 4 ошибок, анализатора 5 синдрома, второго сумматора по модулю два 11 и первого элемента ИЛИ 12.

Генератор 14 тактовых импульсов предназначен для формирования тактовых импульсов, необходимых для работы формирователя временного интервала 17, и является самостоятельным устройством. Выход генератора 14 тактовых импульсов связан с третьим входом элемента 15 "ЗАПРЕТ".

Элемент 15 "ЗАПРЕТ" предназначен для подачи тактовых импульсов с выхода генератора 14 тактовых импульсов на вход формирователя временного интервала 17 в промежуток времени от момента поступления на первый вход элемента 15 "ЗАПРЕТ" сигнала о наличии ошибок с третьего выхода анализатора 5 синдрома через второй сумматор по модулю два 11 и первый элемент ИЛИ 12 до момента поступления на его второй вход сигнала с выхода второго элемента ИЛИ 18.

Пороговый счетчик 16 предназначен для подсчета количества сигналов ошибок, поступающих с третьего выхода анализатора 5 синдрома через второй сумматор по модулю два 11 и первый элемент ИЛИ 12, и выдачи сигнала "ошибки" в случае переполнения. Порог срабатывания порогового счетчика 16 выбирается, исходя из корректирующих свойств квазиортогонального сверточного кода и требований по допустимой вероятности трансформации сообщений.

Формирователь временного интервала 17 предназначен для установления временного интервала анализа информации, поступающей на вход порогового счетчика 16. В качестве формирователя временного интервала 17 используется счетчик, порог срабатывания которого выбирается, исходя из допустимой вероятности трансформации сообщений, длины кодового ограничения и корректирующей способности квазиортогонального сверточного кода.

Второй элемент ИЛИ 18 предназначен для установки в закрытое состояние элемента 15 "ЗАПРЕТ" и сброса показаний порогового счетчика 16 и формирователя временного интервала 17 в случае поступления на входы элемента ИЛИ 18 сигнала переполнения как с выхода порогового счетчика 16, так и с выхода формирователя временного интервала 17.

Блок 19 умножения на весовой коэффициент предназначен для умножения сигналов ортогональных проверок Аi на соответствующие им весовые множители и суммирования сигналов значений взвешенных ортогональных проверок. В качестве блока 19 умножения на весовой коэффициент может быть использован инвертирующий сумматор, построенный на основе операционного усилителя (3). Вход блока 19 подключен к второму выходу анализатора 5 синдрома, а выход - ко входу порогового элемента 9.

Сущность изобретения состоит в том, что с введением новых элементов и связей реализуется новая дисциплина функционирования порогового декодера сверточного кода, состоящая в том, что решение о значении шумового символа производится на основе принятия гибких решений на пороговом элементе. Кроме этого, за счет определения значения шумового символа производится коррекция сигнала коррекции с выхода порогового элемента, что в совокупности, позволяет исправлять большую часть трехкратных ошибок, что в свою очередь повышает достоверность декодирования пороговым декодером сверточного кода.

Пусть порождающий многочлен квазиортогонального сверточного кода имеет вид (2)

Рк(х) = Ро(х) + Рg(х)хе (1)

Для наглядности рассмотрим квазиортогональный сверточный код со скоростью R= 1/2, кодовым ограничением nА=12, минимальным кодовым расстоянием αmin=7, порождающим многочленом вида (2):

Рk(х)=х5+х4+х3+1+(х+1) х7=

= х8+х7+х5+х4+х3+1 (2)

При поступлении на информационный и проверочный входы декодера информационной и проверочной последовательностей соответственно, на выходе формирователя синдрома 3 (фиг. 1 и 2) образуется последовательность символов синдрома вида 2:

S02=ео1+е02;

S12=е11+е12;

S22=е21+е22;

S32=е01+е31+е32;

S42=е01+е11+е41+е42;

S52=е01+е11+е21+е51+е52. (3)

На основании символов синдрома в анализаторе синдрома 5 формируется система ортогональных проверок {Ak}, k= относительно е

относительно е

А1=S02= е01+е02;

А2=S32=e 01+e31+e32;

A3=e01+e11+e41+e42;

A4=S12+S52= e01+e21+e51+e12+ e52 (4)

В предлагаемом устройстве система проверок {Ak} подается на блок умножения на весовой коэффициент, где каждая из проверок {Ak} умножaется на коэффициент, зависящий от веса проверок (чем меньше вес проверки, тем больше коэффициент).

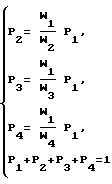

Принцип образования коэффициентов представлен в таблице.

Если сравнить веса проверок А1 и А2 в таблице, то видно, что W1<W2. Следовательно, на достоверность символа е01 в проверке А2оказывает влияние большее количество шумовых символов, чем на достоверность символа, чем на достоверность символа е01 в проверке А1. Следовательно, значение проверки А1 больше значения проверки А2 при принятии решения на взвешивающем пороговом элементе в W2/W1 раз. Продолжая подобные рассуждения, на основании таблицы, получим систему уравнений вида (5)

(5)

Решив выражение (5) относительно {Pk} проверок {Ak}, получим

P1=

P2=

P3=

P4=

Умноженные на коэффициенты Рk проверки Аk1=АkРk подаются на пороговый элемент 9. (В данной схеме порог выбран Pn =  ). Если

). Если  AiPi≅ Pn , то порог не превышается и на выходе порогового элемента сигнал коррекции не формируется, т.е.

AiPi≅ Pn , то порог не превышается и на выходе порогового элемента сигнал коррекции не формируется, т.е.  = 0. Если

= 0. Если  AiPi> Pn, то на выходе порогового элемента формируется сигнал коррекции

AiPi> Pn, то на выходе порогового элемента формируется сигнал коррекции  = 1 , который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора синдрома 5, второго сумматора по модулю два 11, элемента ИЛИ 12 и корректора ошибок 4, на первый вход которого поступает трансформированный информационный символ Uo+e01. На выходе корректора ошибок 4 формируется сигнал Uo+e

= 1 , который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора синдрома 5, второго сумматора по модулю два 11, элемента ИЛИ 12 и корректора ошибок 4, на первый вход которого поступает трансформированный информационный символ Uo+e01. На выходе корректора ошибок 4 формируется сигнал Uo+e = Uo. Трансформации сообщения нет. Так как в системе взвешенных проверок {Ak1} наибольшее значение имеет проверка А1, следовательно, требования к ее достоверности выше, чем к другим. Поэтому необходимо с большей вероятностью знать значение символа е02, поступающего вместе с проверочными символами по второму каналу. Из символов синдрома вида (3) в формирователе проверок 6 образуются две проверки, ортогональные относительно символа ер2 вида (6)

= Uo. Трансформации сообщения нет. Так как в системе взвешенных проверок {Ak1} наибольшее значение имеет проверка А1, следовательно, требования к ее достоверности выше, чем к другим. Поэтому необходимо с большей вероятностью знать значение символа е02, поступающего вместе с проверочными символами по второму каналу. Из символов синдрома вида (3) в формирователе проверок 6 образуются две проверки, ортогональные относительно символа ер2 вида (6)

В1=S02+S32=e02+e31+e32

B2= S02+S12+S42= e02+e41+e12+e42, (6) которые подаются на первый вход решающей схемы 7 (элемент И), на выходе которой, в случае поступления на второй вход разрешающего сигнала "1" с элемента ИЛИ 8, будет также формироваться сигнал коррекции  = 1, который через четвертый элемент ИЛИ 13 поступает в цепь обратной связи. Если разрешающий сигнал "0", то сигнал коррекции не формируется, т.е.

= 1, который через четвертый элемент ИЛИ 13 поступает в цепь обратной связи. Если разрешающий сигнал "0", то сигнал коррекции не формируется, т.е.  = 0. При появлении в канале связи на длине кодового ограничения nАошибок, кратность которых не превышает корректирующей способности ортогонального сверточного кода, входящего в состав квазиортогонального сверточного кода, происходит безошибочное декодирование принимаемого сообщения. В случае появления на длине кодового ограничения ошибок, кратность которых больше корректирующей способности ортогонального сверточного кода, входящего в состав квазиортогонального сверточного кода, происходит ошибочное декодирование сообщения, при этом факт возникновения ошибки декодирования обнаруживается в силу известного алгоритма декодирования квазиортогонального сверточного кода (прототип).

= 0. При появлении в канале связи на длине кодового ограничения nАошибок, кратность которых не превышает корректирующей способности ортогонального сверточного кода, входящего в состав квазиортогонального сверточного кода, происходит безошибочное декодирование принимаемого сообщения. В случае появления на длине кодового ограничения ошибок, кратность которых больше корректирующей способности ортогонального сверточного кода, входящего в состав квазиортогонального сверточного кода, происходит ошибочное декодирование сообщения, при этом факт возникновения ошибки декодирования обнаруживается в силу известного алгоритма декодирования квазиортогонального сверточного кода (прототип).

Декодер работает следующим образом.

В исходном состоянии регистры сдвига первого 1, второго 10 кодеров и пороговый счетчик 16 находятся в нулевом состоянии.

Пусть из канала связи на информационный и проверочный входы предлагаемого порогового декодера сверточного кода с тактовым периодом Δ Т поступают последовательности, содержащие трехкратную ошибку вида е01е11е21, ведущую к трансформации сообщения. В соответствии с соотношениями вида (3) на выходе формирователя 3 синдрома образуется синдромная последовательность вида (7)

S52=e01+e11+ e21=1;

S42=e01+e11=0; S32=e01=1;

S22=e21=1; S12=e11=1;

S02= e01= 1, которая поступает в анализатор 5 синдрома, где происходит формирование системы проверок {Ak} в соответствии с выражениями (4), ортогональной относительно первого шумового символа e01 вида (8)

А1=So2=1,

A2=S32=1,

A3=S42=0,

A4=S12 + S52=0. (8)

Система проверок {Ak}, k =  поступает на блок 19 умножения на весовой коэффициент, где происходит умножение каждой из них на соответствующий ей коэффициент Рk, k =

поступает на блок 19 умножения на весовой коэффициент, где происходит умножение каждой из них на соответствующий ей коэффициент Рk, k =  и формируется сумма

и формируется сумма  AiPi, которая поступает на пороговый элемент 9, где сравнивается со значением порога Pn=

AiPi, которая поступает на пороговый элемент 9, где сравнивается со значением порога Pn=  , т.е.

, т.е.

AiPi= 1·

AiPi= 1·  + 1·

+ 1·  + O·

+ O·  + 0·

+ 0·  =

=  > Pn

> Pn

На выходе порогового элемента 9 формируется сигнал коррекции  = 1, который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора 5 синдрома, где происходит устранение влияния исправляемой ошибки и последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный информационный символ Vo+e01. На выходе корректора 4 ошибок формируется сигнал Uo+e

= 1, который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора 5 синдрома, где происходит устранение влияния исправляемой ошибки и последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный информационный символ Vo+e01. На выходе корректора 4 ошибок формируется сигнал Uo+e = Uo. Следовательно, трансформация символа V0 устраняется. На этом заканчивается работа устройства на данном такте и происходит сдвиг информации вправо на один такт. Устройство готово для работы на следующем такте. Записанный в анализаторе 5 синдрома синдром имеет вид S65S52S42S32S22S12

= Uo. Следовательно, трансформация символа V0 устраняется. На этом заканчивается работа устройства на данном такте и происходит сдвиг информации вправо на один такт. Устройство готово для работы на следующем такте. Записанный в анализаторе 5 синдрома синдром имеет вид S65S52S42S32S22S12 001011. При этом формируется следующая система проверок {Ak}, k =

001011. При этом формируется следующая система проверок {Ak}, k =

А1= 1, А2=1; А3=0; А4=1, которая поступает на блок 19 умножения на весовой коэффициент и далее сумма на вход порогового элемента 9 AiPi= 1·

AiPi= 1·  + 1·

+ 1·  + O·

+ O·  + 1·

+ 1·  =

=  > Pn

> Pn

На выходе формируется сигнал коррекции  = 1, который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора 5 синдрома, где происходит устранение влияния исправляемой ошибки на последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный символ V1+e11. На выходе корректора 4 ошибок формируется сигнал U1+e

= 1, который через элемент ИЛИ 13 поступает по цепи обратной связи на вторые входы анализатора 5 синдрома, где происходит устранение влияния исправляемой ошибки на последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный символ V1+e11. На выходе корректора 4 ошибок формируется сигнал U1+e = U1. Трансформация символа V1устраняется. Происходит сдвиг информации вправо на один такт. На следующем такте устройство работает аналогично. Формируется синдром: 111001 и система проверок: IIII, происходит превышение порога

= U1. Трансформация символа V1устраняется. Происходит сдвиг информации вправо на один такт. На следующем такте устройство работает аналогично. Формируется синдром: 111001 и система проверок: IIII, происходит превышение порога  AiPi> Pn и на выходе порогового элемента 9 формируется сигнал коррекции

AiPi> Pn и на выходе порогового элемента 9 формируется сигнал коррекции  = 1, который корректирует неправильно принятый символ U2+e

= 1, который корректирует неправильно принятый символ U2+e = U1. Трехкратная ошибка полностью исправляется, трансформация сообщения не происходит.

= U1. Трехкратная ошибка полностью исправляется, трансформация сообщения не происходит.

Пусть из канала связи на информационный и проверочный входы предлагаемого декодера сверточного кода поступают последовательности, содержащие трехкратную ошибку вида е01е11е02. В соответствии с соотношениями вида (3) на выходе формирователя синдрома 3 образует- ся синдромная последовательность: S52S42S32S22S12S02 001010, которая поступает в анализатор 5 синдрома, где происходит формирование системы проверок {Ak} в соответствии с выражениями (4), ортогональной относительно первого шумового символа е01 A1=0; A2=1; A3=0; A4=1. Система проверок {Ak}, k =

001010, которая поступает в анализатор 5 синдрома, где происходит формирование системы проверок {Ak} в соответствии с выражениями (4), ортогональной относительно первого шумового символа е01 A1=0; A2=1; A3=0; A4=1. Система проверок {Ak}, k =  поступает на блок 19 умножения на весовой коэффициент, где происходит умножение каждой из них на соответствующий ей коэффициент {Pk}, k =

поступает на блок 19 умножения на весовой коэффициент, где происходит умножение каждой из них на соответствующий ей коэффициент {Pk}, k =  и формируется сумма

и формируется сумма  AiPi, которая поступает на пороговый элемент 9, где сравнивается с порогом Pn=

AiPi, которая поступает на пороговый элемент 9, где сравнивается с порогом Pn=  , т.е.

, т.е.

AiPi= 0·

AiPi= 0·  + 1·

+ 1·  + 0·

+ 0·  + 1·

+ 1·  =

=  < Pn,. на выходе порогового элемента 9 сигнал коррекции не формируется, т.е.

< Pn,. на выходе порогового элемента 9 сигнал коррекции не формируется, т.е.  = 0. Одновременно с этим по первому выходу анализатора 5 синдрома в формирователе 6 проверок образуются проверки В1=1, В2=1, в соответствии с выражениями вида (6), ортогональных относительно шумового символа е02, которые поступают на первый вход решающей схемы 7, на второй вход которой поступает разрешающий сигнал "1" с выхода третьего элемента ИЛИ 8, так как А2+А3+А4=1+0+1=1. На выходе решающей схемы формируется сигнал коррекции

= 0. Одновременно с этим по первому выходу анализатора 5 синдрома в формирователе 6 проверок образуются проверки В1=1, В2=1, в соответствии с выражениями вида (6), ортогональных относительно шумового символа е02, которые поступают на первый вход решающей схемы 7, на второй вход которой поступает разрешающий сигнал "1" с выхода третьего элемента ИЛИ 8, так как А2+А3+А4=1+0+1=1. На выходе решающей схемы формируется сигнал коррекции  = 1, который через объединяющий четвертый элемент ИЛИ 13 поступает по цепи обрат- ной связи на вторые входы анализатора синдрома 5, где происходит устранение влияния исправляемой ошибки на последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный информационный символ V0+e01. На выходе корректора 4 ошибок формируется сигнал Uo+e

= 1, который через объединяющий четвертый элемент ИЛИ 13 поступает по цепи обрат- ной связи на вторые входы анализатора синдрома 5, где происходит устранение влияния исправляемой ошибки на последующие символы, второго сумматора по модулю два 11, первого элемента ИЛИ 12 и корректора 4 ошибок, на первый вход которого поступает трансформированный информационный символ V0+e01. На выходе корректора 4 ошибок формируется сигнал Uo+e = Uo. Трансформация символа устраняется. Происходит сдвиг информации вправо на один такт.

= Uo. Трансформация символа устраняется. Происходит сдвиг информации вправо на один такт.

Устройство готово для работы на следующем такте. Записанный в анализаторе синдрома 5 синдром имеет вид S62S52S42S32S22S12 111001. Формируется система проверок {Ak}, k =

111001. Формируется система проверок {Ak}, k =  ; А1=1; А2=1; А3=1; А4=1, происходит превышение порога

; А1=1; А2=1; А3=1; А4=1, происходит превышение порога  AiPi> Pn и на выходе порогового элемента 9 формируется сигнал коррекции

AiPi> Pn и на выходе порогового элемента 9 формируется сигнал коррекции  = 1, который корректируется неправильно принятый символ U1+e

= 1, который корректируется неправильно принятый символ U1+e = U1. Трехкратная ошибка полностью исправляется, трансформация сообщений не происходит.

= U1. Трехкратная ошибка полностью исправляется, трансформация сообщений не происходит.

В случае возникновения трехкратных ошибок, которые не исправляются предлагаемым устройством, они обнаруживаются за счет положительных свойств прототипа по обнаружению ошибок в предлагаемом пороговом декодере сверточного кода.

Таким образом, если раньше происходила трансформация сообщения при трехкратной и более ошибке и она только обнаруживалась, то теперь в предлагаемом устройстве за счет введения новых элементов и связей исправляется большая часть трехкратных ошибок, а остальная часть трехкратных и более ошибок обнаруживается. Для того, чтобы исправлять большую часть трехкратных ошибок, используя прежнее устройство, необходимо, чтобы ортогональный сверточный код, входящий в состав квазиортогонального сверточного кода, имел αomin≥7. Пример такого кода может быть 4

Р(х)=х17+х16+х13+х7+х2+1.

При этом n А=36, R=1/2, что и доказывает достижение задачи изобретения.

Известный пороговый декодер сверточного кода на длине кодового ограничения nА= 12 исправлял все однократные и двухкратные ошибки, а также 10 трехкратных ошибок, т.е. С121+С122+10=12+66+10=88.

Остальную часть ошибок более высокой кратности он обнаруживал.

Таким образом, К1= 298-88= 210 - количество неисправляемых сочетаний ошибок на длине кодового ограничения nA=12 в известном пороговом декодере сверточного кода.

При исследовании работы предлагаемого устройства было рассмотрено декодирование всех возможных комбинаций однократных, двухкратных и трехкратных ошибок на длине кодового ограничения nА=12. Общее количество их сочетаний равно С121+С122+С123=12+66+220=298.

При этом предлагаемое устройство исправляло все однократные, двухкратные и 120 трехкратных ошибок, остальные ошибки оно обнаруживало.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах цифровой связи, использующих сверточные коды. Цель изобретения - повышение достоверности декодирования за счет исправления большей части трехкратных ошибок - достигается введением элементов ИЛИ 8, 13, блока 19 умножения на весовой коэффициент, решающей схемы 7 и формирователя 6 проверок, а также введены пороговый счетчик 16 и пороговый элемент 9, декодер, содержащий кодеры 1, 10, корректор ошибок 4, сумматоры по модулю два 2 и 11, элементы ИЛИ 12, 18, формирователь 3 синдрома, генератор 14 тактовых импульсов, формирователь 17 временного интервала, элемент 15. Сущность изобретения: с введением новых элементов и связей реализуется новая дисциплина функционирования порогового декодера сверточного кода, состоящая в том, что решение о значении шумового символа производится на основе принятия гибких решений на пороговом элементе. Кроме того, за счет определения значения шумового символа производится коррекция сигнала коррекции с выхода порогового элемента, что в совокупности позволяет исправлять большую часть трехкратных ошибок, что в свою очередь повышает достоверность декодирования. 2 ил., 1 табл.

ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА, содержащий первый кодер, вход которого является информационным входом декодера, первый и второй выходы первого кодера соединены с первыми входами соответственно корректора ошибок и первого сумматора по модулю два, выход которого соединен с первым входом формирователя синдрома, второй вход которого является проверочным входом декодера, выход формирователя синдрома соединен с первым входом анализатора синдрома, первый выход которого соединен с первым входом второго сумматора по модулю два, выход которого соединен с первым входом первого элемента ИЛИ, выход первого элемента ИЛИ соединен с первыми входами элемента ЗАПРЕТ и порогового счетчика, выход которого является выходом сигнала ошибок декодера и соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторыми входами порогового счетчика и элемента ЗАПРЕТ и первым входом формирователя временного интервала, выход которого соединен с вторым входом второго элемента ИЛИ, генератор тактовых импульсов, выход которого соединен с третьим входом элемента ЗАПРЕТ, выход которого соединен с вторым входом формирователя временного интервала, выход корректора ошибок соединен с входом второго кодера, первый выход которого является информационным выходом декодера, второй выход соединен с вторым входом первого сумматора по модулю два, вторые входы корректора ошибок, анализатора синдрома второго сумматора по модулю два и первого элемента ИЛИ объединены, и пороговый элемент, отличающийся тем, что, с целью повышения достоверности декодера, в него введены формирователь сигнала проверок, решающая схема,блок умножения, третий и четвертый элементы ИЛИ, вторые выходы анализатора синдрома соединены с входами формирователя сигнала проверок, выходы которого соединены с первыми входами решающей схемы, выход которой соединен с первым входом третьего элемента ИЛИ, третьи выходы анализатора синдрома соединены с входами блока умножения и четвертого элемента ИЛИ, выход которого соединен с вторым входом решающей схемы, выходы блока умножения соединены с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ.

| Т.Касами, Н.Токура, Е.Ивадари, Я.Ивагаки | |||

| Теория кодирования | |||

| М.: Мир, 1978, 576 с. |

Авторы

Даты

1994-11-15—Публикация

1991-12-02—Подача