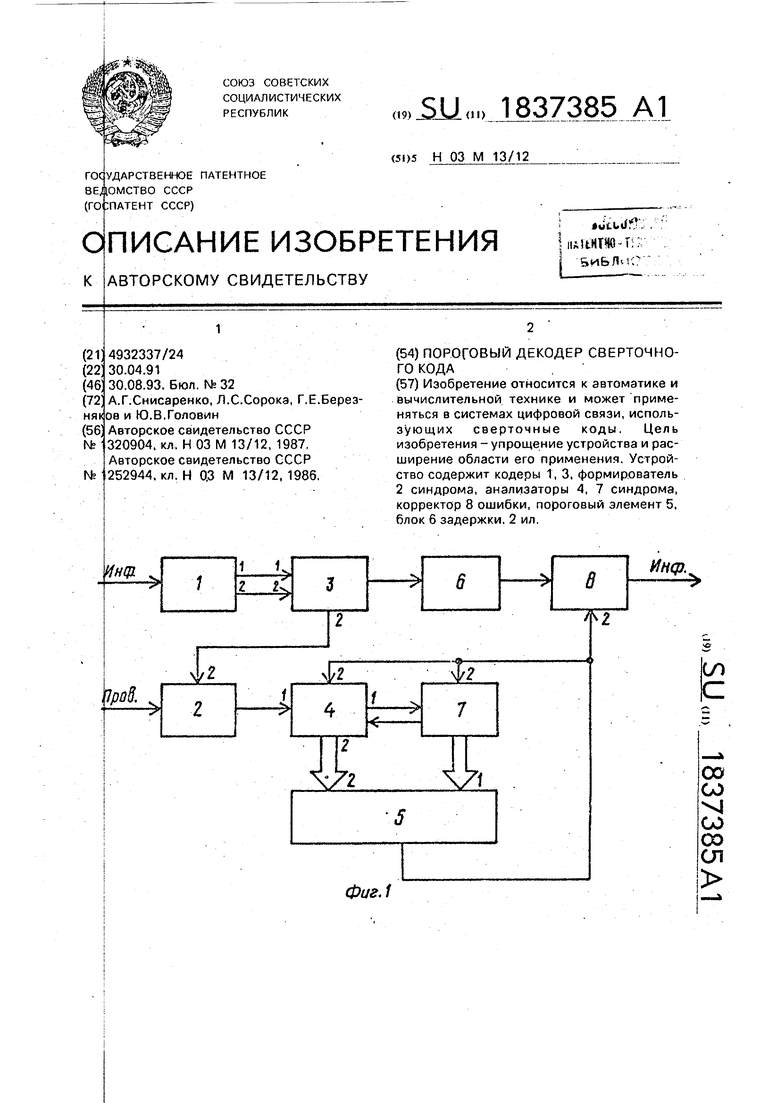

Изобретение относится к автоматике и вычислительной технике и может применяться в системах цифровой связи, использующих сверточные коды.

Цель изобретения - упрощение устройства и расширение области его применения.

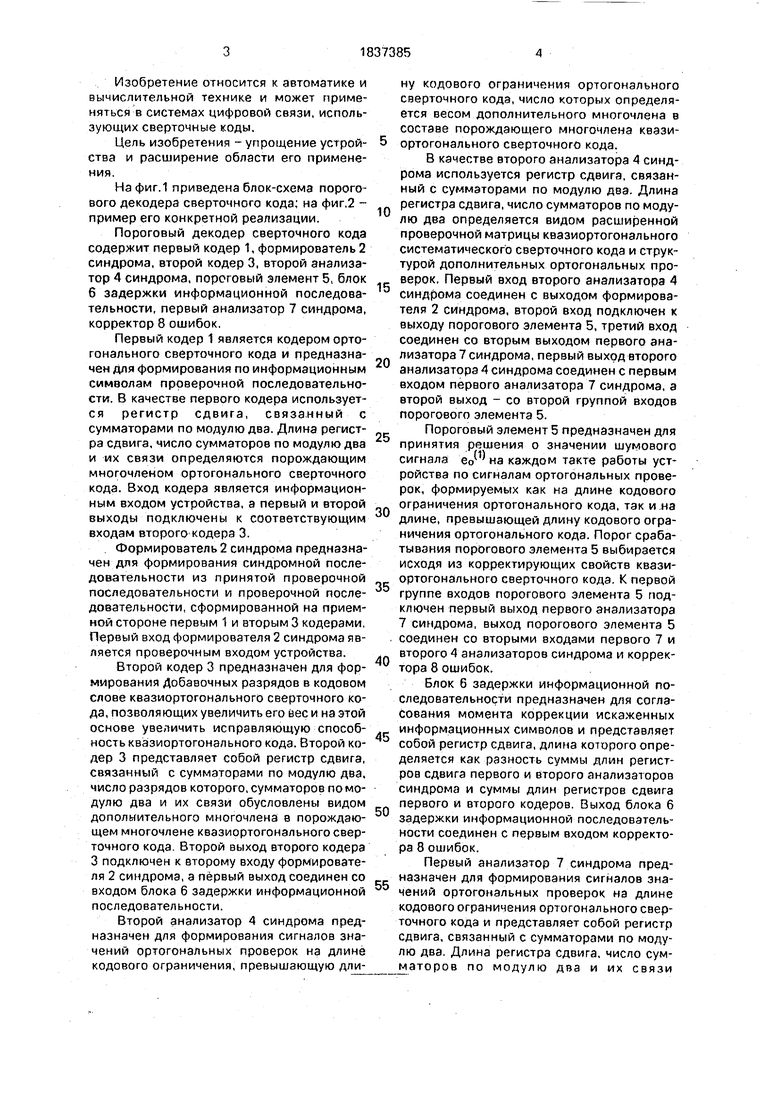

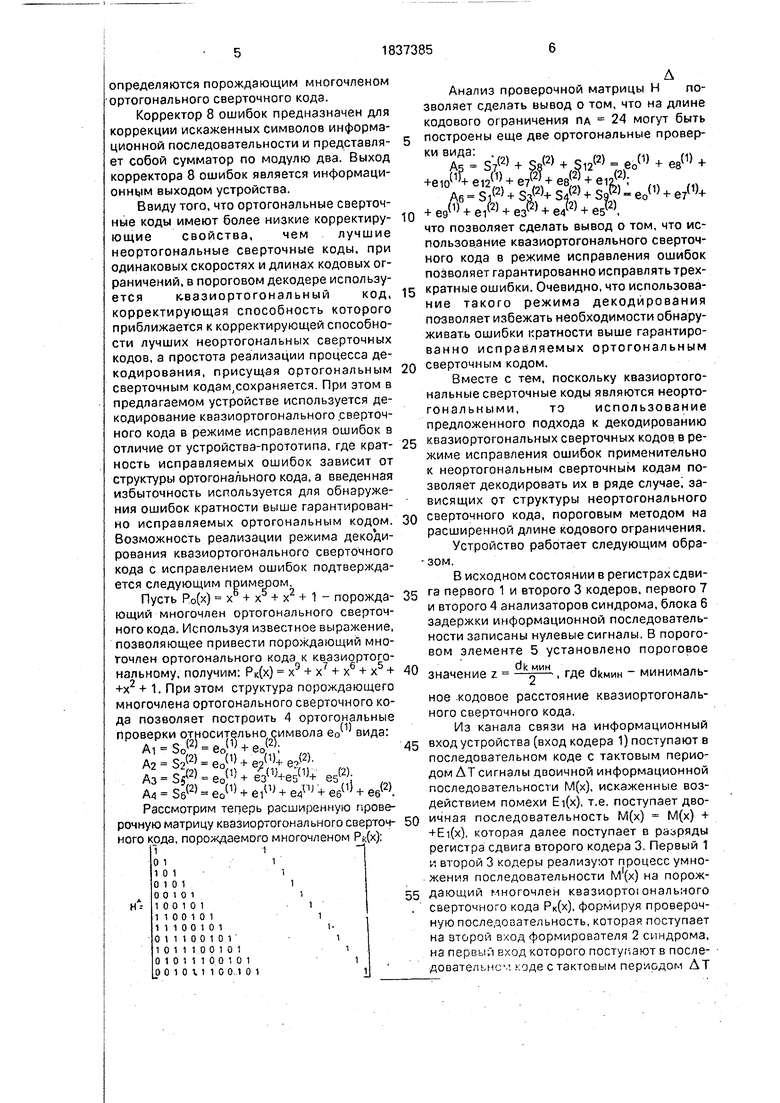

Нафиг.1 приведена блок-схема порогового декодера сверточного кода; на фиг.2 - пример его конкретной реализации.

Пороговый декодер сверточного кода содержит первый кодер 1, формирователь 2 синдрома, второй кодер 3, второй анализатор 4 синдрома, пороговый элемент 5, блок б задержки информационной последовательности, первый анализатор 7 синдрома, корректор 8 ошибок.

Первый кодер 1 является кодером ортогонального сверточного кода и предназначен для формирования по информационным символам проверочной последовательности. В качестве первого кодера используется регистр сдвига, связанный с сумматорами по модулю два. Длина регистра сдвига, число сумматоров по модулю два и их связи определяются порождающим многочленом ортогонального сверточного кода. Вход кодера является информационным входом устройства, а первый и второй выходы подключены к соответствующим входам второго кодера 3.

Формирователь 2 синдрома предназначен для формирования синдромной последовательности из принятой проверочной последовательности и проверочной последовательности, сформированной на приемной стороне первым 1 и вторым 3 кодерами, Первый вход формирователя 2 синдрома является проверочным входом устройства.

Второй кодер 3 предназначен для формирования Добавочных разрядов в кодовом слове кеазиортогонэльного сверточного кода, позволяющих увеличить его вес и на этой основе увеличить исправляющую способность квазиортогонального кода. Второй кодер 3 представляет собой регистр сдвига, связанный с сумматорами по модулю два. число разрядов которого, сумматоров по модулю два и их связи обусловлены видом дополнительного многочлена в порождающем многочлене квазиортогонального сверточного кода. Второй выход второго кодера 3 подключен к второму входу формирователя 2 синдрома, а первый выход соединен со входом блока 6 задержки информационной последовательности.

Второй анализатор 4 синдрома предназначен для формирования сигналов значений ортогональных проверок на длине кодового ограничения, превышающую длиа

15

20

ну кодового ограничения ортогонального сверточного кода, число которых определяется весом дополнительного многочлена в составе порождающего многочлена квэзи- 5 ортогонального сверточного кода.

В качестве второго анализатора 4 синдрома используется регистр сдвига, связанный с сумматорами по модулю два. Длина регистра сдвига, число сумматоров по моду- лю два определяется видом расширенной проверочной матрицы квазиортогонального систематического сверточного кода и структурой дополнительных ортогональных проверок. Первый вход второго анализатора 4 синдрома соединен с выходом формирователя 2 синдрома, второй вход подключен к выходу порогового элемента 5, третий вход соединен со вторым выходом первого анализатора 7 синдрома, первый выход второго анализатора 4 синдрома соединен с первым входом первого анализатора 7 синдрома, а второй выход - со второй группой входов порогового элемента 5.

Пороговый элемент 5 предназначен для принятия решения о значении шумового сигнала ео на каждом такте работы устройства по сигналам ортогональных проверок, формируемых как на длине кодового ограничения ортогонального кода, так и .на длине, превышающей длину кодового ограничения ортогонального кода. Порог срабатывания порогового элемента 5 выбирается исходя из корректирующих свойств квазиортогонального сверточного кода. К первой группе входов порогового элемента 5 подключен первый выход первого анализатора 7 синдрома, выход порогового элемента 5 . соединен со вторыми входами первого 7 и второго 4 анализаторов синдрома и коррек- тора 8 ошибок.

Блок 6 задержки информационной последовательности предназначен для согласования момента коррекции искаженных информационных символов и представляет собой регистр сдвига, длина которого определяется как разность суммы длин регистров сдвига первого и второго анализаторов синдрома и суммы длин регистров сдвига первого и второго кодеров. Выход блока 6 задержки информационной последовательности соединен с первым входом корректора 8 ошибок.

Первый анализатор 7 синдрома предназначен для формирования сигналов значений ортогональных проверок на длине кодового ограничения ортогонального сверточного кода и представляет собой регистр сдвига, связанный с сумматорами по модулю два. Длина регистра сдвига, число сум- jnaTopoB по модулю два и их связи

30

35

45

50

55

сигналы проверочной последовательности, сформированные на передающей стороне, вида:

Мп(х)-М(х)гМх)+Е2(х).

В случае отсутствия ошибок, т.е. при Ei(x) Е2(х)в 0, в регистры сдвига второго 4 и первого 7 анализаторов синдрома запишется нулевой синдром. Сигналы ортогональных проверок Ai-Аб равны нулю. Порог порогового элемента 5 превышен не будет. В результате информационная последовательность М(х). поступающая с выхода блока 6 задержки информационной последовательности на первый вход корректора 8 ошибок, коррекции не подвергается и поступает в неискаженном виде получателю. Коррекция соответствующих разрядов регистров сдвига первого 7 и второго 4 анализаторов синдрома не производится.

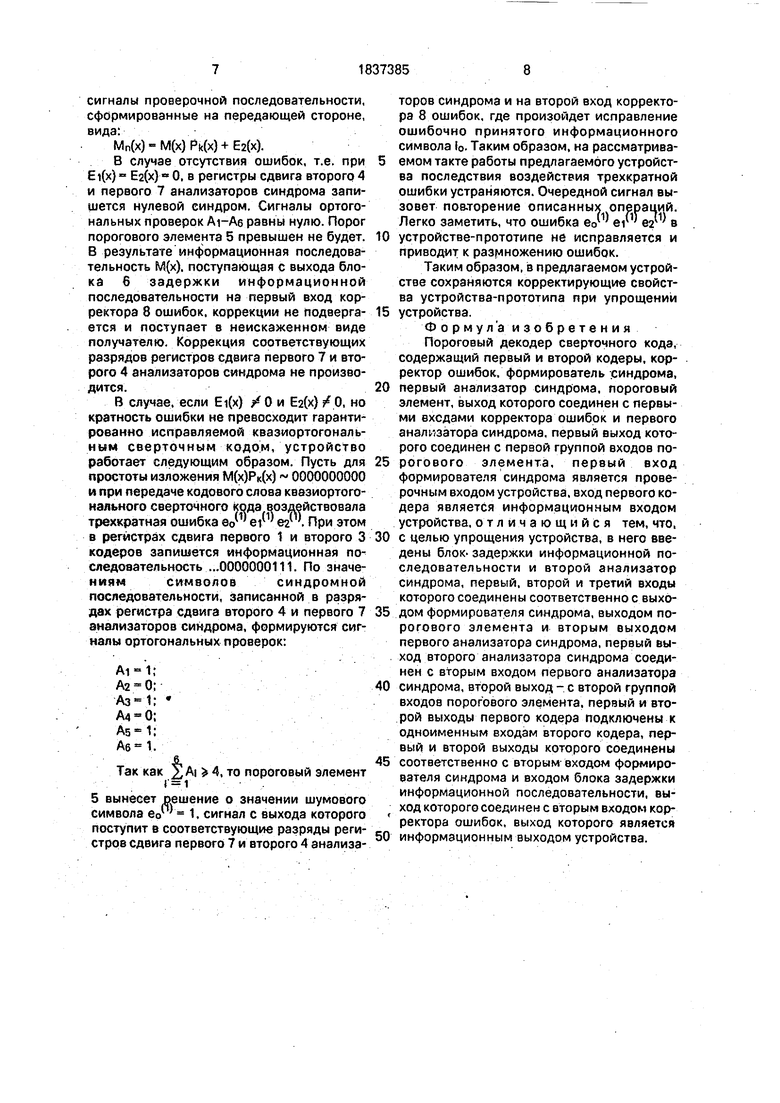

В случае, если Ei(x) 0 и Е2(х} 0, но кратность ошибки не превосходит гарантированно исправляемой квазиортогональным сверточным кодом, устройство работает следующим образом. Пусть для простоты изложения М(х)Рк(х) 0000000000 и при передаче кодового слова квазиортогонального сеерточного кода воздействовала трехкратная ошибка ег ,ег . При этом в регистрах сдвига первого 1 и второго 3 кодеров запишется информационная последовательность ...0000000111. По значениямсимволовсиндромнойпоследовательности, записанной в разрядах регистра сдвига второго 4 и первого 7 анализаторов синдрома, формируются сигналы ортогональных проверок:

А2 0; Аз--1: А4-0; .

.

Так как ХА| 4, то пороговый элемент

-.., .

5 вынесет решение о значении шумового символа ест 1, сигнал с выхода которого поступит в соответствующие разряды регистров сдвига первого 7 и второго 4 анализаторов синдрома и на второй вход корректора 8 ошибок, где произойдет исправление ошибочно принятого информационного символа 10. Таким образом, на рассматриваемом такте работы предлагаемого устройства последствия воздействия трехкратной ошибки устраняются. Очередной сигнал вызовет повторение описанных операций. Легко заметить, что ошибка е«/1 ег1 ег1 в

устройстве-прототипе не исправляется и приводит к размножению ошибок.

Таким образом, в предлагаемом устройстве сохраняются корректирующие свойства устройства-прототипа при упрощений

устройства.

Формул а изобретения Пороговый декодер сверточного кода, содержащий первый и второй кодеры, корректор ошибок, формирователь синдрома,

первый анализатор синдрома, пороговый элемент, выход которого соединен с первыми входами корректора ошибок и первого анализатора синдрома, первый выход которого соединен с первой группой входов порогового элемента, первый вход формирователя синдрома является проверочным входом устройства, вход первого кодера является информационным входом устройства, отличающийся тем, что,

с целью упрощения устройства, в него введены блок-задержки информационной последовательности и второй анализатор синдрома, первый, второй и третий входы которого соединены соответственно с выходом формирователя синдрома, выходом порогового элемента и вторым выходом первого анализатора синдрома, первый выход второго анализатора синдрома соединен с вторым входом первого анализатора

синдрома, второй выход - с второй группой входов порогового элемента, первый и второй выходы первого кодера подключены к одноименным входам второго кодера, первый и второй выходы которого соединены

соответственно с вторым входом формирователя синдрома и входом блока задержки информационной последовательности, выход которого соединен с вторым входом корректора ошибок, выход которого является

информационным выходом устройства.

i

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

Изобретение относится к автоматике и вычислительной технике и может применяться в системах цифровой связи, использующих сверточные коды. Цель изобретения -упрощение устройства и расширение области его применения. Устройство содержит кодеры 1, 3, формирователь 2 синдрома, анализаторы 4, 7 синдрома, корректор 8 ошибки, пороговый элемент 5. блок 6 задержки. 2 ил.

Рё,

.актор С.Ходакова

Составитель А.Снисзренко

Техред М.МоргенталКорректор И.Шмакова

За

аз 2870

Тираж

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Подписное

Авторы

Даты

1993-08-30—Публикация

1991-04-30—Подача