Изобретение относится к технике связи и может использоваться в устройствах помехоустойчивого кодирования при передаче дискретной информации.

Цель изобретения - повьшение помехоустойчивости устройства з.а счет уменьшения эффекта распространения ошибок.

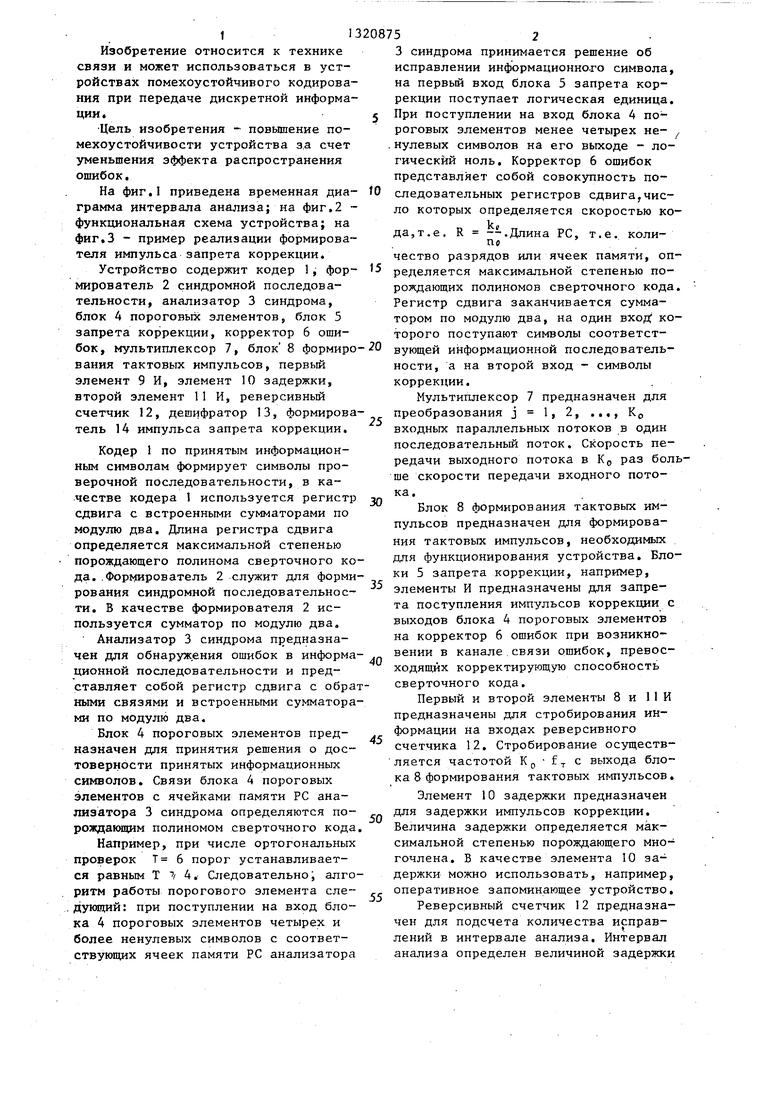

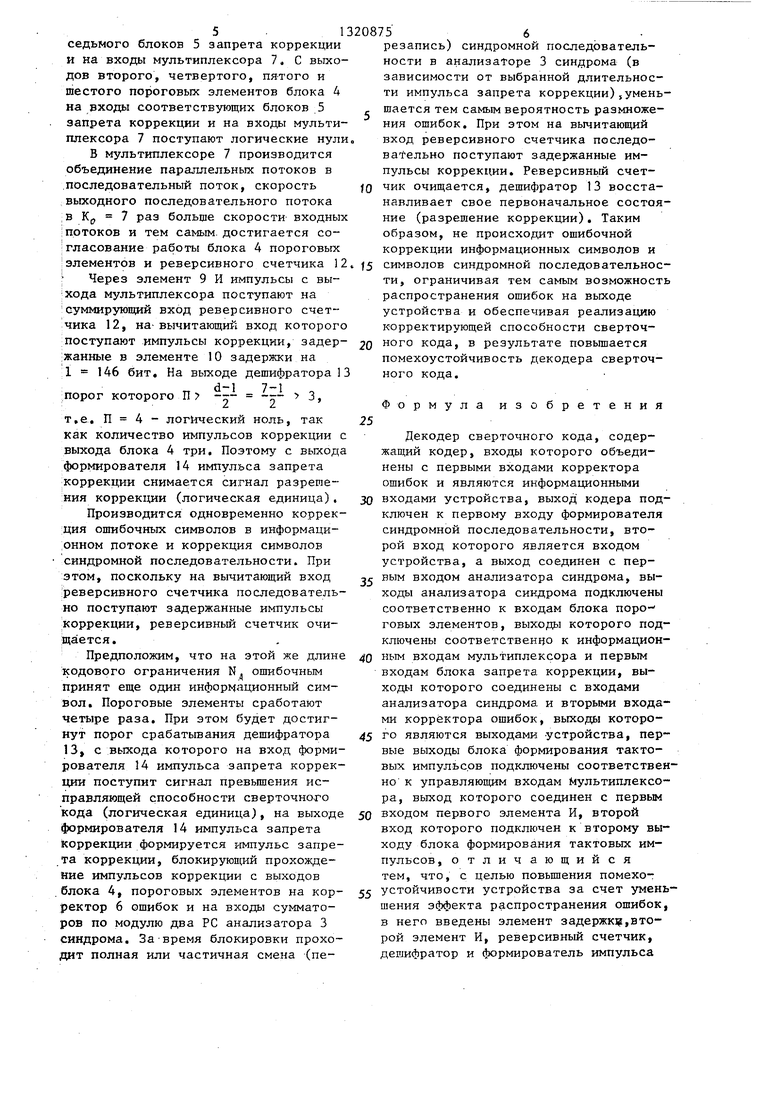

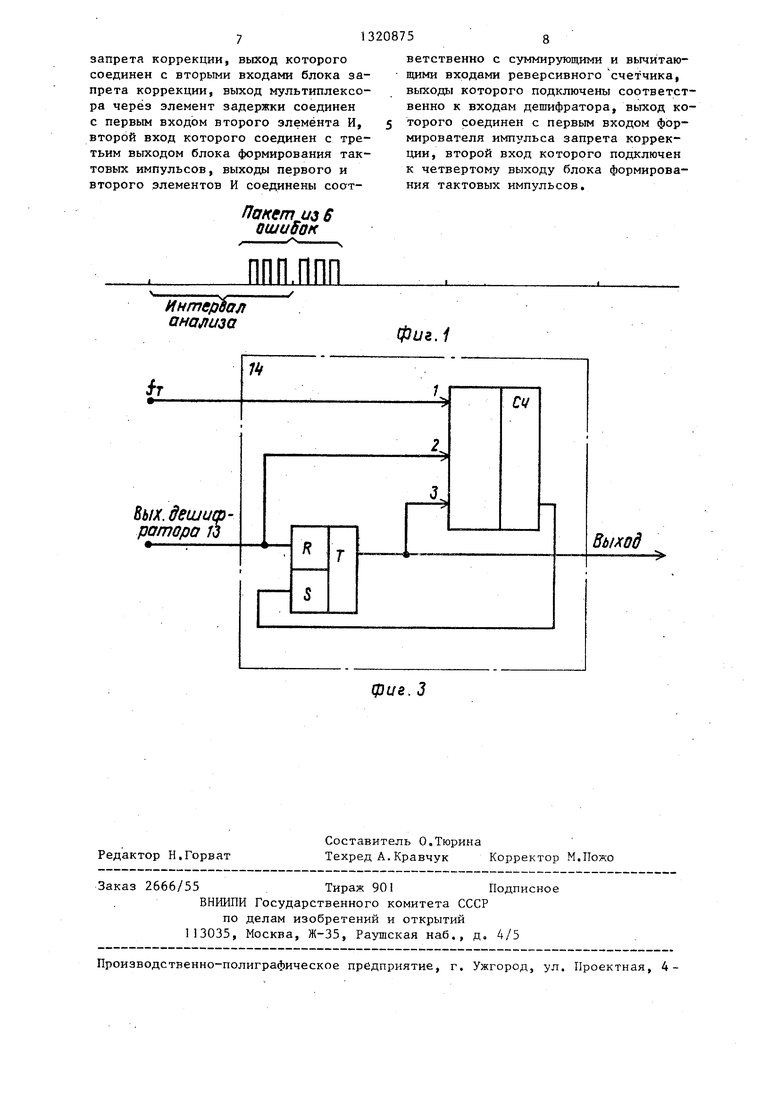

На фиг,1 приведена временная диаграмма интервала анализа; на фиг,2 - функциональная схема устройства; на фиг.З - пример реализации формирователя импульса запрета коррекции.

Устройство содержит кодер , формирователь 2 синдромной последовательности, анализатор 3 синдрома, блок 4 пороговых элементов, блок 5 запрета коррекции, корректор 6 ошибок, мультиплексор 7, блок 8 формирования тактовых импульсов, первый элемент 9 И, элемент 10 задержки, второй элемент 11 И, реверсивный счетчик 12, дешифратор 13, формирователь 14 импульса запрета коррекции.

Кодер 1 по принятым информационным символам формирует символы проверочной последовательности, в качестве кодера 1 используется регистр сдвига с встроенными сумматорами по модулю два. Длина регистра сдвига определяется максимальной степенью порождающего полинома сверточного кода. .Формирователь 2 служит для формирования синдромной последовательности. В качестве формирователя 2 используется сумматор по модулю два.

Анализатор 3 синдрома предназначен для обнаружения ошибок в информационной последовательности и представляет собой регистр сдвига с обраными связями и встроенными сумматорами по модулю два.

Блок 4 пороговых элементов предназначен для принятия решения о достоверности принятых информационных символов. Связи блока 4 пороговых элементов с ячейками памяти PC анализатора 3 синдрома определяются порождающим полиномом сверточного кода

Например, при числе ортогональных проверок Т 6 порог устанавливается равным Т /4, Следовательно i алгоритм работы порогового элемента сле- дуклдий: при поступлении на вход блока 4 пороговых элементов четырех и более ненулевых символов с соответствующих ячеек памяти PC анализатора

3 синдрома принимается решение об исправлении информационного символа, на первый вход блока 5 запрета коррекции поступает логическая единица. При поступлении на вход блока 4 пороговых элементов менее четырех не- / .нулевых символов на его выходе - логический ноль, Корректор 6 ошибок представляет собой совокупность последовательных регистров сдвига,число которых определяется скоростью кода, т.е. R

-.Длина ЕС, т.е. коли- пс

5

0

5

0

5

0

5

0

5

чество разрядов или ячеек памяти, определяется максимальной степенью порождающих полиномов сверточного кода. Регистр сдвига заканчивается сумматором по модулю два, на один вход которого поступают символы соответствующей информационной последовательности, а на второй вход - символы коррекции.

Мультиплексор 7 предназначен для преобразования j 1, 2, ,,., К входных параллельных потоков в один последовательный поток. Скорость передачи выходного потока в К раз больше скорости передачи входного потока.

Блок 8 формирования тактовых импульсов предназначен для формирования тактовых импульсов, необходимых для функционирования устройства. Блоки 5 запрета коррекции, например, элементы И предназначены для запрета поступления импульсов коррекции с выходов блока 4 пороговых элементов на корректор 6 ошибок при возникновении в канале связи ошибок, превосходящих корректирующую способность сверточного кода.

Первый н второй элементы 8 и 11 И предназначены для стробироваиия информации на входах реверсивного счетчика 12. Стробирование осуществ- ляется частотой К f. с выхода блока 8 формирования тактовых импульсов.

Элемент 10 задержки предназначен для задержки импульсов коррекции. Величина задержки определяется максимальной степенью порождающего многочлена. В качестве элемента 10 задержки можно использовать, например, оперативное запоминающее устройство.

Реверсивный счетчик 12 предназначен для подсчета количества исправлений в интервале анализа. Интервал анализа определен величиной задержки

элемента 10, т.е. на интервале, совпадающем с максимальной степенью порождающего многочлена сверточного кода.

Дешифратор 13, например, полупроводниковое запоминающее устройство, предназначен для вьщачи сигналов управления на формирователь 12 импульса запрета коррекции при превьппении исправляющей способности сверточного кода. Порог дешифратора выбирается

равным П -т- ,

где d - минимальное

кодовое расстояние сверточного кода

Формирователь 14 импульса запрет коррекции служит для формирования ипульса запрета коррекции на блок 6 запрета коррекгщи (логический ноль) длительностью 1 т, где 1 - длительность импульса запрета корре ции; m - максимальная степень порождающего многочлена, при обнаружении превьшения исправляющей способности сверточного кода (появление управляющего импульса на выходе дешифратора - логическая единица).

Следовательно, алгоритм работы формирователя 14 импульса запрета коррекции следующий.

При поступлении на вход формиров теля 14 импульса запрета коррекции дешифратора 13 сигнала отсутствия превьшения исправляющей способности сверточного кода (логический ноль) с его выхода снимается сигнал разре шения коррекции (логическая единица При превьш1ении исправляющей способности формируется импульс запрета коррекции длительностью 1 и затем возврат в исходное положение - разрешение коррекции, В качестве формирователя 14 импульса запрета коррекций можно использовать, например, соответственно включенные счетчик и триггер (фиг.З),

Рассмотрим принцип работы порогового декодера на примере сверточног

0 -, кода R - Q-, d 7, т.е.

кратность гарантированно исправляемых ошибок на длине кодового ограничения№д (п1+1)-По (146+1) X 8 1176,

t fcl lil.3.

где R - скорость кода; ko - число информационных ветвей; п - общее чис

5

5 0

О вания: 5

0

5

0

5

ло ветвей сверточного кода, t - кратность исправляемых ошибок; d - минимальное расстояние сверточного кода.

Принятые информационные символы поступают на вход кодера 1. В кодере 1 из принятых информационньпс символов формируются символы проверочной последовательности, которые поступают на один из входов формирователя 2 синдромной последовательности, на второй вход которого поступают символы принятой проверочной последовательности.

Производится формирование символов синдромной последовательности, структура которой зависит от типа ошибок как в информационных, так и проверочных символах. Символы синдромной последовательности поступают на вход анализатора 3 синдрома, производится заполнение PC анализатора 3 синдрома в течение m тактов. На . т+1 такте производится анализ в блоке 4 пороговых элементов структуры синдромной последовательности и принятие решения о достоверности первого блока из k 7 информационных символов .

Решение о достоверности декодироесли на вход блока 4 пороговых элементов с анализатора 3 синдрома поступает ненулевых символов больше установленного порога, т.е, более четырех, то принимается решение, что информационный символ принят ошибочным и с выхода блока 4 одновременно на корректор 6 ошибок и на соответствующие сумматоры по модулю два анализатора 3 синдрома поступает импульс коррекции (логическая единица).

Когда в принятой последовательности ошибок нет, на входы блока 4 пороговых элементов поступает последовательность нулей, пороговые элементы не срабатывают , коррекции не происходит.

Предположим, что в принятой информации три ошибочных символа (пусть будут в первом, третьем и седьмом потоках), т.е. число ошибок не пре- BbmiaeT корректирующей способности кода.

В соответствии с алгоритмом порогового декодирования с выхода первого и третьего и седьмого пороговых элементов блока 4 импульсы коррекции (логическая единица) поступают на первые входы первого, третьего и

седьмого блоков 5 запрета коррекции и на входы мультиплексора 7, С выходов второго, четвертого, пятого и шестого пороговых элементов блока 4 на входы соответствующих блоков 5 запрета коррекции и на входы мультиплексора 7 поступают логические нули

В мультиплексоре 7 производится объединение параллельных потоков в .последовательный поток, скорость выходного последовательного потока :в Кр 7 раз больше скорости входных ;потоков и тем самым, достигается со- гласование работы блока 4 пороговых :элементов и реверсивного счетчика 12 Через элемент 9 И импульсы с вы- хода мультиплексора поступают на суммирующий вход реверсивного счет-- чика 12, на-вычитающий вход которого поступают импульсы коррекции, задер- :жанные в элементе 10 задержки на 1 146 бит. На выходе дешифратора 1

порог которого П --- --- 3,

1

т.е. П 4 - логический ноль, так как количество импульсов коррекции с выхода блока 4 три. Поэтому с выхода формирователя 14 импульса запрета коррекции снимается сигнал разрешения коррекции (логическая единица),

Производится одновременно коррек- ;Ция ошибочных СИМВОЛОВ В информаци- ;онном потоке и коррекция символов синдромной последовательности. При этом, поскольку на вычитающий вход реверсивного счетчика последовательно поступают задержанные импульсы коррекции, реверсивный счетчик очищается.

Предположим, что на этой же длине кодового ограничения N ошибочным принят еще один информационный символ. Пороговые элементы сработают четыре раза. При этом будет достигнут порог срабатывания дешифратора 13, с выхода которого на вход формирователя 14 импульса запрета коррек- 1ЦИИ поступит сигнал превьппения исправляющей способности сверточного кода (логическая единица), на выходе формирователя 14 импульса запрета коррекции формируется импульс запрета коррекции, блокирующий прохождение импульсов коррекции с выходов блока 4, пороговых элементов на корректор 6 ошибок и на входы сумматоров по модулю два PC анализатора 3 синдрома. За-время блокировки проходит полная или частичная смена (перезапись) синдромной последовательности в анализаторе 3 синдрома (в зависимости от выбранной длительности импульса запрета коррекции),умень- шается тем самым вероятность размножения ошибок. При этом на вычитающий вход реверсивного счетчика последовательно поступают задержанные импульсы коррекции. Реверсивньш счетчик очищается, дешифратор 13 восстанавливает свое первоначальное состояние (разрешение коррекции). Таким образом, не происходит ошибочной коррекции информационных символов и

символов синдромной последовательности, ограничивая тем самым возможность распространения ошибок на выходе устройства и обеспечивая реализацию корректирующей способности сверточного кода, в результате повьшзается помехоустойчивость декодера сверточного кода.

Формула изобретения

Декодер сверточного кода, содержащий кодер, входы которого объединены с первыми входами корректора ошибок и являются информационными

входами устройства, выход кодера подключен к первому входу формирователя синдромной последовательности, второй вход которого является входом устройства, а выход соединен с первым входом анализатора синдрома, выходы анализатора синдрома подключены соответственно к входам блока пороговых элементов, выходы которого подключены соответственно к информационным входам мультиплексора и первым входам блока запрета коррекции, выходы которого соединены с входами анализатора синдрома и вторыми входами корректора ошибок, выходы которого являются выходами устройства, первые выходы блока формирования тактовых импульс.ов подключены соответственно к управляюш 1м входам Мультиплексора, выход которого соединен с первым

входом первого элемента И, второй

вход которого подключен к второму выходу блока формирования тактовых импульсов, отличающийся тем, что, с целью повьш1ения помехоустойчивости устройства за счет уменьшения эффекта распространения ошибок, в него введены элемент задержк, в торой элемент И, реверсивный счетчик, дешифратор и формирователь импульса

запрета коррекции, выход которого соединен с вторыми входами блока запрета коррекции, выход мультиплексора через элемент задержки соединен с первым входом второго элемента И, второй вход которого соединен с третьим выходом блока формирования тактовых импульсов, выходы первого и второго элементов И соединены соотПакет г/j 6 ошибок

liiS

Интерво/г анализа

h

1

Вых. дешифратора 13

Редактор Н.Горват

Составитель О.Тюрина

Техред А. Кравчук Корректор М.Пожо

Заказ 2666/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4ветственно с суммирующими и вычитающими входами реверсивного счетчика, выходы которого подключены соответственно к входам дешифратора, выход которого соединен с первым входом формирователя импульса запрета коррекции, второй вход которого подключен к четвертому выходу блока формирования тактовых импульсов.

фиг.1

CQ

Выход

фиг. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

Изобретение относится к технике передачи дискретной информации, Целью изобретения является повьппеиие помехоустойчивости устройства за. счет уменьшения эффекта распространения ошибок. Устройство содержит кодер 1 , формирователь 2 синдромной последовательности, анализатор 3 синдрома, блок 4 пороговых элементов, блок 5 запрета коррекции, корректор 6 ошибок, мультиплексор 7, блок 8 формирования тактовых импульсов, два элемента И 9 и П, элемент iO задержки, реверсивный счетчик 12, дешифратор 13, фор- Ь Шрователь 4 импульса запрета коррекции. 3 ил. (Л с Выход инсо N3 О 00 ел

| Пороговый декодер сверхточного кода | 1976 |

|

SU586571A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Clark G.C., Bibb Cain Т | |||

| Brror- correction coding for digital communications | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| РЕЛЬСОВАЯ ПЕДАЛЬ | 1920 |

|

SU290A1 |

| Kavehrach M | |||

| Implementation of a seltorthogonal convolutional codl used in satellite communications | |||

| - Electronic circuits and SustemSj May, 1979, vol | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-06-30—Публикация

1985-07-26—Подача