Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах повышенной надежности для хранения информации при воздействии ионизирующего излучения.

Целью изобретения является повышение надежности ячейки памяти.

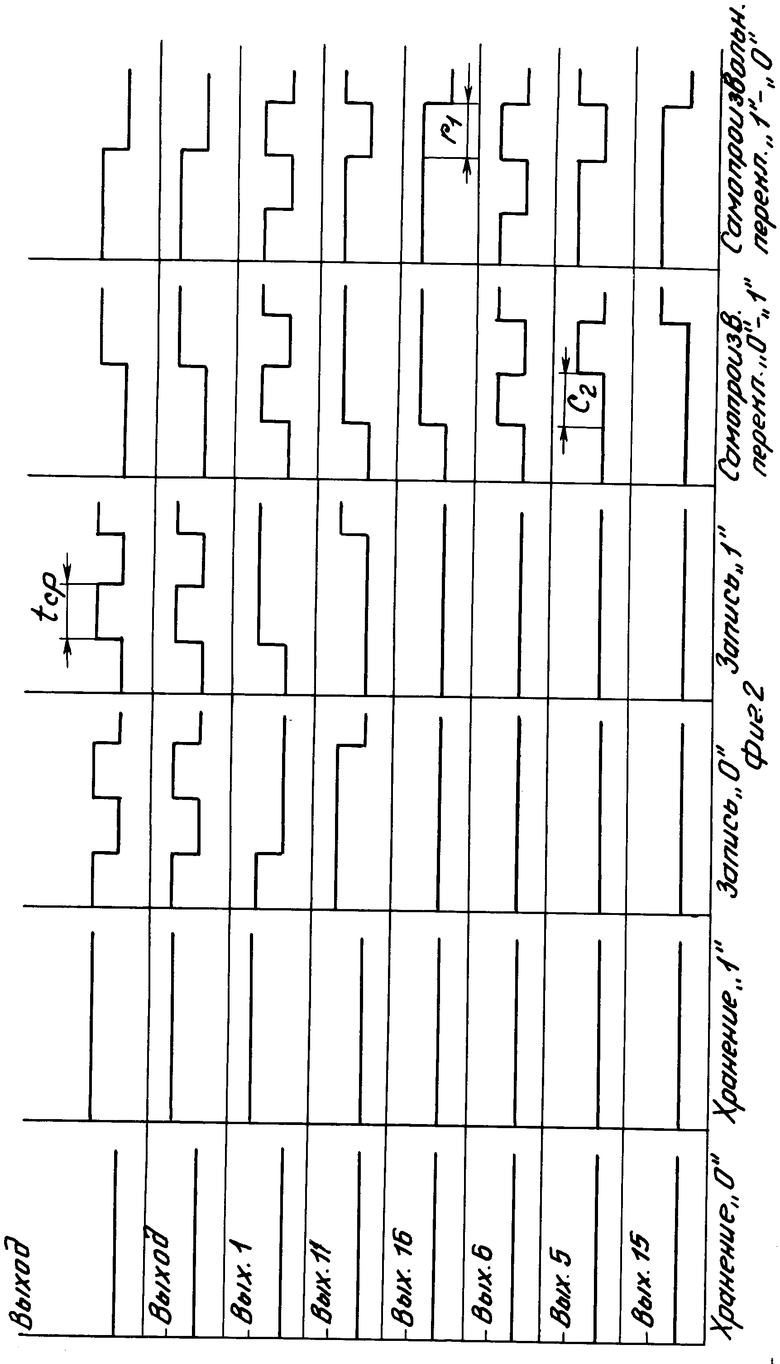

На фиг.1 представлена функциональная схема ячейки памяти; на фиг.2 приведены эпюры работы ячейки памяти в различных режимах, где tср - время срабатывания ячейки памяти.

Ячейка памяти содержит два канала, каждый из которых состоит из D-триггера 1, инвертора 2, элементов И 3, 4, мажоритарного элемента 5, элемента 6 задержки, элементов И 7, 8, 9, элемента ИЛИ 10, D-триггера 11, инвертора 12, элементов И 13, 14, мажоритарного элемента 15, элемента 16, элемента И 17.

Ячейка памяти работает следующим образом.

В режиме хранения информации на входы элементов И 3, 13 подается информация, которая записана в D-триггерах 1, 11 ячейки памяти. На элементы И 4, 14 подается инверсный сигнал хранимой информации. Мажоритарный элемент 5 при появлении стробирующего сигнала срабатывает и подает сигнал на тактовый вход D-триггеров 1, 11. При этом происходят считывание записанной информации и проверка хранившейся информации. Пройдя через элемент 6 задержки, сигнал задерживается на один такт и под действием стробирующего сигнала С1 подается на информационный вход триггера 1. С информационного выхода триггера 1 подается сигнал на элемент И 8, и под действием стробирующего сигнала С2 подается сигнал на элемент ИЛИ 10. Мажоритарный элемент 15 под действием стробирующего импульса С1 подает сигнал на тактовый вход триггера 11, который под действием этого импульса считывает или записывает информацию, находящуюся на информационном входе ячейки памяти. Инвертор 12 инвертирует сигнал, находящийся на входе триггера 11, и подает инверсный сигнал на элемент И 13. Элемент 16 задержки задерживает сигнал на один такт. Выход элемента 16 задержки соединен с входом элемента И 17. Под действием стробирующего сигнала С2 с выхода элемента И 17 подается сигнал на информационный выход триггера 11. Информационный выход триггера 11 соединен с входом элемента И 9, который под действием стробирующего сигнала С1 посылает сигнал на элемент ИЛИ 10. Выход элемента ИЛИ 10 является логическим выходом ячейки памяти.

В случае искажения хранившейся информации в триггерах на их информационные входы подается считанный сигнал, задержанный на один такт и вновь записанный в триггер, а в дальнейшем считанный с него. Сигнал подается на выход ячейки памяти, предварительно сравнившись с исходным импульсом. Данную операцию выполняют элементы 2, 3, 4, 12, 13, 14.

Ячейка памяти обладает повышенной надежностью: при воздействии ионизирующего излучения невозможно самопроизвольное переключение ячейки памяти из одного состояния в другое, так как при наличии сигналов, вызванных ионизирующим излучением на входах ячейки памяти, исключаются возможность реального прохождения сигналов и переключение триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2072567C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| Устройство коммутации для систем многоканального контроля и управления | 1985 |

|

SU1264206A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2051409C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2007031C1 |

| @ -Триггер | 1984 |

|

SU1234951A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах помехоустойчивого хранения информации. Задачей изобретения является хранение и достоверное считывание информации из ячейки памяти после воздействия ионизирующего излучения. Эта задача решается путем введения в схему ячейки памяти мажоритарных элементов 5, 15, элемента 6 задержки, инверторов 2, 12 и элементов И 3, 4, 7, 13, 14, 17. Посредством этих элементов исключается самопроизвольное переключение D-триггера, и информация, хранящаяся в триггерах не изменяется. 2 ил.

ЯЧЕЙКА ПАМЯТИ, содержащая элемент ИЛИ, два разряда, каждый из которых состоит из D-триггера и первого элемента И, первый вход которого соединен с прямым выходом D-триггера, информационные входы D-триггеров первого и второго разрядов соединены и являются информационным входом ячейки памяти, выходы первых элементов И первого и второго разрядов соединены с первым и вторым входами соответственно элемента ИЛИ, выход которого является выходом ячейки памяти, вторые входы первых элементов И первого и второго разрядов являются соответственно первым и вторым входами ячейки памяти, отличающаяся тем, что, с целью повышения надежности за счет увеличения стойкости к ионизирующим излучениям ячейки памяти, каждый разряд ячейки содержит мажоритарный элемент, инвертор, второй, третий и четвертый элементы И, элемент задержки, выход которого соединен с первым входом второго элемента И, выход которого соединен с информационным входом D-триггера, входом инвертора, первым входом третьего элемента И, второй вход которого соединен с инверсным выходом D-триггера, тактовый вход которого соединен с выходом мажоритарного элемента, первый вход которого соединен с выходом третьего элемента И, а второй вход - с выходом четвертого элемента И, первый вход которого соединен с выходом инвертора, а второй вход - с прямым выходом D-триггера и входом элемента задержки, вторые входы вторых элементов И первого и второго разрядов являются соответственно третьим и четвертым тактовыми входами ячейки памяти, третьи входы мажоритарных элементов первого и второго разрядов являются соответственно пятым и шестым тактовыми входами ячейки памяти.

| Ячейка памяти | 1985 |

|

SU1429170A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-11-30—Публикация

1991-02-12—Подача