Изобретение относится к цифровой технике и может быть использовано в вычислительной технике в цифровых ;системах управления.

Целью изобретения является повышение быстродействия ячейки памяти

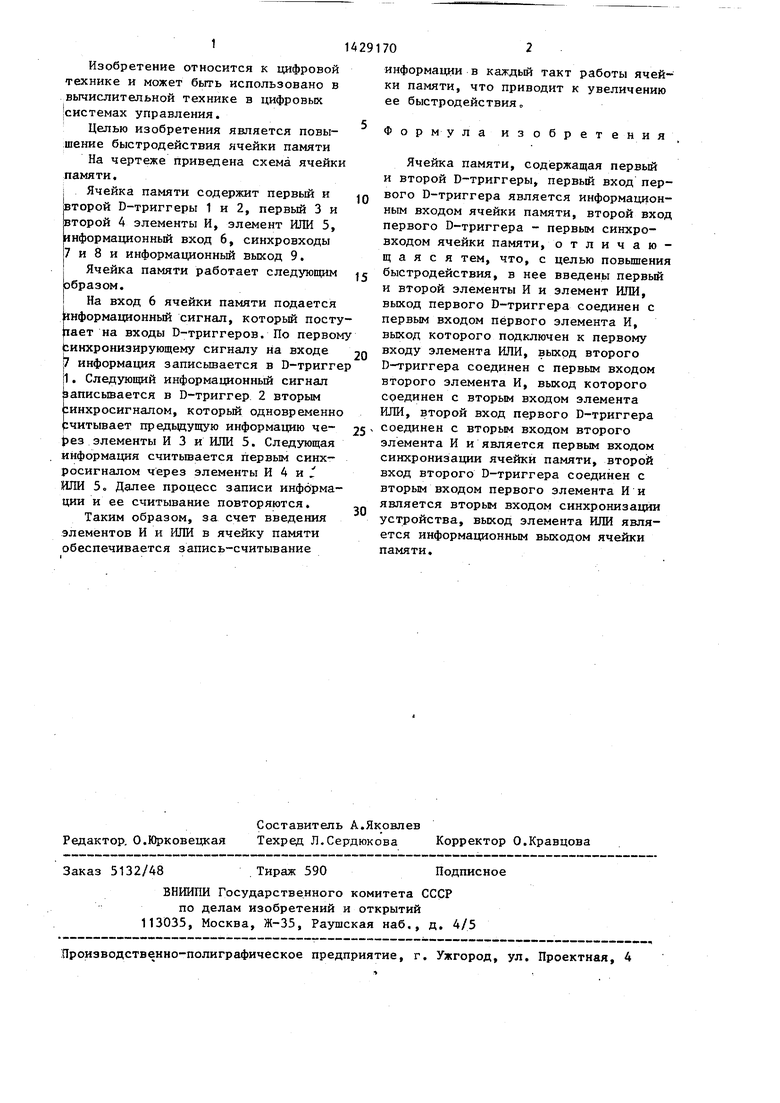

На чертеже приведена схема ячейк памяти,

i Ячейка памяти содержит первый и второй D-триггеры 1 и 2, первый 3 и второй 4 элементы И, элемент ИЛИ 5, информационный вход 6, синхровходы 7 и 8 и информаид онный выход 9. I Ячейка памяти работает следующим Ьбразом.

I На вход 6 ячейки памяти подается Информационный сигнал, который пост на входы D-триггеров. По перво синхронизирующему сигналу на входе |7 информация записьшается в D-тригг |l. Следующий информационный сигнал записьшается в D-триггер 2 вторым ;инхросигналом, который одновременн :читывает предьщущую информацию че- )ез элементы И 3 и ИЛИ 5. Следующая информация считьшается первым синхросигналом через элементы И 4 и ЩШ 5 Далее процесс записи информации и ее считывание повторяются.

Таким образом, за счет введения элементов И и ИЛИ в ячейку памяти обеспечивается запись-считывание

0

5

0

5

0

информации в каждый такт работы ячейки памяти, что приводит к увеличению ее быстродействия„

Формула изобретения,

Ячейка памяти, содержащая первый и второй D-триггеры, первый вход первого D-триггера является информационным входом ячейки памяти, второй вход первого D-триггера - первым синхро- входом ячейки памяти, о т л и ч а ю - щ а я с я тем, что, с целью повьшения быстродействия, в нее введены первый и второй элементы И и элемент ИЛИ, выход первого D-триггера соединен с первым входом первого элемента И, выход которого подключен к первому входу элемента ИЛИ, выход второго D-триггера соединен с первьм входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, второй вход первого D-триггера соединен с вторым входом второго элемента И и является первым входом синхронизации ячейки памяти, второй вход второго D-триггера соединен с вторым входом первого элемента И и является вторым входом синхронизации устройства, выход элемента ИЛИ является информационным выходом ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2199774C1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство цифровой задержки информации с контролем | 1988 |

|

SU1635225A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2097819C1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2006 |

|

RU2319192C2 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Устройство для формирования векторов на экране телевизионного индикатора | 1988 |

|

SU1506477A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

Изобретение относится к цифровой технике и может быть использовано в вычислительной технике в цифровых системах управления. Целью изобретения является повышение быстродействия устройства.. Поставленная цель достигается за счет введения элементов И 3, 4 и РШИ 5, что позволяет обеспечить запись-считьшание информации в каждый такт работы устройства. 1 ил.

| Дроздов Е.А | |||

| и др | |||

| Электронные цифровые вычислительные машины | |||

| - М.: Воениздат, 1968, с | |||

| Канальная печь-сушильня | 1920 |

|

SU230A1 |

| Алексенко А.Г | |||

| и др | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с | |||

| Поршень для воздушных тормозов с сжатым воздухом | 1921 |

|

SU188A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-07—Публикация

1985-12-29—Подача