Изобретение относится к вычислительной технике и технике связи, а именно к системам управления техническими средствами связи и предназначено для ввода управляющей информации.

Целью изобретения является повышение достоверности ввода информации.

Устройство позволяет, во-первых, определять длину (количество знаков (символов) в команде) сообщения - команды и, если она не соответствует заданной, то формируется сигнал ошибки, во-вторых, сверять конец команды на соответствие определенному знаку (символу), в-третьих, осуществлять проверку каждого символа в команде, при которой выявляется его соответствие заданному и, в случае несовпадения с заданным, формируется ошибка, а также обеспечивается распределение кодов команд по их классам (типам) в зависимости от их принадлежности к какой-либо подсистеме, например, обслуживания, обработки сообщений, статистики и т.д.

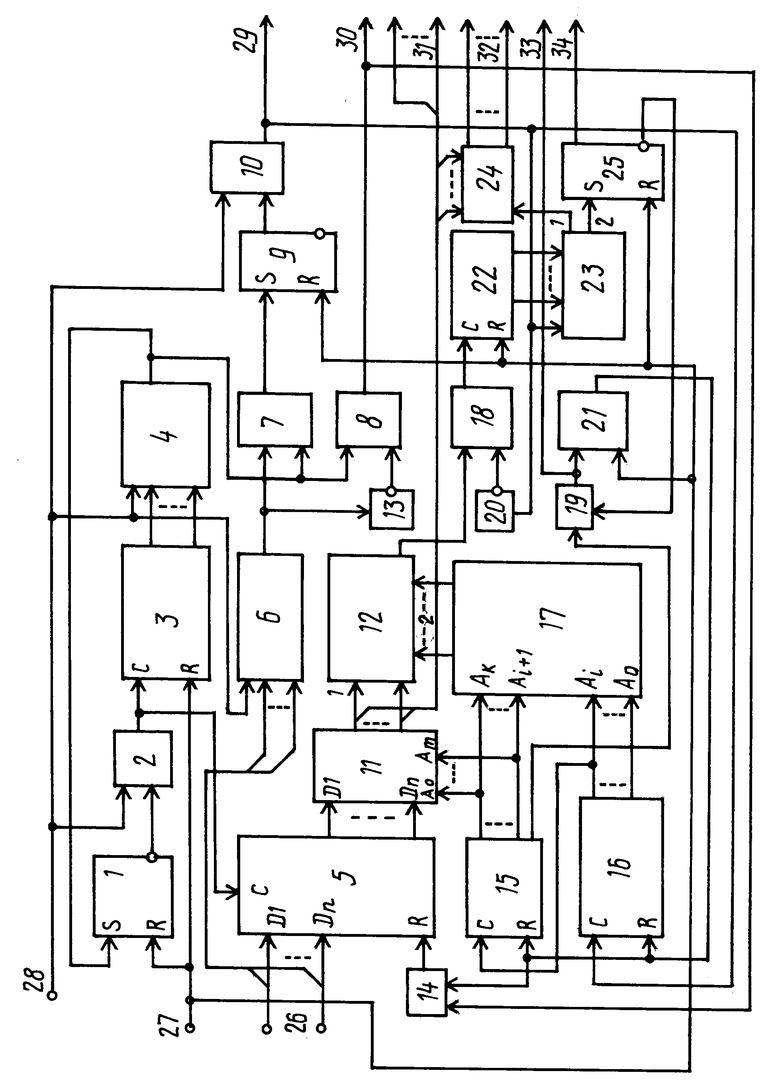

На чертеже представлена функциональная схема устройства для ввода команд управления.

Устройство содержит первый триггер 1, третий элемент И 2, первый счетчик 3, первый дешифратор 4, блок регистров 5, второй дешифратор 6, четвертый и первый элементы И 7,8, второй триггер 9, пятый элемент И 10, блок мультиплексоров 11, блок сравнения 12, первый элемент НЕ 13, первый элемент ИЛИ 14, третий и второй счетчики 15, 16, блок памяти 17 (постоянное запоминающее устройство), второй и шестой элементы И 18, 19, второй элемент НЕ 20, второй элемент ИЛИ 21, четвертый счетчик 22, третий и четвертый дешифраторы 23, 24 и третий триггер 25 (на чертеже обозначены). Входы и выходы устройства 26-34.

Блок регистров 5 содержит N, например 8 или 16 и т.д., восьмиразрядных регистров памяти, выполненных на регистрах 155 ТМ8, 155 ТМ2, у которых информационные (Do-D7) входы поразрядно объединены, а выходы регистров являются (по отдельности) выходами блока 5, входы синхронизации (С) регистров памяти подключены к выходам отдельного N-разрядного кольцевого регистра сдвига, выполненного, например, на последовательно включенных регистрах 155 ИР1, на вход(ы) синхронизации которого подается сигнал тактовой частоты (с выхода элемента И2), а в один из разрядов регистра сдвига, например, по сигналу сброса записывается логическая единица, которая движется по регистру под действием тактовых импульсов, входы сброса регистров памяти объединены и подключены через элементы НЕ (для согласования) к входу сброса блока 5.

К выходам дешифратора 6 подключены элементы НЕ, выходы которых объединены по схеме И и образуют полный 2 n дешифратор.

Устройство работает следующим образом.

После включения напряжения питания и подачи сигнала "Сброс" на вход 27 устройства его блоки с памятью (регистры, счетчики, триггеры) устанавливаются в исходное состояние.

На входы 26 устройства, а значит, и на информационные входы блока 5 поступает входная информация в параллельном коде посимвольно. Эта входная информация (команды управления или ответы на них) записывается в блок 5 с помощью импульсов тактовой частоты, подаваемой на вход 28 устройства.

Триггер 1 разрешает прохождение импульсов частоты через элемент И 2 на счетчик 3. Последний отсчитывает количество поступающих символов и, если оно не меньше заданного значения, то дешифратор 4 (длины кода команды) сформирует на своем выходе сигнал, который поступит на одни входы элементов И 7, 8. На другие входы этих элементов подается стробирующий сигнал (прямой и инверсный соответственно) с выхода дешифратора 6. Этот дешифратор 6 выделяет разделительный символ, например, "Пробел", означающий конец кода команды.

Таким образом, если длина кода или число его знаков (символов), содержащихся в команде, соответствует заданному значению, то с выхода элемента И 7 будет сформирован сигнал на триггер 9, который перейдет в состояние логической единицы и разрешит прохождение импульсов тактовой частоты через элемент И 10. Это означает, что сигнал (код) команды был в данном случае полным.

Если же число символов в команде не соответствует заданному, то с выхода элемента И 7 сигнала не будет, а он появится на выходе элемента И 8. Это означает, что сигнал (код) команды был неполным. Триггер 9 останется в исходном (нулевом) состоянии и не разрешит прохождение импульсов через элемент И 10. С выхода элемента И 8 на выход 2 устройства, в этом случае будет выдан сигнал "Ошибка полноты", а устройство запретит дальнейшую обработку принимаемой информации. При этом сигнал с выхода элемента И 8 поступит через элемент ИЛИ 14 на вход сброса блока 5, который обнулится.

В случае успешной проверки кода команды на полноту, производится проверка содержимого кода команды на корректность.

В этом случае триггер 9 разрешает прохождение импульсов частоты через элемент И 10 на входы счетчиков 16 и 22.

Счетчик 16 формирует по очередности адресные коды на входы блока памяти (ПЗУ) 17.

С выходов ПЗУ 17 считываются хранящиеся в нем коды символов, соответствующие первому знакоместу для всех допустимых команд управления (или ответов на них), на одни из входов блока 12. На других входах блока 12 присутствует в это время код первого по знакоместу символа, принятого и записанного в блоке 5. Поскольку триггер 1 по сигналу, полученному с выхода дешифратора 4, переключился в состояние логической единицы, то под действием сигнала логического нуля, подаваемого с инверсного выхода триггера 1 на вход элемента И 2, будет запрещено прохождение импульсов частоты на вход синхронизации блока 5.

Информация о команде управления хранится в блоке 5 и считывается из него посимвольно с помощью счетчика 15 и блока мультиплексоров 11. Счетчик 15 формирует новый адрес на блоки 11 и 17 после того, как счетчик 16 "прокрутит" (переберет) адреса всех символов первого знакоместа в команде. В результате с выходов блока 11 на входы блоков 12 и 22 и на выходы 1 устройства выдается новый код символа после того, как будут проверены с помощью счетчика 16 всевозможные значения символов, коды которых хранятся в виде таблицы в ПЗУ 17.

При этом с выходов дешифратора 24 на выходы 6 устройства формируются сигналы-признаки в соответствии с принятой в системе классификацией (типом) команд, содержащихся, например, в первом знаке команды.

При совпадении кодов символов с выхода блока 12 через элемент И 18, стробируемый импульсами инверсной частоты, на счетчик 22 поступает импульс. Число импульсов сравнения должно соответствовать числу (количеству) символов в коде команды.

Если число таких сравнений будет не менее заданного (оно определяется дешифратором 23), то с выхода блока 23 на триггер 25 сформируется сигнал. Триггер 25 переключится в состояние логической единицы и с его прямого выхода на выход 4 устройства будет выдан сигнал готовности продолжать работу дальше. Это значит, что код принятой команды прошел успешную проверку не только на полноту, но и на корректность, то есть соответствие кодов символов требуемым.

Если же число отсчитанных импульсов сравнения счетчиком 22 окажется меньше заданного, то это означает, что на устройство поступила ложная информация или некорректная команда. При этом с одиночного выхода (последнего разряда) счетчика 15 через элемент И 19, открытый сигналом логической единицы с инверсного плеча триггера 25, выдается на выход 3 устройства сигнал "Ошибка корректности".

Этот сигнал поступит через элемент ИЛИ 21 на входы сброса счетчиков 15, 16 и через элемент ИЛИ 14 на вход сброса блока 5. Указанные блоки обнуляются и устройство готово к новому циклу приема команд управления, начинающегося сигналом "Сброс" по входу 1 устройства.

На этом проверка принятой команды на полноту и корректность завершается.

В случае правильного ввода кода команды при проверке на его полноту с выхода элемента И 10 на выход 5 устройства будет выдаваться последовательность тактовых импульсов, с помощью которых можно считывать посимвольно код команды или ответного сообщения на выходах 1 устройства. При этом на выходах 6 устройства формируются сигналы - "признаки", означающие принадлежность команды или сообщения определенной подсистеме, например, обслуживания, обработки информации, статистики и т.д., в соответствии с принятой классификацией (типом) команд.

Таким образом, предлагаемое устройство позволит повысить достоверность принимаемой или вводимой из другого устройства информации (в частности команд управления) не только в условиях появления ошибок из-за электромагнитных помех, но также вследствие ошибочных действий человека - оператора, а также расширить функциональные возможности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для ввода информации в калькулятор | 1990 |

|

SU1791807A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1991 |

|

RU2024217C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОМАНД УПРАВЛЕНИЯ ДВУХПОЗИЦИОННЫМИ ОБЪЕКТАМИ | 2002 |

|

RU2244344C2 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

Использование: ввод управляющей информации в системах управления техническими средствми. Сущность: устройство содержит три триггера, шесть элементов И, четыре счетчика, блок регистров, блокк мультиплексоров, блок сравнения, четыре дешифратора, два элемента НЕ, два элемента ИЛИ, блок памяти. 1 ил.

УСТРОЙСТВО ДЛЯ ВВОДА КОМАНД УПРАВЛЕНИЯ, содержащее блок регистров, первый счетчик, блок памяти, блок сравнения, первый триггер, первый и второй элементы И, первый и второй элементы ИЛИ, первый элемент НЕ, информационные входы блока регистров являются информационными входами устройства, первый вход первого элемента И соединен с выходом первого элемента НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход блока сравнения соединен с первым входом второго элемента И, отличающееся тем, что, с целью повышения достоверности вводимой информации, в устройство введены блок мультиплексоров, второй и третий триггеры, третий, четвертый, пятый и шестой элементы И, второй элемент НЕ, первый, второй, третий и четвертый дешифраторы, причем выход первого триггера соединен с первым входом третьего элемента И, выход которого соединен со счетным входом первого счетчика и входом сдвига блока регистров, выходы которого соединены с информационными входами блока мультиплексоров, выходы первого счетчика соединены с информационными входами первого дешифратора, выход которого соединен с вторыми входами первого и четвертого элементов И и установочным входом первого триггера, информационные входы второго дешифратора объединены с информационными входами блока регистров, выход второго дешифратора соединен с первым входом четвертого элемента И и входом первого элемента НЕ, выход четвертого элемента И соединен с установочным входом второго триггера, выход которого соединен с первым входом пятого элемента И, вторые входы третьего и пятого элементов И и входы синхронизации первого и второго дешифраторов являются тактовым входом устройства, выход пятого элемента И соединен с входом второго элемента НЕ, стробирующим входом третьего дешифратора, счетным входом второго счетчика и является тактовым выходом устройства, выходы второго счетчика соединены с адресными входами первой группы блока памяти, один из выходов второго счетчика соединен со счетным входом третьего счетчика, выходы группы которого соединены с адресными входами второй группы блока памяти и адресными входами блока мультиплексоров, выходы которого соединены с входами первой группы блока сравнения, информационными входами четвертого дешифратора и являются первыми информационными выходами устройства, выходы блока памяти соединены с входами второй группы блока сравнения, выход третьего счетчика соединен с первым входом шестого элемента И, выход которого соединен с первым входом второго элемента ИЛИ и является выходом ошибки корректности команды устройства, выход второго элемента ИЛИ соединен с входами сброса второго и третьего счетчиков и вторым входом первого элемента ИЛИ, выход которого соединен с входом сброса блока регистров, входы сброса первого, второго и третьего триггеров, первого и четвертого счетчиков и второй вход второго элемента ИЛИ являются входом сброса устройства, выход второго элемента НЕ соединен с вторым входом второго элемента И, выход которого соединен со счетным входом четвертого счетчика , выходы которого соединены с информационными входами третьего дешифратора, первый выход которого соединен со стробирующим входом четвертого дешифратора, выходы которого являются информационными выходами второй группы устройства, второй выход третьего дешифратора соединен с установочным входом третьего триггера, прямой выход которого является выходом готовности устройства, инверсный выход третьего триггера соединен с вторым входом шестого элемента И, выход первого элемента И является выходом ошибки полноты команды устройства.

| Способ изготовления фотополимерных печатных форм | 1987 |

|

SU1418640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-12-15—Публикация

1991-08-29—Подача