Изобретение относится к электросвязи и может быть использовано в цифровых междугородних телефонных станциях или узлах коммутации, в частности в коммутационном оборудовании с временной цифровой коммутацией.

Целью изобретения является расширение функциональных возможностей, а именно: обеспечение измерения различных скоростей передачи цифровой информации одновременно в N дискретных каналах связи.

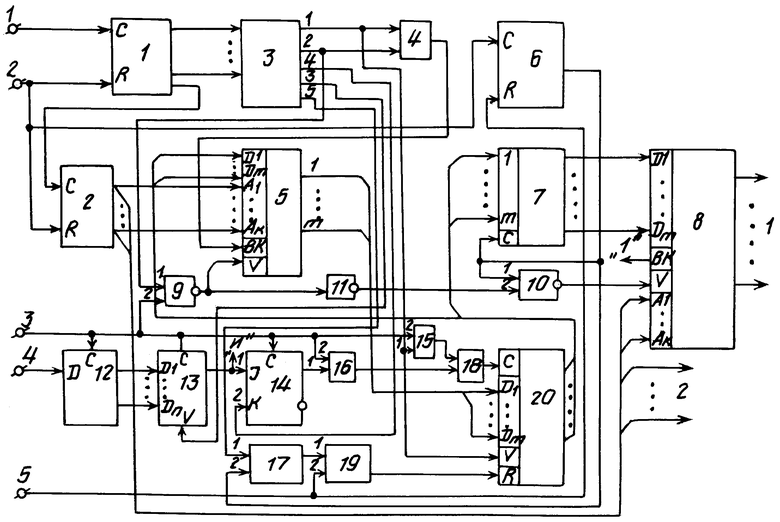

На чертеже представлена электрическая функциональная схема устройства для измерения скоростей передачи цифровой информации.

Устройство для измерения скоростей передачи цифровой информации содержит первый и второй счетчики 1 и 2, первый дешифратор 3, первый элемент ИЛИ 4, первое оперативное запоминающее устройство (ОЗУ) 5, третий счетчик 6, второй дешифратор 7, второе ОЗУ 8, первый и второй элементы И-НЕ 9 и 10, элемент НЕ 11, первый и второй регистры 12 и 13, IK-триггер 14, первый, второй и третий элементы И 15, 16 и 17, второй и третий элементы ИЛИ 18, 19 и четвертый счетчик 20.

Вход 1 устройства (вход первой тактовой частоты) является счетным входом счетчика 1, выходы которого подключены к входам дешифратора 3.

Выходы 1 и 2 дешифратора 3 подключены к входам элемента ИЛИ 4, выход которого подключен к входу выбора кристалла (ВК) ОЗУ 5.

Выход 3 дешифратора 3 соединен с входом управления регистра 13, выход которого подключен к первому входу управления триггера 14, второй вход управления которого соединен с выходом 4 дешифратора 3, а выход - с входом 1 элемента И 16.

Вход 2 устройства (цикловой частоты) объединен с входом сброса последовательно соединенных счетчиков 1 и 2 и счетным входом счетчика 6.

Второй выход дешифратора 3 подключен к входу 1 элемента И-НЕ 9. Отдельный выход счетчика 1 соединен со счетным входом счетчика 2.

Выходы счетчика 2 подключены к адресным входам ОЗУ 5, выходы которого подключены к информационным входам счетчика 20.

Выход 5 дешифратора 3 подключен к входу 1 элемента И 17, выход которого соединен с входом 1 элемента ИЛИ 19, выход которого подключен к входу сброса счетчика 20.

Выход 1 дешифратора 3 подключен к входу 1 элемента И 15.

Вход 3 устройства (второй тактовой частоты) подключен к входам синхронизации регистров 12, 13, триггера 14, входу 2 элемента И-НЕ 9 и вторым входам элементов И 15, 16, выходы которых подключены к входам элемента ИЛИ 18, выход которого подключен к счетному входу счетчика 20.

Вход 4 устройства (информационный) является входом информации регистра 12, выходы которого подключены к информационным входам регистра 13.

Выход счетчика 6 объединен с входом разрешения дешифратора 7, входом 1 элемента И-НЕ 10 и входом 2 элемента И 17.

Выходы счетчика 20 подключены к входам дешифратора 7 и информационным входам ОЗУ 5, выходы ОЗУ 8 являются первыми (информационными) выходами устройства. Выходы дешифратора 7 соединены с входами ОЗУ 8. Выходы счетчика 2 подключены к адресным входам ОЗУ 8 и являются адресными выходами устройства.

Выход элемента И-НЕ 9 подключен к входу режима ОЗУ 5 и через элемент НЕ 11 - к входу 2 элемента И-НЕ 10, выход которого соединен с входом управления ОЗУ 8. Вход управления счетчика 20 подключен к выходу 1 дешифратора 3. Вход 5 устройства подключен к входу 2 элемента ИЛИ 19 и входу сброса счетчика 6.

Блоки и элементы устройства могут быть выполнены, например, на микросхемах 155 (или К 133), К 531, К 530 серий, счетчики 1 и 2 (4-х разрядные, двоичные) - на микросхемах 155ИЕ7, дешифратор 3 - на микросхемах 155 ИДЗ и 155 ЛН1 элементы ИЛИ 4, 18, 19 - на элементах микросхем 155 ЛЕ5 и 155 ЛН1. ОЗУ 5 и 8 (m - разрядное) выполнены на микросхемах 155 РУ2 (или К 53 ОРУ 2) и 155 ЛН1, подключенных к инверсным входам управления (режима) и выходам. Счетчик 6 - это двоично-десятичный счетчик, выполненный на микросхемах 155 ИЕ2.

Дешифратор 7 построен на микросхемах - дешифраторах 155 ИДЗ, к инверсным выходам которых подключены элементы 155ЛН1, а соответствующие их выходы - к элементам 155 ЛИ2. Элементы И-НЕ 9, 10 - это элементы микросхем 155ЛАЗ. Элемент НЕ - это элемент 155ЛН1; регистр 12 выполнен на микросхемах 155ТМ7. Регистр 13 выполнен на микросхемах 155ИР1. Триггер 14 - это триггер К531ТВ10. Элементы И 15, 16, 17 - это элементы микросхем 155ЛИ2. Счетчик 20 построен на последовательно соединенных счетчиках-микросхемах 155ИЕ7.

Устройство работает следующим образом.

После включения напряжения питания обнуляются счетчики 6 и 20 сигналом сброса, а при поступлении импульса цикловой частоты (8 кГц) длительностью один период тактовой частоты (Т1=Т2=2048 кГц), обнуляются счетчики 1 и 2. Под действием импульсов, поступающих по входу 1 устройства на счетчик 1, последний отсчитывает 16 временных интервалов, каждый из которых равен периоду частоты 2048 кГц.

Дешифратор 3 выделяет импульсы временных интервалов: на выходе 1 - первый, на выходе 2 - восьмой, на выходе 3 - шестнадцатый, на выходе 4 - девятый, а на выходе 5 - одиннадцатый.

Счетчик 2 формирует (по приходу каждого импульса на его счетный вход) код адреса временных интервалов - каналов (ВК), число которых соответствует числу канальных интервалов группового тракта (ГТ).

На вход 4 устройства поступает информационная последовательность, каждый бит которой записывается последовательно в регистр 12 с помощью импульсов тактовой частоты Т2, синхронных, но сдвинутых на полпериода относительно импульсов тактовой частоты Т1.

После записи входной информации в регистр 12 по переднему фронту тактовых импульсов Т2 она переписывается в параллельном виде в регистр 13. Перезапись осуществляется по заднему фронту (cпаду) импульса Т2 при одновременном наличии сигнала на управляющем входе регистра 13, формируемого с выхода 3 дешифратора 3.

Накопление порции информации в регистре 12 и перезапись ее в регистр 13 после накопления позволяют осуществлять ее независимую обработку за время длительности канальных интервалов, содержащихся в цикле ГТ.

Из регистра 13 записанная информация выдается по заднему фронту импульсов Т2 на первый логический вход триггера 14 (а также на выход устройства при необходимости).

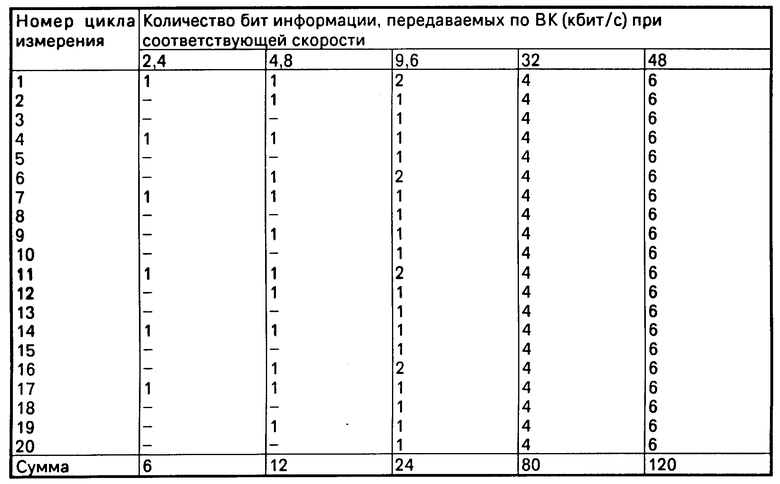

При появлении на входе триггера 14 "флажка", который представлен всегда битом "логическая единица", триггер 14 переключается по заднему фронту импульса Т2 в единичное состояние, а по сигналу с выхода 4 дешифратора 3 - в нулевое состояние. За "флажком" следуют биты информации, значения которых соответствуют значениям бит в дискретном канале связи, а распределение и количество бит в каждом ВК зависят от скорости передачи информации (см. таблицу).

Дешифратор 7 декодирует это число принятых бит, соответствующее номиналу скорости передачи информации в дискретном канале связи, и выдает его на информационные входы ОЗУ 8. В это ОЗУ осуществляется запись значений по каждому из ВК при совпадении сигнала, сформированного с выхода 2 дешифратора 3, с импульсом тактовой частоты Т2 на элементе И-НЕ 9 и сигналом с выхода счетчика 6 на элементе И-НЕ 10.

Обнуление счетчика 20 производится при совпадении импульса с выхода 5 дешифратора 3 и сигнала с выхода счетчика 6 на элементе И 17.

Поскольку измерение скоростей передачи цифровой информации происходит одновременно (за интервал измерения) по N дискретным каналам связи за счет поочередного накопления бит информации за интервал измерения, например, равного 20 циклам измерения (см. таблицу), то при этом необходимо сохранять ранее принятые порции бит из ОЗУ 5, на информационные (Д) входы которого подается код числа принятых бит информации с выходов счетчика 20, а на адресные входы - код адреса с выходов счетчика 2. Сигнал на вход выбора кристалла (ВК) ОЗУ 5 формируется с выходов 1 и 2 дешифратора 3 через элемент ИЛИ 4, а сигнал режима (записи) ОЗУ 5 выдается с выхода элемента И-НЕ 9.

Перезапись информации с выходов ОЗУ 5 на информационные входы счетчика 20 (для временного хранения и дальнейшей дешифрации за интервал измерения) производится по сигналу с выхода элемента ИЛИ 18 при совпадении сигнала, формируемого с выхода 1 дешифратора 3 и импульса Т2 на элементе И 15.

Считывание измеренных значений скоростей можно произвести из ОЗУ 8 (в режиме чтения) по выходам 1 устройства, на выходах 2 которого формируется код адреса соответствующего временного канала, номер которого идентифицирован с номером дискретного канала связи.

Таким образом предлагаемое устройство позволит измерять скорости передачи (приема) цифровой информации одновременно (за интервал измерения) по N дискретным каналам связи независимо от соотношения значений и номинала скоростей в диапазоне от 2,4 до 48 кбит/c.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для приема цифровых сигналов | 1990 |

|

SU1734240A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2011 |

|

RU2455672C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СОСТОЯНИЯ И УПРУГОДИССИПАТИВНЫХ СВОЙСТВ ПОВЕРХНОСТЕЙ ТРЕНИЯ | 1992 |

|

RU2036464C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

Использование: в электросвязи, цифровых телефонных станциях или узлах коммутации, в частности в коммутационном оборудовании с временной цифровой коммутацией. Сущность изобретения: устройство состоит из четырех счетчиков 1, 2, 6, 20, двух дешифраторов 3, 7, трех элементов ИЛИ 4, 18, 19, двух оперативно-запоминающих устройств 5, 8, двух элементов И - НЕ 9, 10, одного элемента НЕ 11, двух регистров 12, 13, одного JK-триггера 14, трех элементов И 15, 16, 17. Устройство обеспечивает расширение функциональных возможностей путем обеспечения измерения различных скоростей передачи цифровой информации одновременно по N дискретным каналам связи. 1 ил.

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее первый, второй, третий и четвертый счетчики, первое оперативно-запоминающее устройство, первый регистр, первый, второй, третий элементы И, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения измерения различных скоростей передачи цифровой информации одновременно по N дискретным каналам связи, в него введены второе оперативно-запоминающее устройство (ОЗУ), первый и второй элементы И - НЕ, элемент НЕ, первый, второй и третий элементы ИЛИ, первый и второй дешифраторы, второй регистр и JK-триггер, причем первый вход устройства, являющийся входом первой тактовой частоты, соединен со счетным входом первого счетчика, отдельный выход которого соединен со счетным входом второго счетчика, вход сброса которого, объединенный с входом сброса первого счетчика, подключен к второму входу устройства, являющемуся входом цикловой частоты, причем третий вход устройства, являющийся входом второй тактовой частоты, соединен с входами синхронизации первого и второго регистров и JK-триггера, при этом четвертый вход устройства является информационным входом первого регистра, информационные выходы которого соединены с соответствующими информационными входами второго регистра, выход которого подключен к первому управляющему входу JK-триггера, выход которого соединен с первым входом второго элемента И, а первый вход первого элемента И, объединенный с управляющим входом четвертого счетчика и первым входом первого элемента ИЛИ, соединен с первым выходом первого дешифратора, входы которого подключены к соответствующим выходам первого счетчика, при этом второй выход первого дешифратора соединен с вторым входом первого элемента ИЛИ и с первым входом первого элемента И - НЕ, второй вход которого, подключенный к входу второй тактовой частоты устройства, соединен с вторыми входами первого и второго элементов И, выходы которых являются соответственно первым и вторым входами второго элемента ИЛИ, выход которого подключен к счетному входу четвертого счетчика, информационные входы которого соединены с соответствующими выходами первого ОЗУ, адресные входы которого подключены к соответствующим выходам второго счетчика и к соответствующим адресным входам второго ОЗУ, а также к адресным выходам устройства, а информационные входы второго ОЗУ соединены с соответствующими выходами второго дешифратора, входы которого подключены к соответствующим информационным входам первого ОЗУ и к выходам четвертого счетчика, вход сброса которого подключен к выходу третьего элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, а второй вход подключен к пятому входу устройства и к входу сброса третьего счетчика, счетный вход которого соединен с входом сброса второго счетчика, причем третий, четвертый и пятый выходы первого дешифратора соединены соответственно с входами управления второго регистра, JK-триггера и с первым входом третьего элемента И, второй вход которого соединен с выходом третьего счетчика, объединенного с входом разрешения второго дешифратора и первым входом второго элемента И - НЕ, второй вход которого подключен к выходу элемента НЕ, вход которого соединен с выходом первого элемента И - НЕ, объединенного с входом режима первого ОЗУ, при этом вывод первого элемента ИЛИ подключен к входу выбора кристалла первого ОЗУ, а информационными выходами устройства являются соответствующие выходы второго ОЗУ, вход управления которого подключен к выходу второго элемента И - НЕ, а вход выбора кристалла второго ОЗУ подключен к источнику сигнала "Лог. 1".

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1325724A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-11-30—Публикация

1991-05-12—Подача