Устройство относится к электросвязи, точнее к системам приемопередачи данных, и может быть использовано в групповых устройствах защиты от ошибок, групповых устройствах приема дискретной информации.

Известно многоканальное устройство для передачи и приема дискретной информации, содержащее согласующие блоки, переключатель передачи, блок управления, переключатель приема, анализатор отбоя, блок сопряжения с линией, приемник кода, распределитель, кодек кодонезависимых каналов, кодек кодозависимых каналов, оперативный запоминающий блок, формирователь адреса, буферный блок, селектор вызова, блока памяти с произвольной выборки, опознаватель занятости, формирователь сигнала момента анализа и блок анализа и блокировки [1].

Недостатками этого устройства являются сложность - большие аппаратурные затраты, низкое быстродействие - невозможность декодирования принимаемой информации при высоких скоростях в каналах связи.

Наиболее близким по технической сущности к заявляемому является многоканальный декодер, содержащий генератор тактовых импульсов, счетчик цикла декодирования, распределитель каналов (счетчик), входной коммутатор, декодирующий блок, дешифратор импульса записи, сумматор, оперативные запоминающие устройства и коммутатор адресов записи [2].

Недостатками этого декодера являются низкое быстродействие декодирования информации, принимаемой одновременно по N каналам, большие аппаратурные затраты (ОЗУ на каждый канал) и невозможность декодирования информации при ее приеме на некратных скоростях от независимых источников.

Целью изобретения является повышение быстродействия устройства.

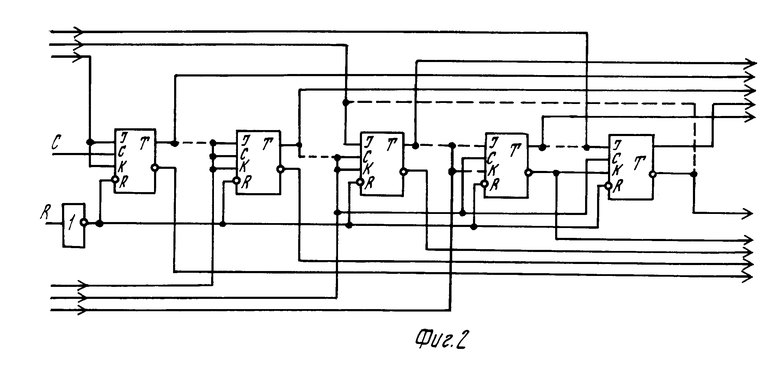

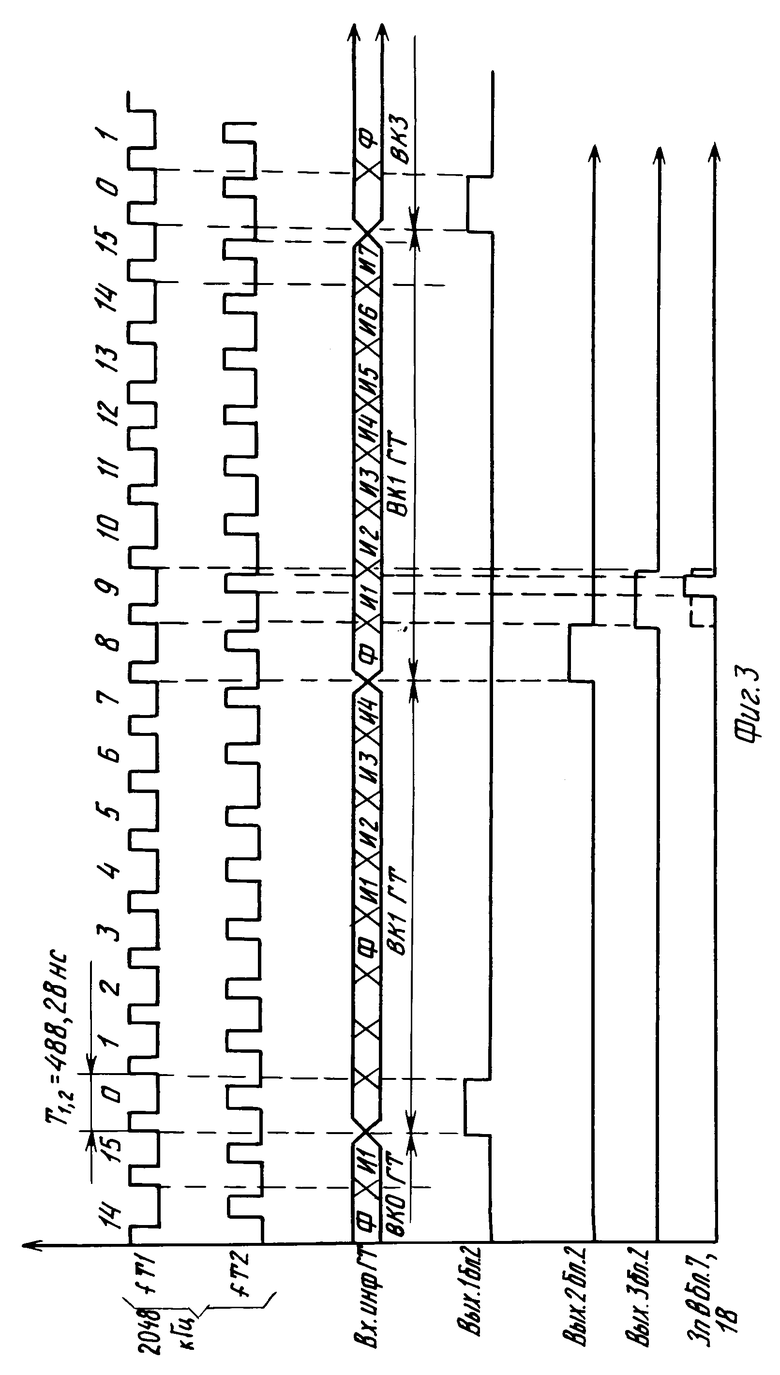

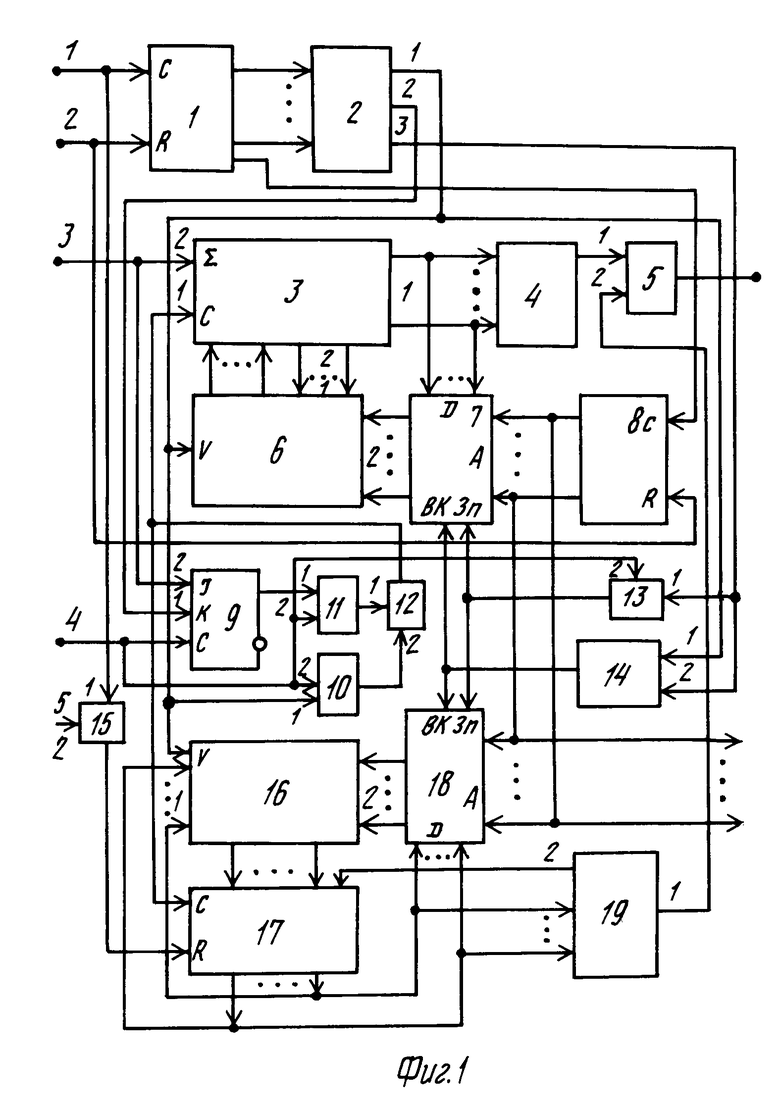

На фиг. 1 представлена электрическая функциональная схема устройства для многоканального декодирования; на фиг. 2 - электрическая функциональная схема третьего счетчика (длины последовательности); на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит первый счетчик 1 (временных интервалов), первый дешифратор 2, декодер 3 (декодирующий блок), второй дешифратор 4, третий элемент 5, первый мультиплексор 6, ОЗУ 7, второй счетчик 8 (адресный), IK-триггер 9, первый и четвертый элементы И 10 и 11, второй элемент ИЛИ 12, второй элемент И 13, первый элемент ИЛИ 14, пятый элемент И 15, второй мультиплексор 16, третий счетчик 17 (длины последовательности), блок 18 оперативной памяти и третий дешифратор 19.

Декодер 3 представляет собой набор отдельных D-триггеров и сумматоров по модулю два (полусумматоров), которые подключаются по известным правилам построения цифровых декодеров, связи (соединения) в которых образуются в соответствии с видом циклического полинома (многочлена), степень которого соответствует количеству разрядов регистра сдвига, выполненного на D-триггерах.

Счетчик 17 (фиг. 2) выполнен на отдельных IK-триггерах, к объединенным между собой входам обнуления которых подключен элемент НЕ. Входы и выходы триггеров проключаются с помощью мультиплексора 16.

Устройство работает следующим образом.

На первый (тактовый) вход устройства непрерывно поступает последовательность тактовых импульсов Т 1 с частотой 2048 кГц (фиг. 3).

После обнуления счетчиков 1 и 8 импульсом цикловой частоты (8 кГц), подаваемой на второй вход обнуления устройства, счетчик 1 отсчитывает циклически 16 временных интервалов, каждый из которых равен периоду частоты 2048 кГц. Счетчик 8 после прихода на его счетный вход каждого шестнадцатого импульса с выхода счетчика 1 формирует адрес (в двоичном коде) временного канала (ВК), число которых соответствует N-числу (нечетных или четных) канальных интервалов группового тракта.

В течение длительности каждого ВК на выходах дешифратора 2 циклически формируются соответствующие сигналы: на первом выходе - первый (нулевой) по счету временной интервал, на втором выходе - восьмой, а на третьем выходе - девятый (фиг. 3).

На третий (информационный) вход устройства поступает информационная последовательность группового тракта, содержащая биты информации нечетных (или четных) канальных интервалов. Она сопровождается (синхронизируется) последовательностью тактовых импульсов Т2, поступающей на четвертый (тактовый) вход устройства. Тактовые импульсы частоты Т2 (2048 кГц) идентичны Т1 по длительности, но сдвинуты во времени и не перемежаются между одной и другой последовательностями.

Информационная последовательность с третьего входа устройства поступает на информационный вход декодера 3 и I-вход триггера 9. При появлении на I-входе триггера 9 "флажка", который всегда обозначен битом логическая "1", триггер 9 переключается по заднему фронту импульса Т2 в единичное состояние. В результате через элемент И 11 и элемент ИЛИ 12 разрешается прохождение импульсов Т 2 на счетный вход счетчика 17 и вход синхронизации декодера 3. По переднему фронту этих импульсов осуществляется запись порции информации в регистр (или триггеры) декодера 3, которая поступает за "флажком" в последовательном коде, а счетчик 17 отсчитывает количестчво битов (или длину) этой порции информации.

Значение битов в информационной последовательности ВК соответствуют значениям битов в соответствующем интервале времени в дискретном канале связи, а распределение и количество битов в данном ВК зависит от скорости приема информации. Так, например, при одном значении скорости (2400 бит/c) поступления информации в порции одного из ВК содержатся "флажок" и один бит информации, а при другом значении скорости (48000 бит/c) - "флажок" и семь битов информации.

До момента поступления информации в декодер 3 в него переписывается порция информации (для этого же ВК), хранящаяся в ОЗУ 7, а в счетчик 17 переписывается состояние (двоичный код), хранящееся в блоке 18. Эта операция производится под действием сигнала, сформированного на первом выходе дешифратора 2. Сигнал поступает на управляющие входы мультиплексоров 6 и 16 (для проключения информации из ОЗУ 7 и блока 18 соответственно) и через элемент ИЛИ 14 на вход выбора кристалла ОЗУ 7 и блока 18. При совпадении на элементе И 10 этого сигнала и тактового импульса Т 2 (по его переднему фронту) порция информации записывается в декодер 3. Выдача кода адреса ОЗУ 7 блока 18 для выборки (или записи) информации соответствующего ВК осуществляется с помощью счетчика 8.

Таким образом, к информации, переписанной из ОЗУ 7 в декодер 3, добавляется порция информации, поступившей на третий вход устройства, а в счетчике 17 записывается состояние (двоичное число), идентичное состояние счетчика в предыдущем цикле приема информации для этого же ВК.

Ограничение порции информации, поступившей на вход декодера 3, производится триггером 9 при подаче на его К-вход сигнала, сформированного с второго выхода дешифратора 2. При совпадении с этим сигналом во времени тактового импульса Т 2 (по его заднему фронту) триггер 9 переключается в нулевое состояние и запись информации в декодер 3 прекращается.

Затем информация, записанная в декодере 3 для данного ВК, переписывается в ОЗУ 7, а состояние счетчика 17 - в блок 18. Это осуществляется по сигналу, сформированному на третьем выходе дешифратора 2 через элемент ИЛИ 14 на вход выбора кристалла ОЗУ 7 и блока 18, и сигналу, поступившему одновременно на вход режима записи ОЗУ 7 и блока 18 с выхода элемента И 13, который получился при совпадении тактового импульса Т 2 с сигналом на третьем выходе дешифратора 2 (фиг. 3). На этом процедура обработки сигналов для одного ВК заканчивается и начинается формирование следующего ВК. При этом счетчик 8 меняет свое состояние и формирует на входы ОЗУ 7 блока 18 адрес следующего по порядку ВК.

После записи порций информации ОЗУ 7 и блок 18 по всем N ВК и перебора счетчиком 8 адресов всех ВК начинается новый цикл работы устройства. Длительность такого цикла равна периоду следования импульсов цикловой частоты 8 кГц. В результате в ОЗУ 7 накапливается информационная последовательность, в которой использовано избыточное кодирование с помощью циклического кода, например, 19, 10. Декодер 3 используется для обнаружения ошибок в принимаемой информации.

Счетчик 17 с помощью блока 18 и мультиплексора 16 формирует двоичный код числа, определяющего длину информационной последовательности. Это число выявляет дешифратор 19 и выдает сигнал на один из входов элемента И 5, на другой вход которого в случае отсутствия ошибки (т.е. равенства остатка нулю после декодирования блока информационной последовательности в декодере 3) формируется импульс с выхода дешифратора 4. В результате на выходе элемента И 5, а значит, на выходе устройства формируется сигнал подтверждения правильного приема информационного блока данного ВК, номер которого определяется кодом адреса, формируемым счетчиком 8 на адресные выходы устройства.

Счетчик 17 перед приемом каждого информационного блока обнуляется сигналом, формируемым с выхода элемента И 15 при совпадении сигнала (маркера, метки), означающего начало информационного блока (последовательности), с тактовым импульсом Т 1. Сигнал обнуления (маркера) подается на вход 5 устройства в начале каждого информационного блока (последовательности).

Таким образом, предлагаемое устройство позволяет выявлять ошибки (декодировать) в принимаемой информации независимо и одновременно в реальном масштабе времени по N дискретным каналам связи на скоростях 2400, 4800, 9600, 32000 и 48000 бит/с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема цифровых сигналов | 1990 |

|

SU1734240A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1991 |

|

RU2024217C1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство ввода-вывода с контролем ошибок и индикацией | 1989 |

|

SU1728866A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство для кодирования сигналов звукового вещания | 1990 |

|

SU1774500A1 |

Устройство относится к электросвязи, в частности к системам приемопередачи данных, и может быть использовано в групповых устройствах защиты от ошибок, групповых устройствах приема дискретной информации. Изобретение решает задачу повышение быстродействия декодирования информации. Устройство содержит три счетчика 1, 8, 17, декодер 3, три дешифратора 2, 4, 19, пять элементов И 5, 10, 11, 13, 15, триггер 9, два элемента ИЛИ 12, 14, два блока 7, 18 оперативной памяти и два мультиплексора 6, 16. 3 ил.

УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ, содержащее блоки оперативной памяти, первый счетчик, первый дешифратор и декодер, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй и третий счетчики, мультиплексоры, второй и третий дешифраторы, триггер, элементы И, элементы ИЛИ, первые выходы первого счетчика соединены с соответствующими входами первого дешифратора, первый выход которого соединен с первыми входами первого элемента ИЛИ и первого элемента И и управляющими входами мультиплексоров, выходы первого мультиплексора соединены с соответствующими первыми информационными входами декодера, первые и вторые выходы которого соединены с соответствующими первыми информационными входами первого мультиплексора, входами второго дешифратора и информационными входами первого блока оперативной памяти, выходы которого соединены с соответствующими вторыми информационными входами мультиплексора, второй и третий выходы первого дешифратора соединены соответственно с K-входом триггера, первым входом второго элемента И и вторым входом первого элемента ИЛИ, выход которого соединен с входами выбора кристалла первого и второго блоков оперативной памяти, второй выход первого счетчика соединен со счетным входом второго счетчика, выходы которого соединены с соответствующими адресными входами первого и второго блоков оперативной памяти и являются адресными выходами устройства, выходы второго мультиплексора соединены с первыми информационными входами третьего счетчика, выходы которого соединены с первыми информационными входами второго мультиплексора, соответствующими входами третьего дешифратора и информационными входами второго блока оперативной памяти, выходы которого соединены с вторыми информационными входами второго мультиплексора, выходы второго и третьего дешифраторов соединены соответственно с первым и вторым входами третьего элемента И, выход которого является информационным выходом устройства, прямой выход триггера соединен с первым входом четвертого элемента И, выход которого и выход первого элемента И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с синхровходами декодера и третьего счетчика, выход второго элемента И соединен с входами записи блоков оперативной памяти, выход пятого элемента И - с входом обнуления третьего счетчика, второй выход третьего дешифратора соединен с вторым информационным входом третьего счетчика, счетный вход первого счетчика и первый вход пятого элемента И объединены и являются первым входом устройства, входы обнуления первого и второго счетчиков являются вторым входом устройства, второй информационный вход декодера и J-вход триггера объединены и являются третьим входом устройства, C-вход триггера и вторые входы первого, второго и четвертого элементов И объединены и являются четвертым входом устройства, второй вход пятого элемента И - пятым входом устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальный декодер | 1979 |

|

SU799156A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-10-30—Публикация

1990-07-02—Подача