Изобретение относится к вычислительной технике, в частности к цифровой обработке радио,- гидро- и звуколокационных сигналов, и может быть применено при построении быстродействующих Фурье-процессоров.

Цель предлагаемого изобретения - повышение быстродействия устройства.

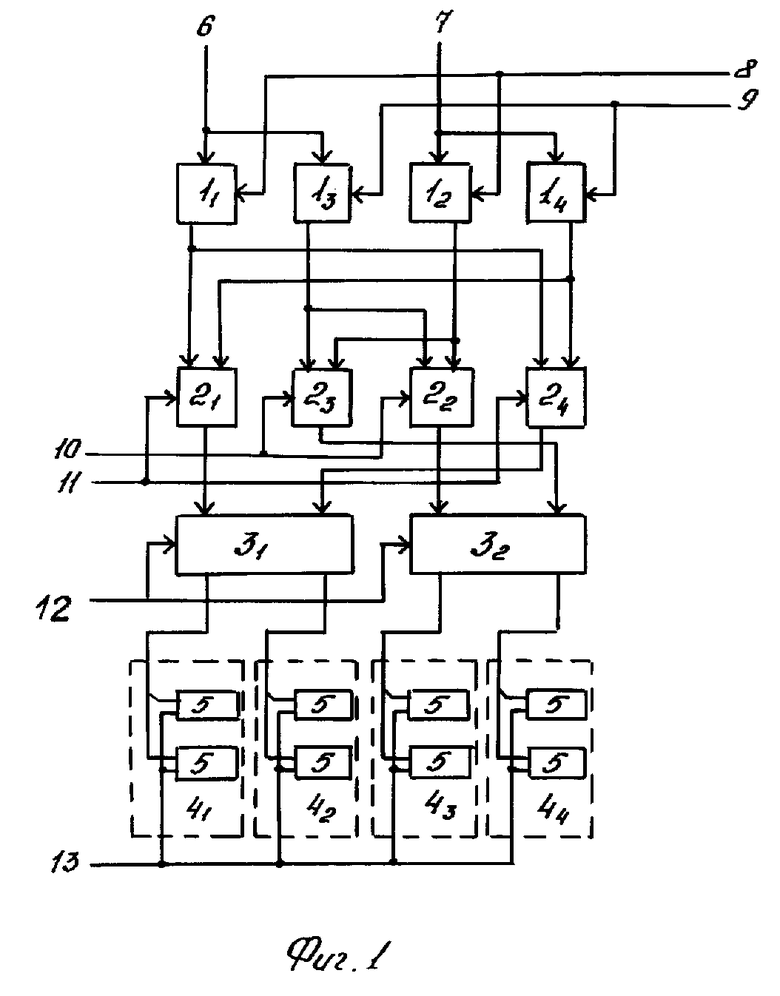

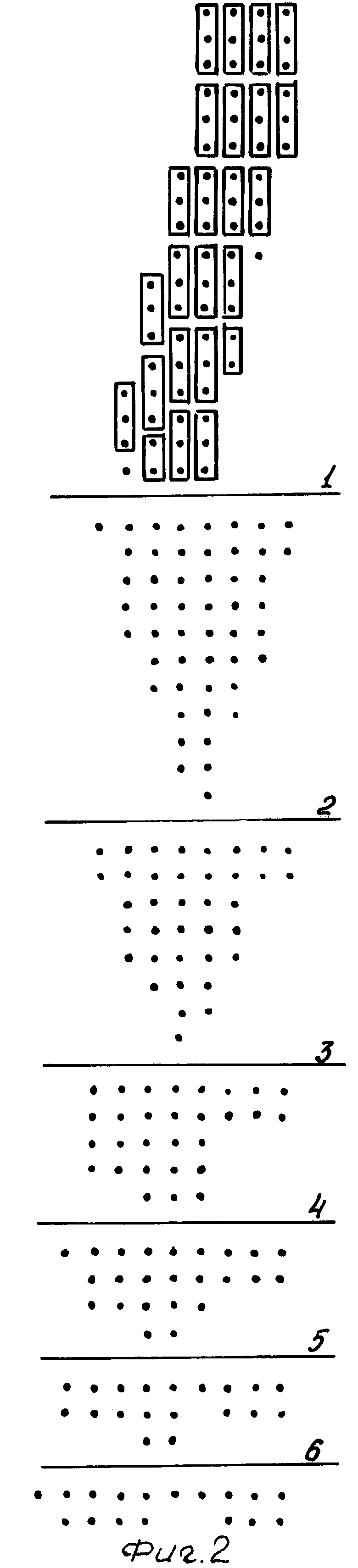

На фиг. 1 представлена функциональная схема устройства для выполнения дискретных ортогональных преобразований; фиг.2 - преобразование многострочной матрицы в сумматоре двухрядного кода в двухрядный код с помощью трехвходовых одноразрядных сумматоров при разрядности входных данных m = 4.

Устройство (фиг.1) содержит первый 11, второй 12, третий 13, и четвертый 14 умножители двухрядного кода, первый 21, второй 22, третий 23 и четвертый 24 сумматоры двухрядного кода, первый 31 и второй 32 коммутаторы, первый 41, второй 42, третий 43 и четвертый 44 блоки регистров, состоящие из регистров 5, входы мнимой 6 и реальной 7 частей второго операнда, входы реальной 8 и мнимой 9 частей коэффициента устройства, входы реальной 10 и мнимой 11 частей первого операнда, управляющий вход 12 и тактовый вход устройства 13.

Устройство работает следующим образом.

При выполнении прямого преобразования Фурье на первый вход 12 устройства подается нулевой сигнал, при выполнении обратного преобразования Фурье этот сигнал должен быть единичным. В остальном работа устройства в обоих режимах одинакова, поэтому рассмотрим режим прямого преобразования Фурье.

На входы 6 и 7 устройства поступают мнимая ImBi и действительная ReBi части второго операнда Bi, на входы 8 и 9 - действительная ReWi и мнимая ImWi части коэффициента устройства, на входы 10 и 11 - действительная ReAi и мнимая ImAi части второго операнда Ai устройства. В результате умножения на выходах первого 11, второго 12, третьего 13 и четвертого 14 умножителей двухрядного кода будут сформированы многострочные матрицы частичных произведений соответственно ImBi. ReWi, ReBi..ReWi, ImBi.ImWi и ReBi.ImWi. С выходов умножителей двухрядного кода многострочные матрицы частичных произведений по шинам многострочного кода поступают на сумматоры двухрядного кода, на входы которых также поступают соответствующие коды первого операнда. Таким образом, на входе сумматора двухрядного кода 2i будет сформирована многострочная кодовая матрица, вид которой соответствует позиции 1 на фиг.2. Многострочная кодовая матрица последовательно преобразуется сумматором двухрядного кода в двухрядный код, этапы преобразования изображены соответствующими позициями на фиг.2.

На выходах первого 21, второго 22, третьего 23 и четвертого 24 сумматоров двухрядного кода будут образованы двухрядные коды соответственно

ImAi + ImBi˙ReWi + ReBi ˙ImWi (1)

ReAi + ReBi ˙ReWi - (ImBi ˙ImWi) (2)

ReAi - (ReBi˙ ReWi) + ImBi ˙ImWi (3)

ImAi - (imBi˙ReWi) - (ReBi ˙ImWi) (4)

Коды выражений, обозначенных круглыми скобками, подаются на инверсные входы одноразрядных сумматоров двухрядного кода 2i, что необходимо для реализации операции вычитания в формулах (2) - (4). По тактовым сигналам значения выражений (1) и (4), соответствующие коды ImAi+1 и ImBi+1, через первый коммутатор будут записаны в первый 41 и второй 42 блоки регистров, а значения выражений (2) и (3), соответствующие кодам ReAi+1 и ReBi+1, через второй коммутатор будут записаны в третий 43 и четвертый 44 блоки регистров.

При выполнении обратного преобразования Фурье под воздействием единичного сигнала на первый и второй коммутаторы и тактовых сигналов в первый 41, второй 42, третий 43 и четвертый 44 блоки регистров производится запись кодов соответственно ImBi+1 ImAi+1, ReBi+1, ReAi+1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА | 1991 |

|

RU2023299C1 |

| Устройство для вычисления быстрого преобразования фурье | 1974 |

|

SU467356A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1170462A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для умножения комплексных чисел | 1985 |

|

SU1297034A1 |

Изобретение относится к вычислительной технике, в частности к цифровой обработке радио-, гидро- и звуколокационных сигналов, и может быть применено при построении быстродействующих Фурье-процессоров. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается за счет обеспечения одновременного суммирования большого числа цифровых кодов и одновременного вычисления действительных и мнимых частей результата выполнения базовой операции, для этого в устройство, содержащее два умножителя двухрядного кода, четыре сумматора двухрядного кода, два коммутатора и четыре блока регистров, введены третий и четвертый умножители двухрядного кода. 2 ил.

УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНЫХ ОРТОГОНАЛЬНЫХ ПРЕОБРАЗОВАНИЙ, содержащее первый и второй умножители двухрядного кода, первый, второй, третий и четвертый сумматоры двухрядного кода, первый и второй коммутаторы, первый, второй, третий и четвертый блоки регистров, причем тактовые входы блоков регистров являются тактовыми входами устройства, первый вход второго сумматора двухрядного кода является входом реальной части первого операнда устройства, входы мнимой и реальной частей второго операнда которого соединены с первыми входами соответственно первого и второго умножителей двухрядного кода, управляющие входы первого и второго коммутаторов объединены и являются управляющим входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены третий и четвертый умножители двухрядного кода, первые входы которых соединены соответственно с первыми входами первого и второго умножителей двухрядного кода, вторые входы первого и второго умножителей двухрядного кода соединены между собой и являются входом реальной части коэффициента устройства, вторые входы третьего и четвертого умножителей двухрядного кода соединены между собой и являются входом мнимой части коэффициента устройства, выходы с первого по четвертый умножителей двухрядного кода соединены соответственно с первым входом первого, вторым входом второго и первыми входами третьего и четвертого сумматоров двухрядного кода, второй вход третьего сумматора двухрядного кода соединен с первым входом второго сумматора двухрядного кода, второй вход первого, третьи входы второго, третьего сумматоров и второй вход четвертого сумматора двухрядного кода соединены соответственно с выходами четвертого, третьего, второго и первого умножителей двухрядного кода, выходы первого и четвертого сумматоров двухрядного кода соединены соответственно с первым и вторым информационными входами первого коммутатора, первый и второй выходы которого соединены с информационными входами соответственно первого и второго блоков регистров, выходы второго и третьего сумматоров двухрядного кода соединены соответственно с первым и вторым информационными входами второго коммутатора, первый и второй выходы которого соединены с информационными входами соответственно третьего и четвертого блоков регистров, третьи входы первого и четвертого сумматоров двухрядного кода соединены между собой и являются входом мнимой части первого операнда устройства.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-12-15—Публикация

1990-11-05—Подача