Изобретение относится к вычислиельной технике, в частности к циф- овоу обработке радио-, гидро- и звуколокационных сигнгшов, и может быть применено при построении быстроействующих процессоров, работаюпщх условиях жестких временных ограничений.

Цель изобретения - увеличение быстродействия за счет представления искрет преоГфазуемого сигнала двух- строчными кодами.

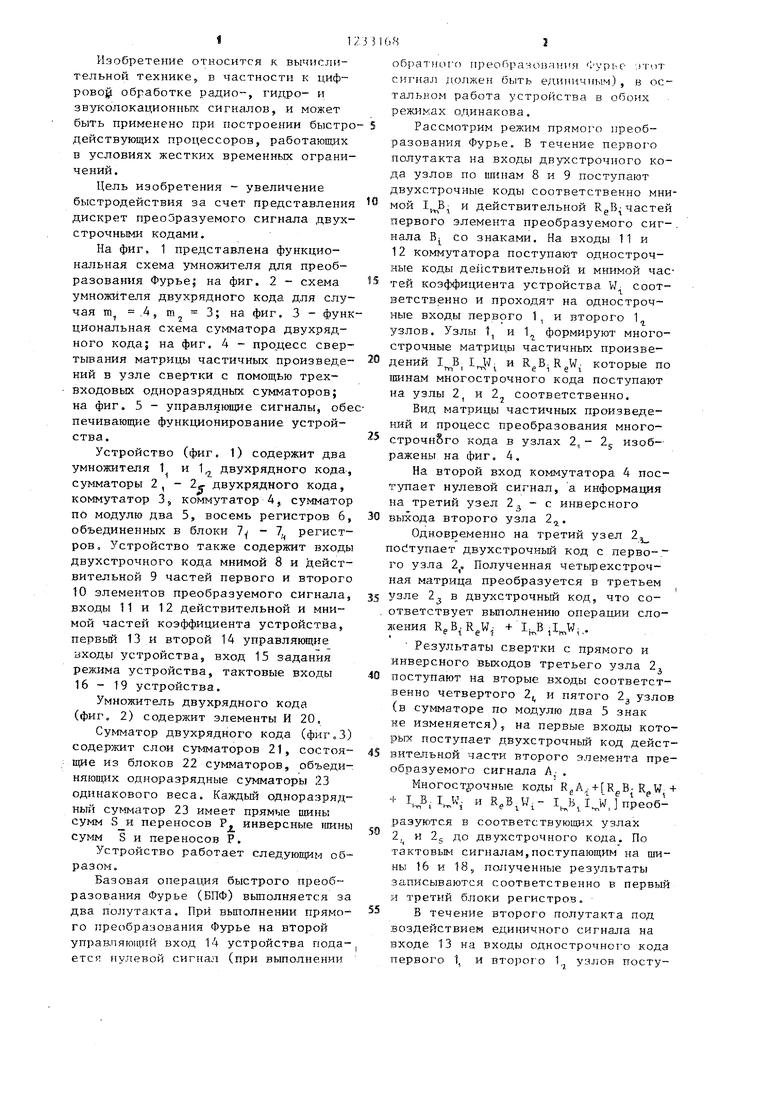

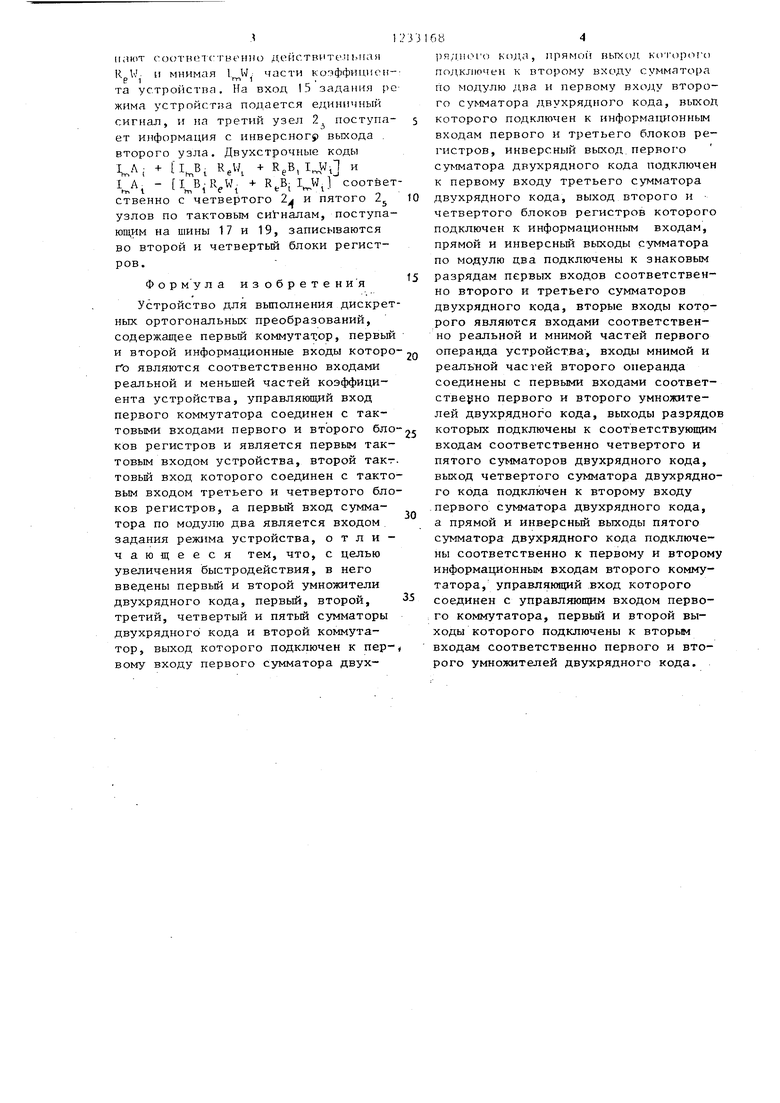

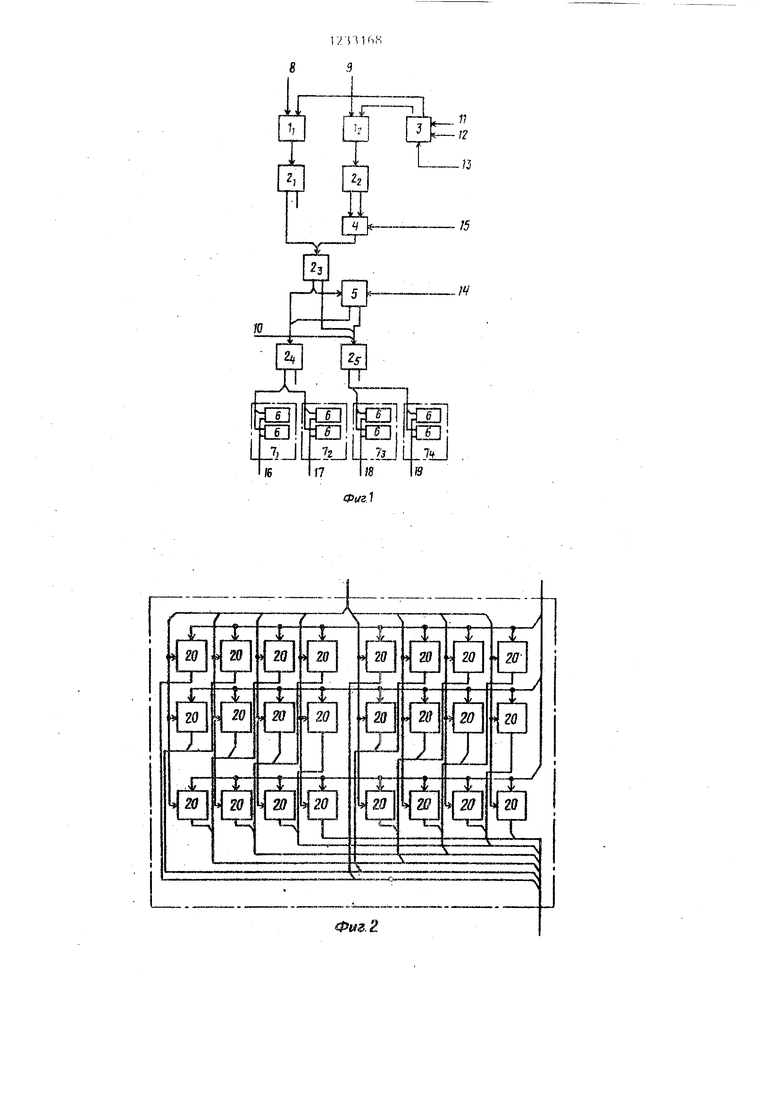

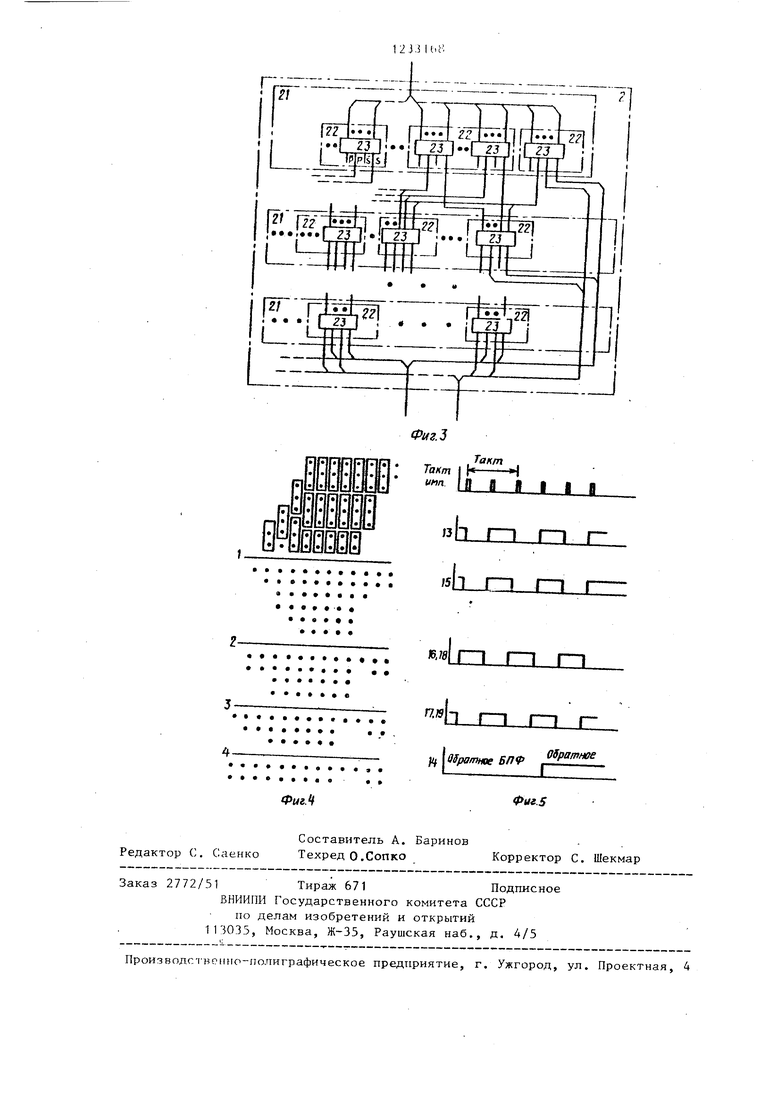

На фиг, 1 представлена функциональная схема умножителя для преобразования ФурьеJ на фиг. 2 - схема умножителя двухрядного кода для случая т, ,4, т. 3; на фиг, 3 - функциональная схема сумматора двухрядного кода; на фиг, 4 - продесс свертывания матрицы частичных произведений в узле свертки с помощью трех- входовых одноразрядных сумматоров; на фиг. 5 - управляющие сигналы, обес печивающие функционирование устройства.

Устройство (фиг. 1) содержит два умножителя 1 и 1 двухрядного кода, сумматоры 2 , 2я- двухрядного кода, коммутатор 3, коммутатор 4, сумматор по модулю два 5, восемь регистров 6, объединенных в блоки 7у - 1, регистров. Устройство также содержит входы двухстрочного кода мнимой 8 и действительной 9 частей первого и второго 10 элементов преобразуемого сигнала, входы 11 и 12 действительной и мнимой частей коэффициента устройства, первьй 13 и второй 14 управляющие аходы устройства, вход 15 задания режима устройства, тактовые входы 16 - 19 устройства.

Умножитель двухрядного кода (фиг. 2) содержит элементы И 20.

Сумматор двухрядного кода (фиГоЗ) содержит слои сумматоров 21, состоя- щие из блоков 22 сумматоров, объеди- няюпщх одноразрядные сумматоры 23 одинакового веса. Каждьй одноразрядный сумматор 23 имеет прямые шины сумм S и переносов Р инверсные тины сумм S и переносов Р.

Устройство работает следующим образом.

Базовая операция быстрого преобразования Фурье (БПФ) вьшолняется за два полутакта. При выполнении прямого преобразования Фурье на второй управ-пяющий вход 14 устройства пода- ется нулевой сигнал (при выполнении

обратного преобрачовяиия 1 урье :ггпт сигнал должен быть едннич){ым) , в ос тальлом работа устройства в обоих режимах одинакова.

Рассмотрим режим прямого преобразования Фурье. В течение первого полутакта на входы двухстрочного кода узлов по шинам 8 и 9 поступают двухстрочные коды соответственно мнимой и действительной RgB частей первого элемента преобразуемого сиг-. нала В, со знаками. На входы 11 и 12 коммутатора поступают однострочные коды действительной и мнимой час5 тей Коэффициента устройства W соответственно и проходят на однострочные входы первого 1, и второго 1 узлов. Узлы 1 и 1 формируют многострочные матрицы частичных произве0 дений и которые по тЕинам многострочного кода поступают на узлы 2| и 2j соответственно.

Вид матрицы частичных произведений и процесс преобразования много5 строчнйго кода в узлах 2 изображены на фиг. 4.

На второй вход коммутатора 4 поступает нулевой сигнал, а информация на третий узел 2 , - с инверсного

0 выхода второго узла 2.

Одновременно на третий узел 2 поступает двухстрочный код с перво-- го узла Полученная четырехстроч- ная матрица преобразуется в третьем

5 узле 2 в двухстрочный код, что соответствует выполнению операции ело- женин .W.; + 1,В,,.

Результаты свертки с прямого и инверсного выходов третьего узла 2,

0 поступают на вторые входь соответственно четвертого 2 и пятого 2 узлов (в сумматоре по модулю два 5 знак не измен:яется),, на первые входы кото- pbDf поступает двухстрочный код дейст45 вительной части второго элемента преобразуемого сигнала Л,- .

Многост эочные коды RgA + + - - , и SeS. ,jnpeo6- разуются в соответствующих узлах

2, и 2 до двухстрочного кода. По тактовым сигналам,поступающим на шины 16 и 18, полученные результаты записываются соответственно в первый и третий блоки регистров.

55 в течение второго полутакта под воздействием единичного сигнала на входе 13 на входы однострочного кода первого 1, и второг о 1,j узлов постуiKUdT соотвел с твенио zun iCTBViTtvnbitaH R W я мнимая части коэффициопта устройстпа, На вход 15 задания ре жима устройства подается единичный сигнал, и на третий узел 2 поступа- ет информация с ннверсиогр выхода . второго узла. Двухстрочные коды Л, 4- , R,U ReB, и - + соответ ственно с четвертого 2 и пятого 2 узлов по тактовым сигналам, поступающим на шины 17 и 19, записываются во второй и четвертый блоки регистров.

Форм ула изобретени я

Устройство для выполнения дискретных ортогональных преобразований, содержащее первый коммута 1:ор, первьш и второй информационные входы котороГо являются соответственно входами реальной и меньшей частей коэффициента устройства, управляющий вход первого коммутатора соединен с тактовыми входами первого и второго блоков регистров и является первым тактовым входом устройства, второй такт-, товьй вход которого соединен с тактовым входом третьего и четвертого блоков регистров, а первьй вход сумматора по модулю два является входом задания режима устройства, отличающееся тем, что, с целью увеличения быстродействия, в него введены первый и второй умножители двухрядного кода, первьш, второй, третий, четвертый и пятый сумматоры двухрядного кода и второй коммутатор, выход которого подключен к пер- вому входу первого сумматора двух

5 10

д 5 5

0

1684

ря;п1О1 о кода, прямой ньгхсм , ксггор|11Ч) подключеь к второму входу сумматора по модулю два и первому входу второго сумматора двухрядного кода, выход которого подключен к информационным входам первого и третьего блоков регистров, инверсный выход первог-о суьматора двухрядного кода подключен к первому входу третьего сумматора двухрядного кода, выход второго и четвертого блоков регистров которого подключен к информационным входам, прямой и инверсный выходы сумматора по модулю два подключены к знаковым разрядам первых входов соответственно второго и третьего сумматоров двухрядного кода, вторые входы которого являются входами соответственно реальной и мнимой частей первого операнда устройства, входы мнимой и реальной частей второго операнда соединены с первыми входами соответ- первого и второго умножителей двухрядного кода, выходы разрядов которых подключены к соответствующим входам соответственно четвертого и пятого сумматоров двухрядного кода, выход четвертого сумматора двухрядного кода подкл1очен к второму входу первого сумматора двухрядного кода, а прямой и инверсный выходы пятого сумматора двухрядного кода подключены соответственно к первому и второму информационным входам второго коммутатора, управляющий вход которого соединен с управляющим входом первого коммутатора, первый и второй выходы которого подключены к вторьм входам соответственно первого и второго умножителей двухрядного кода.

Фиг.

Такт .у. |.n.j|.i. 7fl/r/7i I НН

io fl Д i « Я

;зП -I I-I Г

f.iri.ii;i.ii.fi.i:i

::::::::::: «LL

м П

3- -у-n; {-j

.

1лг г-ял Обратное 4-.-; pJ w/mwe .-:.

ал

Составитель А. Баринов Редактор С. СаенкоТехред О.Сопко . P ZLl-- -

. -----

ЗакГз 2772/51 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1ГЮ35, Москва, Ж-35, Раушская наб., д. 4/5

производствоино-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНЫХ ОРТОГОНАЛЬНЫХ ПРЕОБРАЗОВАНИЙ | 1990 |

|

RU2024931C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА | 1991 |

|

RU2023299C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Рекурсивный цифровой фильтр | 1989 |

|

SU1658376A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Цифровой нерекурсивный фильтр | 1988 |

|

SU1566472A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

Изобретение относится к вычислительной технике, в частности к цифровой обработке радио-, гидро- и звуколокационных сигналов, и может быть применено при построении быстродействующих процессоров, работающих в условиях жестких временных ограничений. Цель изобретения - увеличение быстродействия за счет представления дискрет преобразуемого сигнала двухстрочными сигналами. Устройство содержит два коммутатора., четыре блока регистров, два умножителя двухрядного кода, пять сумматоров двухрядного кода с соответствующими связями, 5 ил. О 00

| Арифметическое устройство для базовой операции быстрого преобразования фурье | 1980 |

|

SU875387A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-11-23—Подача