(Риг./

Изобретение относится к радиотехнике и связи и может быть использовано в системах автоматического регулирования.

Цель изобретения - расширение частотного диапазона.

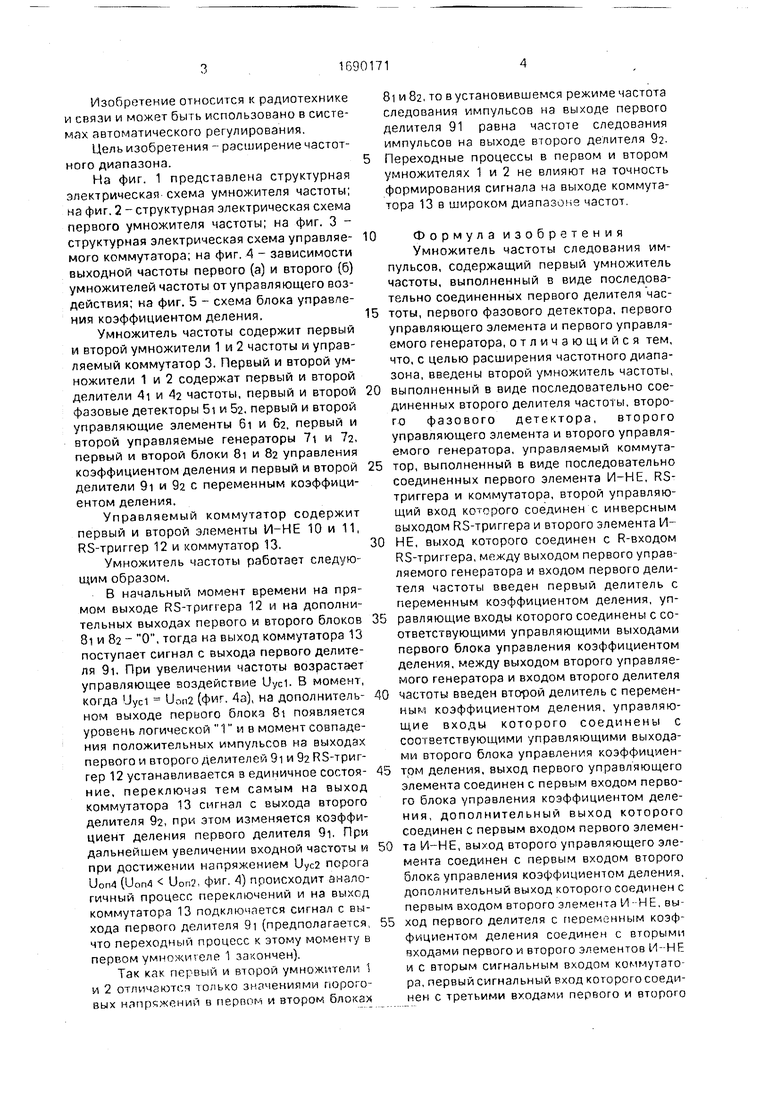

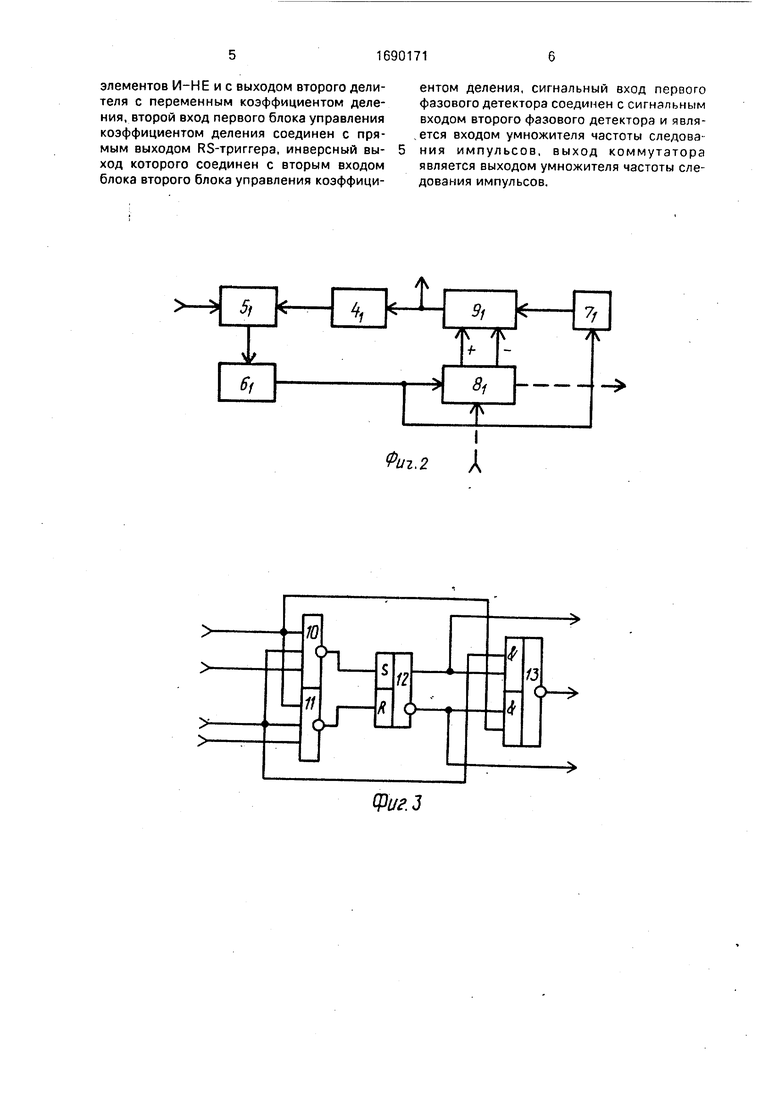

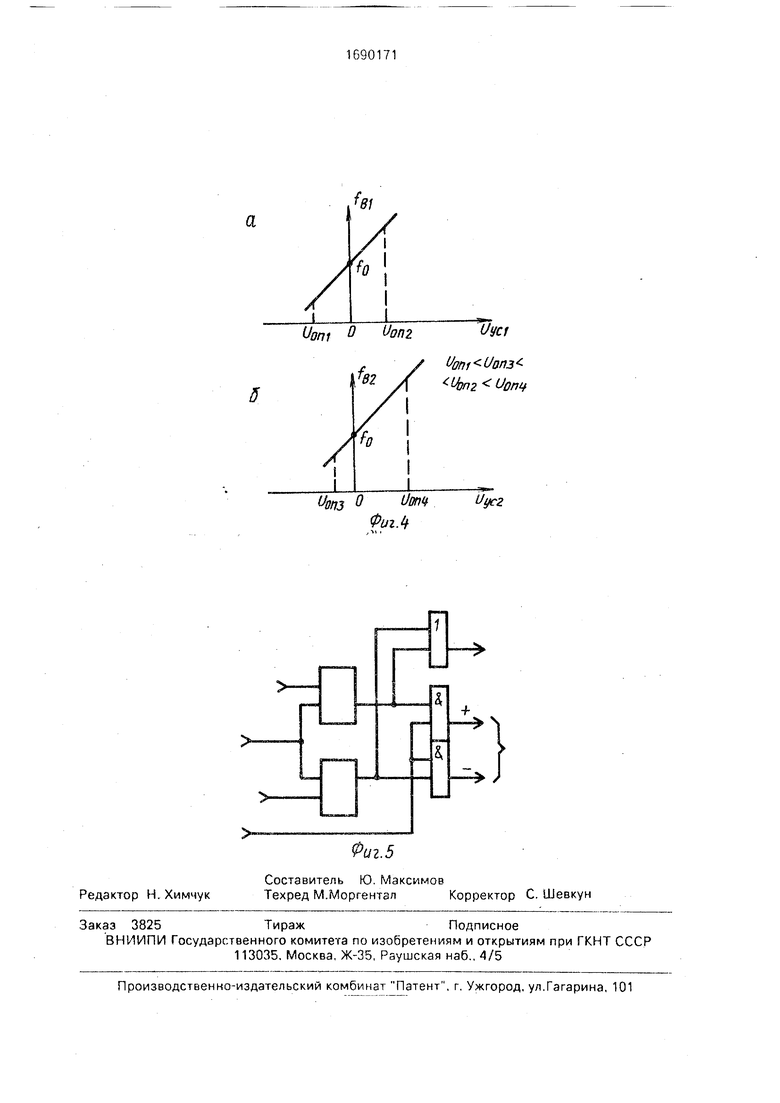

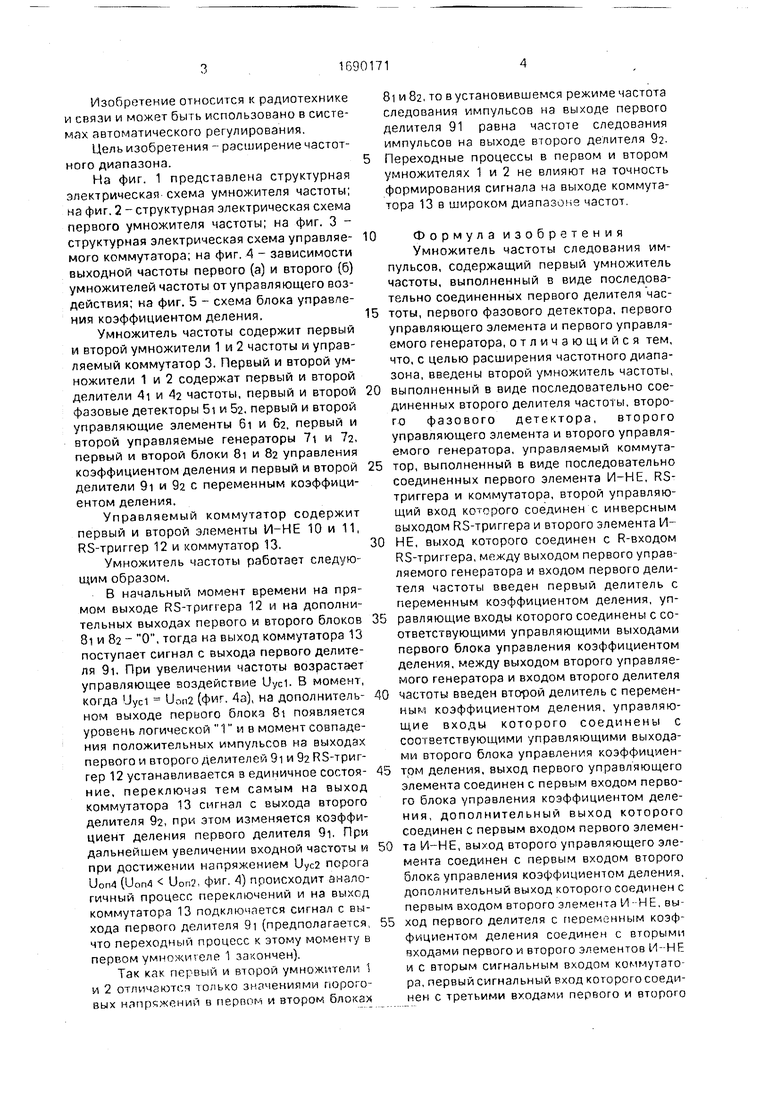

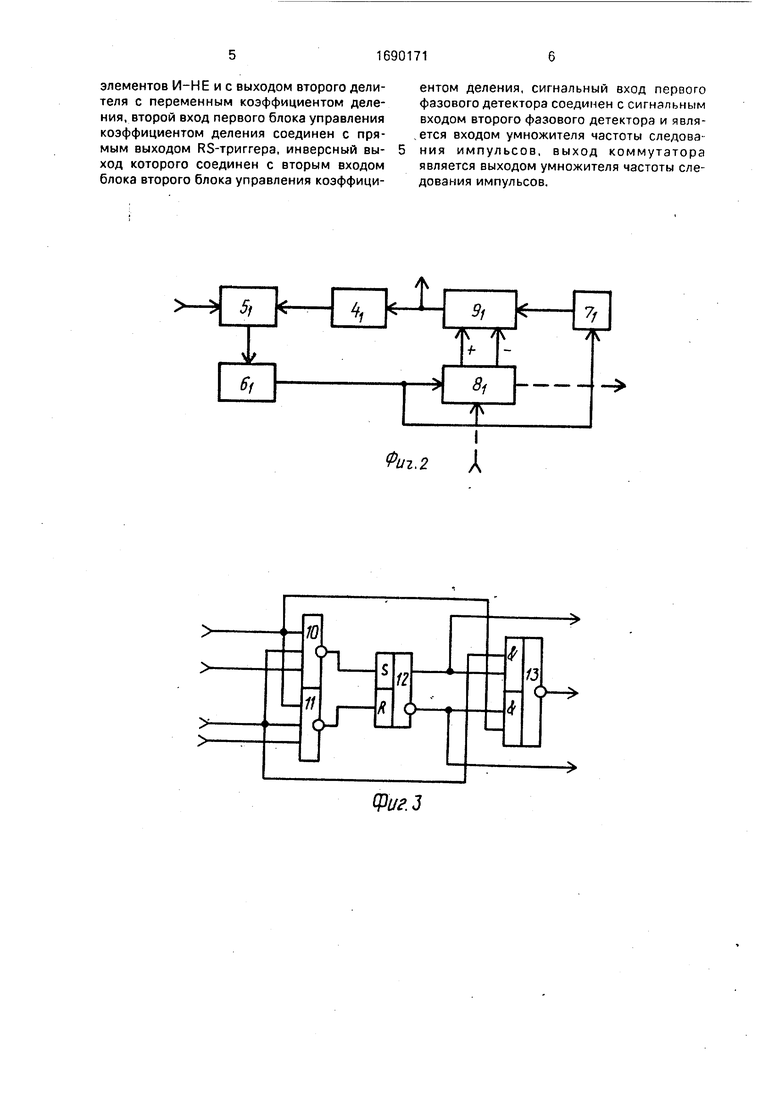

На фиг. 1 представлена структурная электрическая схема умножителя частоты; на фиг, 2 - структурная электрическая схема первого умножителя частоты; на фиг. 3 - структурная электрическая схема управляемого коммутатора; на фиг. 4 - зависимости выходной частоты первого (а) и второго (б) умножителей частоты от управляющего воздействия; на фиг. 5 - схема блока управления коэффициентом деления.

Умножитель частоты содержит первый и второй умножители 1 и 2 частоты и управляемый коммутатор 3. Первый и второй умножители 1 и 2 содержат первый и второй делители 4i и 42 частоты, первый и второй фазовые детекторы 5i и 52, первый и второй управляющие элементы 6i и 62. первый и второй управляемые генераторы 7i и 2, первый и второй блоки 8i и 82 управления коэффициентом деления и первый и второй делители 9i и 92 с переменным коэффициентом деления.

Управляемый коммутатор содержит первый и второй элементы И-НЕ 10 и 11, RS-триггер 12 и коммутатор 13.

Умножитель частоты работает следующим образом.

В начальный момент времени на прямом выходе RS-триггера 12 и на дополнительных выходах первого и второго блоков 8i и 82 - О, тогда на выход коммутатора 13 поступает сигнал с выхода первого делителя 9i, При увеличении частоты возрастает управляющее воздействие Uyci. В момент, когда Jyd Uon2 (фиг. 4а), на дополнительном выходе первого блока 8i появляется уровень логической 1 и в момент совпадения положительных импульсов на выходах первого и второго делителей 9i и 9г RS-триггер 12 устанавливается в единичное состояние, переключая тем самым на выход коммутатора 13 сигнал с выхода второго делителя 92, при этом изменяется коэффициент деления первого делителя 9i, При дальнейшем увеличении входной частоты м при достижении напряжением Uyc2 порога U0n4 (Uon4 Uon2. фиг. 4) происходит аналогичный процесс переключений и на выход коммутатора 13 подключается сигнал с выхода первого делителя 9i (предполагается, что переходный процесс к этому моменту в первом умножителе 1 закончен).

Так как первый и второй умножители 1 и 2 отличаются только значениями пороговых напряжений в первом и втором блоках

8i и 82, то в установившемся режиме частота следования импульсов на выходе первого делителя 91 равна частоте следования импульсов на выходе второго делителя Переходные процессы в первом и втором умножителях 1 и 2 не влияют на точность формирования сигнала на выходе коммутатора 13 в широком диапазоне частот.

0 Формула изобретения

Умножитель частоты следования импульсов, содержащий первый умножитель частоты, выполненный в виде последовательно соединенных первого делителя час5 тоты, первого фазового детектора, первого управляющего элемента и первого управляемого генератора, отличающийся тем, что, с целью расширения частотного диапазона, введены второй умножитель частоты,

0 выполненный в виде последовательно соединенных второго делителя частоты, второго фазового детектора, второго управляющего элемента и второго управляемого генератора, управляемый коммута5 тор, выполненный в виде последовательно соединенных первого элемента И-НЕ, RS- триггера и коммутатора, второй управляющий вход которого соединен с инверсным выходом RS-триггера и второго элемента И0 НЕ, выход которого соединен с R-входом RS-триггера, между выходом первого управляемого генератора и входом первого делителя частоты введен первый делитель с переменным коэффициентом деления, уп5 равляющие входы которого соединены с соответствующими управляющими выходами первого блока управления коэффициентом деления, между выходом второго управляемого генератора и входом второго делителя

0 частоты введен второй делитель с переменным коэффициентом деления, управляющие входы которого соединены с соответствующими управляющими выходами второго блока управления коэффициен5 трм деления, выход первого управляющего элемента соединен с первым входом первого блока управления коэффициентом деления, дополнительный выход которого соединен с первым входом первого элемен0 та И-НЕ, выход второго управляющего элемента соединен с первым входом второго блок, управления коэффициентом деления, дополнительный выход которого соединен с первым входом второго элемента И-НЕ, вы5 ход первого делителя с переменным коэффициентом деления соединен с вторыми входами первого и второго элементов И-НЕ и с вторым сигнальным входом коммутатора, первый сигнальный вход которого соединен с третьими входами первого и второго

элементов И-НЕ и с выходом второго делителя с переменным коэффициентом деления, второй вход первого блока управления коэффициентом деления соединен с прямым выходом RS-триггера, инверсный выход которого соединен с вторым входом блока второго блока управления коэффициентом деления, сигнальный вход первого фазового детектора соединен с сигнальным входом второго фазового детектора и явля- ется входом умножителя частоты следования импульсов, выход коммутатора является выходом умножителя частоты следования импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство дискретного задания фазового сдвига | 1991 |

|

SU1827643A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

Изобретение относится к радиотехнике и связи и может быть использовано в системах автоматического регулирования. Цель изобретения - расширение частотного диапазона. Умножитель содержит первый и второй умножители 1 и 2 частоты и управляемый коммутатор 3, Умножитель содержит первый и второй умножители 1 и 2 частоты И управляемый коммутатор 3. Каждый из умножителей 1 и 2 частоты содержит делитель частоты, фазовый детектор, управляющий элемент, управляемый генератор, блок управления коэффициентом деления и делитель с переменным коэффициентом деления. Управляемый коммутатор 3 содержит два элемента И-НЕ, RS-триггер и коммутатор. Поочередное подключение на выход управляемого коммутатора 3 сигналов с выходов первого и второго умножителей 1 и 2 в зависимости от изменения частоты входного сигнала позволяет осуществлять умножение частоты в широком диапазоне частот 5 ил.

щ г

Риг.2 А

12

3

/з

о-

Фиг.З

а

(Jam 0 Uonz

/

%j 0 Urn иусг Фиг А

Uonz

UKf

UOtlLf

| Умножитель частоты | 1976 |

|

SU678633A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-07—Публикация

1988-06-06—Подача