4 4

00

оо

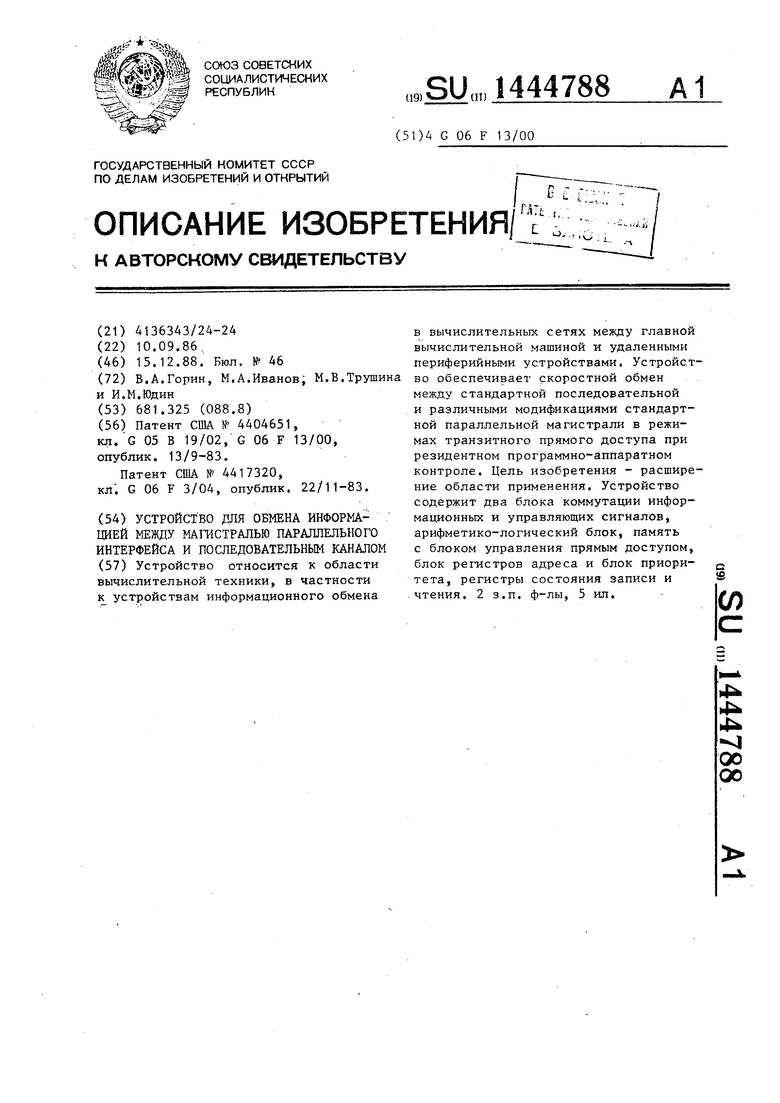

Изобретение относится к области вычислительной техники, в частности к устройствам последовательного информационного обмена между главной вьгаислительной машиной и удаленными периферийными устройствами, имеющими магистральный параллельный интерфейс При этом информационньй обмен с мультиплексным каналом осуществляется двухуровневым фазоманипулированным кодом без возврата к нулю.

Целью изобретения является расширение области применения устройства.

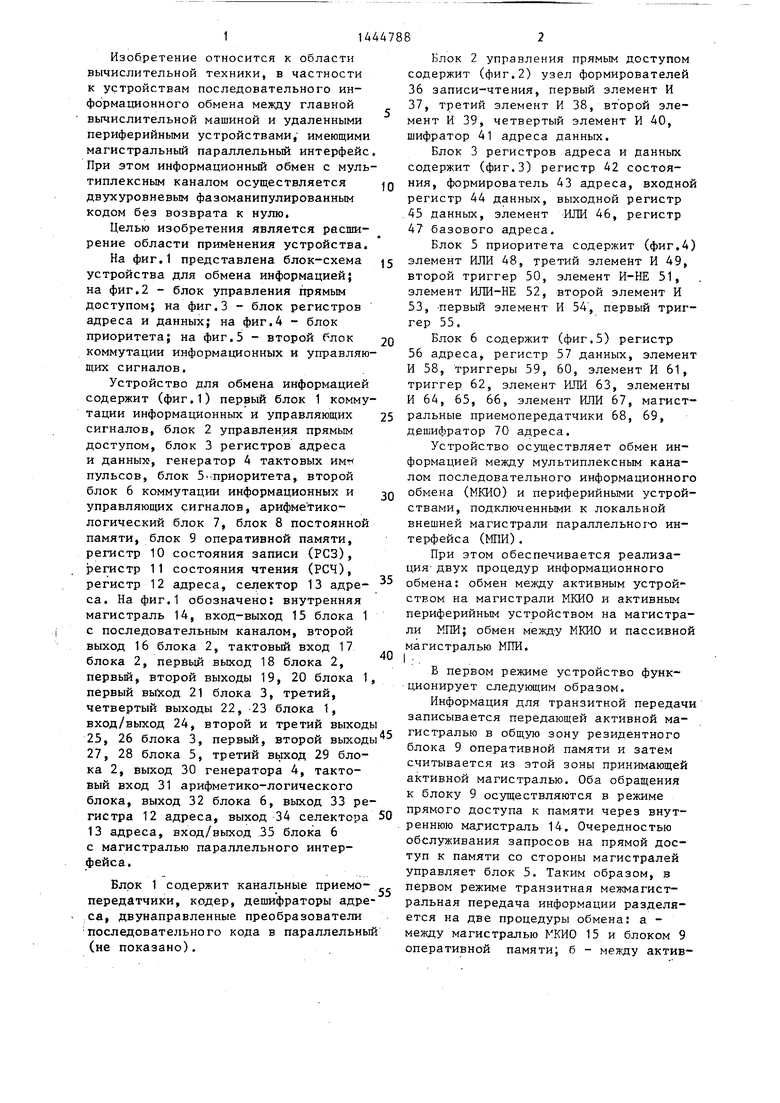

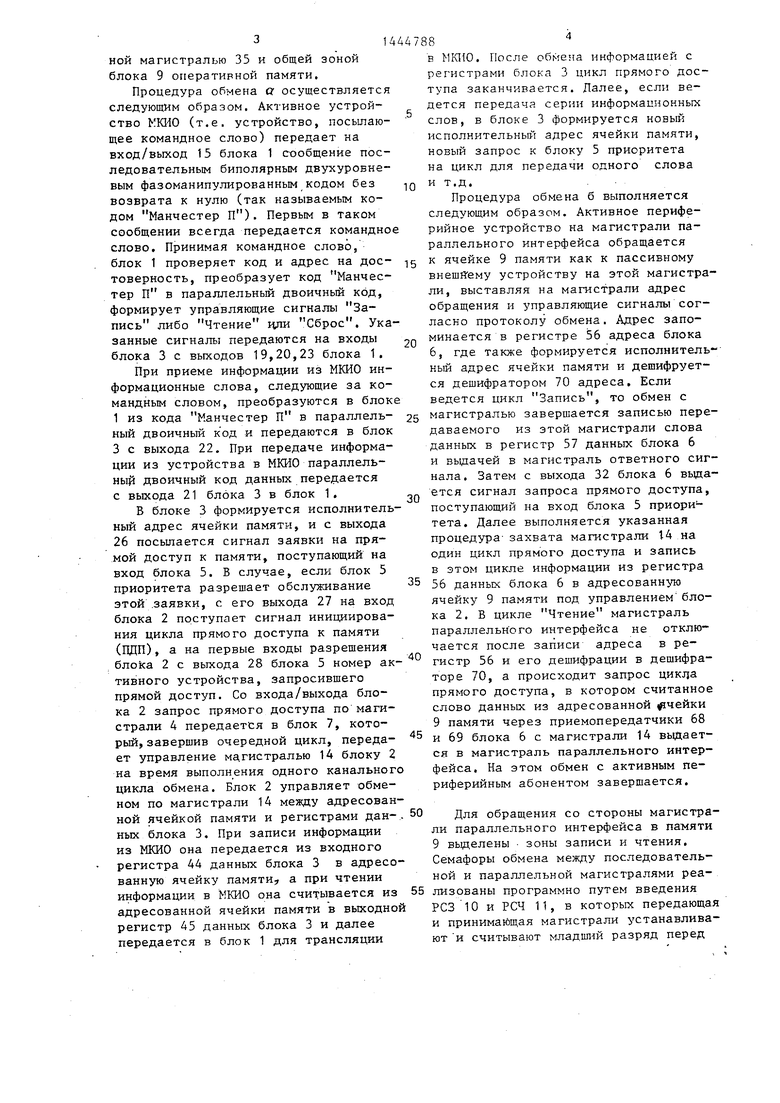

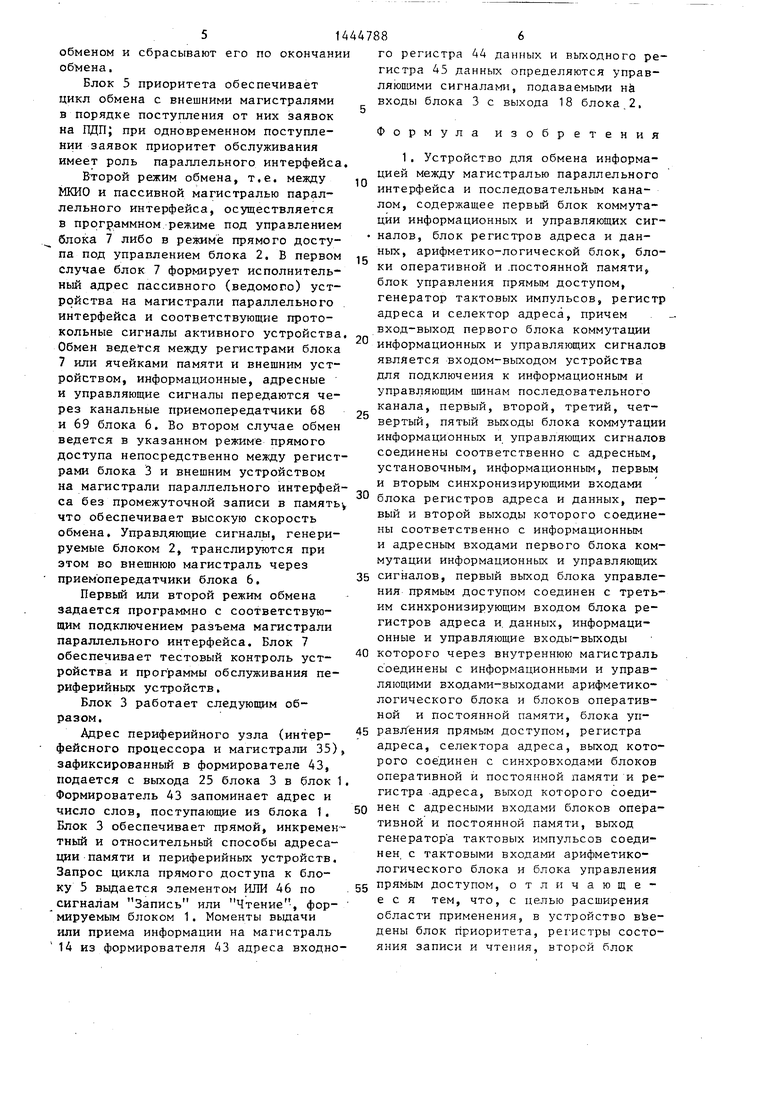

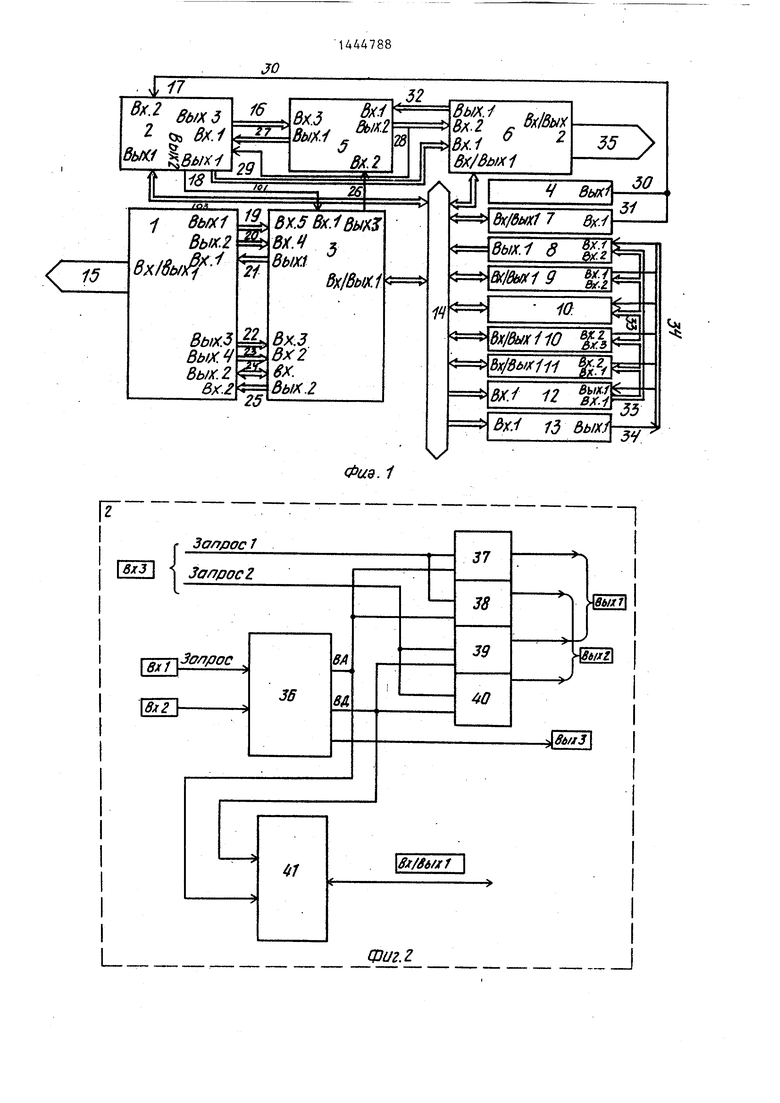

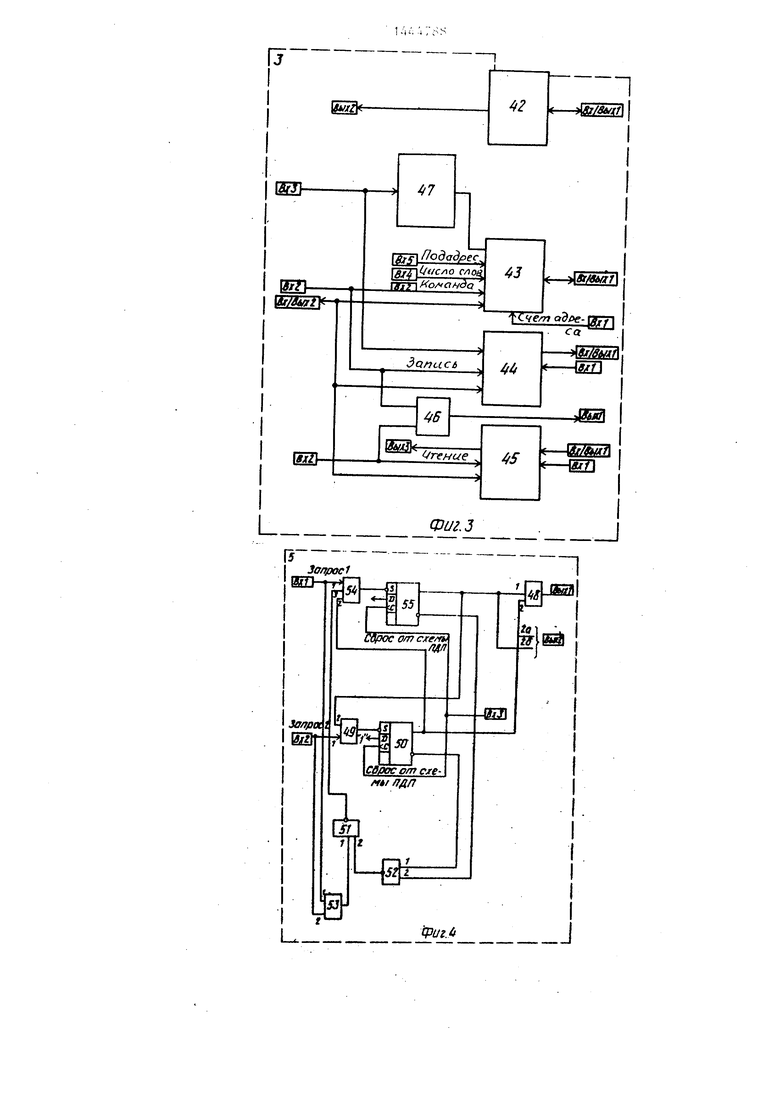

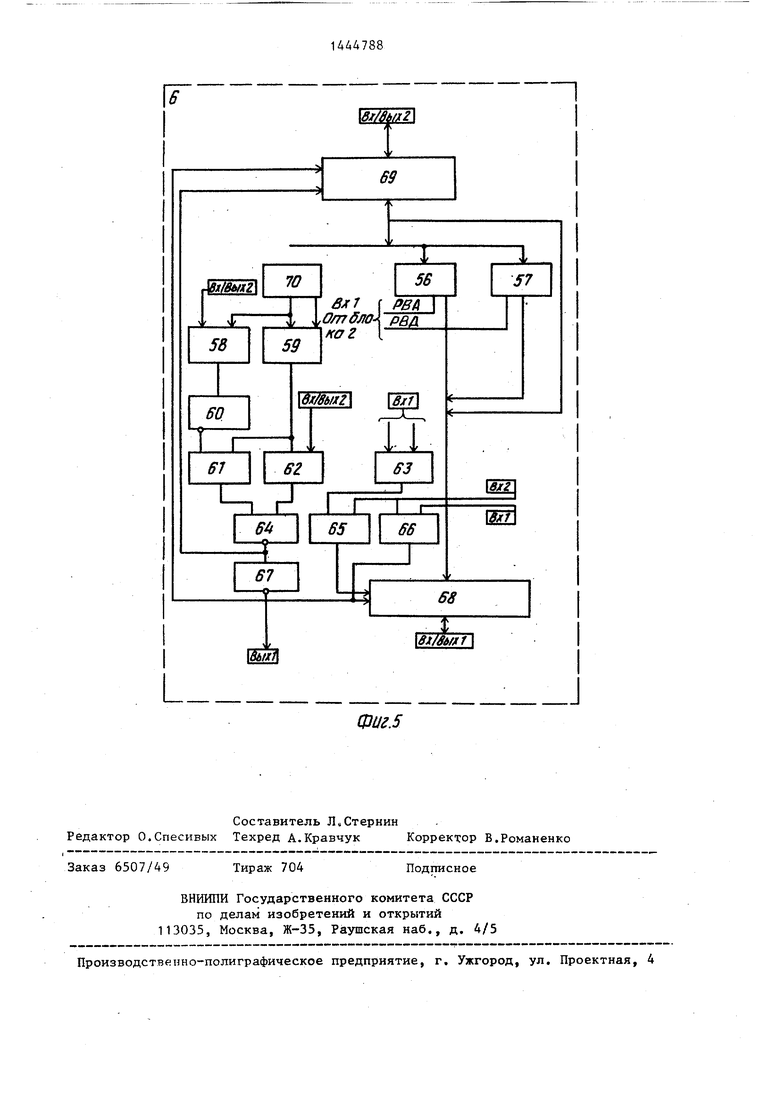

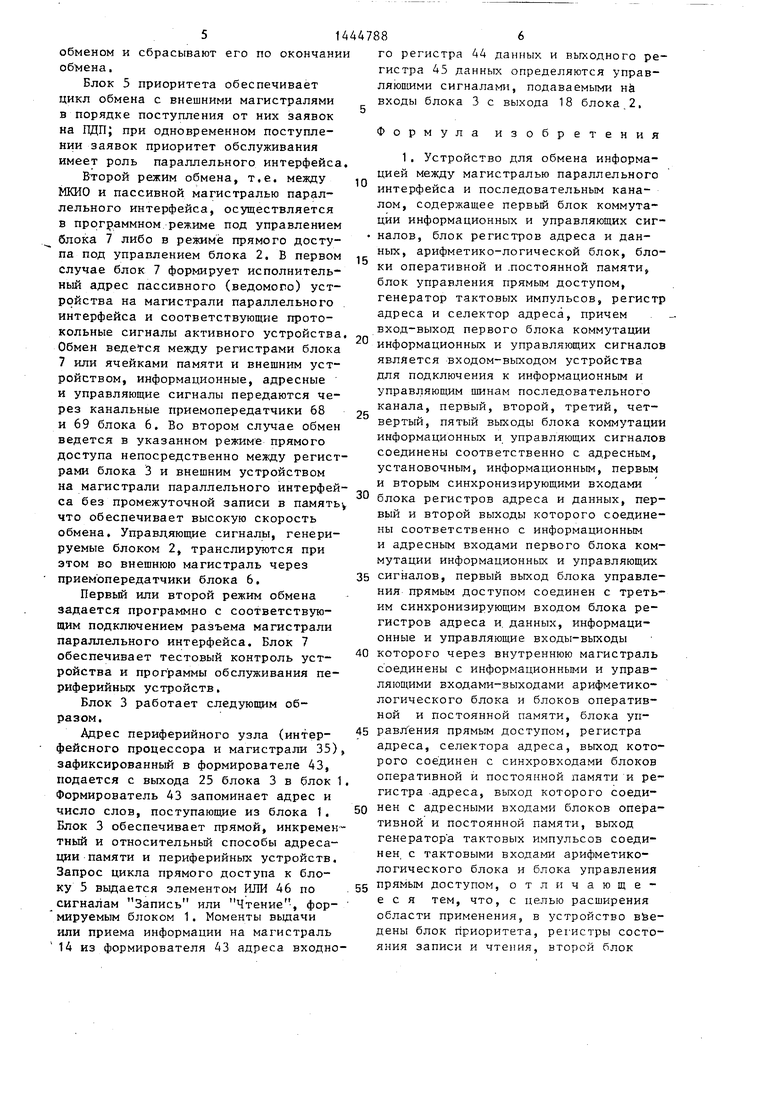

На фиг,1 представлена блок-схема устройства для обмена информацией; на фиг,2 - блок управления гфямым доступом; на фиг.З - блок регистров адреса и данных; на фиг,4 - блок приоритета; на фиг,5 - второй Рлок коммутации информационных и управляющих сигналов.

Устройство для обмена информацией содержит (фиг,1) первый блок 1 коммутации информационных и управляющих сигналов, блок 2 управления прямым доступом, блок 3 регистров адреса и данных, генератор А тактовых имт пульсов, блок 5.приоритета, второй блок 6 коммутации информационных и управляющих сигналов, арифметико- логический блок 7, блок 8 постоянной памяти, блок 9 оперативной памяти, регистр 10 состояния записи (РСЗ), регистр 11 состояния чтения (РСЧ), регистр 12 адреса, селектор 13 адреса. На фиг,1 обозначено внутренняя магистраль 14, вход-выход 15 блока 1 с последовательным каналом, второй выход 16 блока 2, тактовый вход 17 блока 2, первый выход 18 блока 2, первьй, второй выходы 19, 20 блока 1 первый выход 21 блока 3, третий, четвертый выходы 22, 23 блока 1, вход/выход 24, второй и третий выход 25, 26 блока 3, первый, второй выход 27, 28 блока 5, третий вьжод 29 блока 2, выход 30 генератора 4, тактовый вход 31 арифметико-логического блока, выход 32 блока 6, выход 33 регистра 12 адреса, выход 34 селектора 13 адреса, вход/выход 35 блока 6 с магистралью параллельного интерфейса.

Блок 1 содержит канальные приемопередатчики, кодер, дешифраторы адреса, двунаправленные преобразователи последовательного кода в параллельный (не показано),

g

0

5 0

5

5

5

второй элемент И И 54, первый триг0

0 I

Блок 2 управления прямым доступом содержит (фиг,2) узел формирователей 36 записи-чтения, первый элемент И 37, третий элемент И 38, второй элемент И 39, четвертый элемент И 40, щифратор 41 адреса данных.

Блок 3 регистров адреса и данных содержит (фиг.З) регистр 42 состояния, формирователь 43 адреса, входной регистр 44 данных, выходной регистр .45 данных, элемент чИЛИ 46, регистр 47 базового адреса.

Блок 5 приоритета содержит (фиг,4) элемент ИЛИ 48, третий элемейт И 49, второй триггер 50, элемент И-НЕ 51, элемент ИЛИ-НЕ 52, 53, -первый элемент гер 55,

Блок 6 содержит (фиг,5) регистр 56 адреса, регистр 57 данных, элемент И 58, триггеры 59, 60, элемент И 61, триггер 62, элемент ИЛИ 63, элементы И 64, 65, 66, элемент ИЛИ 67, магистральные приемопередатчики 68, 69, дешифратор 70 адреса.

Устройство осуществляет обмен информацией между мультиплексным каналом последовательного информационного обмена (МКИО) и периферийными устройствами, подключенными к локальной внешней магистрали параллельного) интерфейса (МПИ),

При этом обеспечивается реализация- двух процедур информационного обмена: обмен между активным устройством на магистрали МКИО и активным периферийным устройством на магистрали МПИ; обмен между МКИО и пассивной магистралью МПИ,

Б первом режиме устройство функционирует следующим образом.

Информация для транзитной передачи записывается передающей активной магистралью в общую зону резидентного блока 9 оперативной памяти и затем считывается из этой зоны принимающей активной магистралью. Оба обращения к блоку 9 осуществляются в режиме прямого доступа к памяти через внутреннюю магистраль 14, Очередностью обслуживания запросов на прямой доступ к памяти со стороны магистралей управляет блок 5, Таким образом, в первом режиме транзитная межмагистральная передача информации разделяется на две процедуры обмена: а - между магистралью МКИО 15 и блоком 9 оперативной памяти; б - между актив

ной магистралью 35 и общей зоной блока 9 оперативной памяти.

Процедура обмена а осуществляется следующим образом. Активное устройство ККИО (т.е. устройство, посылающее командное слово) передает на вход/выход 15 блока 1 сообщение последовательным биполярным двухуровневым фазоманипулированньм кодом без возврата к нулю (так называемым кодом Манчестер П). Первым в таком сообщении всегда передается командное слово. Принимая командное слово, блок 1 проверяет код и адрес на дос- товерность, преобразует код Манчестер П в параллельньй двоичный код, формирует управляющие сигналы Запись либо Чтение нли Сброс, Указанные сигналы передаются на входы блока 3 с выходов 19,20,23 блока 1,

При приеме информации из МКИО информационные слова, следующие за командным словом, преобразуются в блоке 1 из кода Манчестер П в параллель- ный двоичньш код и передаются в блок 3 с выхода 22. При передаче информации из устройства в МКИО параллель- ы двоичный код данных передается с выхода 21 блока 3 в блок 1,

В блоке 3 формируется исполнительный адрес ячейки памяти, и с выхода 26 посылается сигнал заявки на прямой доступ к памяти, поступающий на вход блока 5. В случае, если блок 5 приоритета разрешает обслуживание этой .заявки, с его выхода 27 на вход блока 2 поступает сигнал инициирования цикла прямого доступа к памяти (ПДП), а на первые входы разрешения блока 2 с выхода 28 блока 5 номер активного устройства, запросившего прямой доступ. Со входа/выхода блока 2 запрос прямого доступа по магистрали 4 передается в блок 7, который, завершив очередной цикл, переда- ет управление магистралью 1А блоку 2 на время выполнения одного канального цикла обмена. Блок 2 управляет обменом по магистрали 14 между адресованной ячейкой памяти и регистрами данных блока 3, При записи информации из МКИО она передается из входного регистра 44 данных блока 3 в адресованную ячейку памяти, а при чтении информации в МКИО она считывается из адресованной ячейки памяти в выходной регистр 45 данных блока 3 и далее передается в блок 1 для трансляции

88

в МК1ГО. После обмена информацией с регистрами блока 3 цикл прямого доступа заканчивается. Далее, если ведется передача серии информационных слов, в блоке 3 формируется НОБЫЙ исполнительный адрес ячейки памяти, запрос к блоку 5 приоритета на цикл для передачи одного слова и т.д,. .

Процедура обмена б выполняется следующим образом. Активное периферийное устройство на магистрали параллельного интерфейса обращается к ячейке 9 памяти как к пассивному внешнему устройству на этой магистрали, выставляя на магистрали адрес обращения и управляющие сигналы согласно протоколу обмена. Адрес запоминается в регистре 56 адреса блока 6, где также формируется исполнитель- ный адрес ячейки памяти и дешифруется дешифратором 70 адреса. Если ведется цикл Запись, то обмен с магистралью завершается записью передаваемого из этой магистрали слова данных в регистр 57 данных блока 6 и выдачей в магистраль ответного сигнала . Затем с выхода 32 блока 6 выдается сигнал запроса прямого доступа, поступающий на вход блока 5 приоритета. Далее выполняется указанная процедура- захвата магистрали 14 на один цикл прямого доступа и запись в этом цикле информации из регистра 56 данных блока 6 в адресованную ячейку 9 памяти под. управлением блока 2. В цикле Чтение магистраль параллельного интерфейса не отключается после записи адреса в регистр 56 и его дешифрации в дешифраторе 70, а происходит запрос цикла прямого доступа, в котором считанное слово данных из адресованной 1чейки 9 памяти через приемопередатчики 68 и 69 блока 6 с магистрали 14 выдается в магистраль параллельного интерфейса. На этом обмен с активным периферийным абонентом завершается.

Для обращения со стороны магистрали параллельного интерфейса в памяти 9 выделены зоны записи и чтения. Семафоры обмена между последовательной и параллельной магистралями реализованы программно путем введения РСЗ 10 и РСЧ 11, в которых передающая и принимающая магистрали устанавливают и считывают младший разряд перед

обменом и сбрасывают его по окончани обмена.

Блок 5 приоритета обеспечивает цикл обмена с внешними магистралями в порядке поступления от них заявок на ПДП; при одновременном поступлении заявок приоритет обслуживания имеет роль параллельного интерфейса

Второй режим обмена, т.е. между МКИО и пассивной магистралью параллельного интерфейса, осуществляется в программном режиме под управлением блока 7 либо в режиме прямого доступа под управлением блока 2. В первом случае блок 7 формирует исполнительный адрес пассивного (ведомого) устройства на магистрали параллельного интерфейса и соответствующие протокольные сигналы активного устройства Обмен ведется между регистрами блока 7 или ячейками памяти и внешним устройством, информационные, адресные и управляющие сигналы передаются через канальные приемопередатчики 68 и 69 блока 6, Во втором случае обмен ведется в указанном режиме прямого доступа непосредственно между регистрами блока 3 и внешним устройством на магистрали параллельного интерфейса без промежуточной записи в память что обеспечивает высокую скорость обмена. Управляющие сигналы, генерируемые блоком 2, транслируются при этом во внешнюю магистраль через приемопередатчики блока 6,

Первьй или второй режим обмена задается программно с соответствующим подключением разъема магистрали параллельного интерфейса. Блок 7 обеспечивает тестовый контроль устройства и программы обслуживания периферийных устройств,

Блок 3 работает следующим образом,

Адрес периферийного узла (интерфейсного процессора и магистрали 35) зафиксированный в формирователе 43, подается с выхода 25 блока 3 в блок Формирователь 43 запоминает адрес и число слов, поступающие из блока 1. Блок 3 обеспечивает прямой, инкремен тный и относительный способы адресации памяти и периферийных устройств. Запрос цикла прямого доступа к блоку 5 выдается элементом ИЛИ 46 по сигналам Запись или Чтение -, фор- мируемым блоком 1. Моменты вьщачи или приема информации на магистраль 14 из формирователя 43 адреса входно

5

0

5 5

0 6

0

0

5

го регистра 44 данных и выходного регистра 45 данных определяются управляющими сигналами, подаваемыми на входы блока 3 с выхода 18 блока,2,

Формула изобретения

1, Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом, содержащее первый блок коммутации информационных и управляющих сигналов, блок регистров адреса и данных, арифметико-логической блок, блоки оперативной и .постоянной памяти, блок управления прямым доступом, генератор тактовых импульсов, регистр адреса и селектор адреса, причем вход-выход первого блока коммутации информационных и управляющих сигналов является входом-выходом устройства для подключения к информационным и управляющим шинам последовательного канала, первый, второй, третий, четвертый, пятый выходы блока коммутации информационных и управляющих сигналов соединены соответственно с адресным, установочным, информационным, первым и вторым синхронизирующими входами блока регистров адреса и данных, первый и второй выходы которого соединены соответственно с информационным и адресным входами первого блока коммутации информационных и управляющих сигналов, первый выход блока управления прямым доступом соединен с третьим синхронизирующим входом блока регистров адреса и. данных, информационные и управляющие входы-выходы которого через внутреннюю магистраль соединены с информационными и управляющими входами-выходами арифметико- логического блока и блоков оперативной и постоянной памяти, блока уп- равл ения прямь М доступом, регистра адреса, селектора адреса, выход которого соединен с синхровходами блоков оперативной и постоянной памяти и регистра .адреса, выход которого соединен с адресными входами блоков оперативной и постоянной памяти, выход генератора тактовых импульсов соединен, с тактовыми входами арифметико- логического блока и блока управления прямым доступом, отличающееся тем, что, с целью расширения области применения, в устройство введены блок приоритета, регистры состояния записи и чте)1ия, второй блок

коммутации и)формапионных и управляющих сигналов, первый информационный и упрявляющиГт вход-выход которого япляется входом-выходом устройства для ггодключения к информационной, и упр;111.11Я|(11дей гпинам магистрали параллельного интерфейса, второй информа- ционныГг и управляющий вход-выход второго Олока коммутации информационных и упрарляюпшх сигналов, информационные входы-выходы регистров состояния записи и чтения через внутреннюю -магистраль соединены с входами-выходам информационных и управляющих сигна- лов арифметико-логического блока, выходы селектора адреса и регистра адреса соединены соответственно с режимными и информационными входами регистров состояния записи и чтения, выход второго блока коммутации информационных и управляющих сигналов соединен с первым входом запроса блока приоритета, первый выход которого соединен с входом инициирования бло- ка управления прямьп доступом, второй выход которого сотединен с установочным входом блока приоритета, второй выход которого соединен с входами разрешения второго блока ком- мутации информационных и управляющих сигналов и блока управления прямым .доступом, третий выход которого соединен с входом установки второго блока коммутации информационных и управляющих сигналов, третий выход блока регистров адреса и данных соединен с вторым входом запроса блока приоритета.

2, Устройство по п.1, о т л и - ча ющееся тем, что блок управления прямым доступом содержит узел формирователей записи и чтения, шифратор адреса и данных, четыре элемента И, первые входы которых образуют вход разреше ния блока, выходы перво- го и второго элементов И образуют третий выход блока, а выходы третьег и четвертого элементов И образуют

первый выход блока, первый и второй входы узла формирователей записи и чтения соединены соответственно с входом инициирования и тактовым входом блока, первый выход узла формирователей записи и чтения соединен с вторыми входами первого и третьего элементов И и с первым входом шифратора адреса и данных, второй выход узла формирователей записи и чтения соединен с вторыми входами второго и четвертого элементов И и с вторым входом шифратора адреса и данных, вход-выход которого является информационным и управляющим входом-выходом блока.

3. Устройство по п,1, отличающееся тем, что блок приоритета содержит два триггера, три элемента И, элементы И-НЕ, ИЛИ, ИЛИ- НЕ, причем первые входы первого и второго элементов И объединены и подсоединены к первому входу запроса блока, второй вход запроса которого соединен с первым входом третьего элемента И и вторым входом второго элемента И, выход которого соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с инверсными выходами первого и второго триггеров, прямой выход первого триггера соединен с первым входом элемента ИЛИ, вторым входом третьего элемента И, выход которого соединен с установочным входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, вторым входом элемента ИЛИ, выход которого является первым выходом блока, установочный вход которого соединен с синкровходами первого и второго триггеров, прямые выходы которого образуют второй выход блока, выход элемента И-НЕ соединен с третьим выходом первого элемента И, выход которого соединен с установочным входом первого триггера.

Фиэ. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1762308A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Устройство относится к области вычислительной техники, в частности к устройствам информационного обмена в вычислительных сетях между главной вычислительной машиной и удаленными периферийными устройствами. Устройство обеспечивает скоростной обмен между стандартной последовательной и различными модификациями стандартной параллельной магистрали в режимах транзитного прямого доступа при резидентном программно-аппаратном контроле. Цель изобретения - расширение области применения. Устройство содержит два блока коммутации информационных и управляющих сигналов, арифметико-логический блок, память с блоком управления прямым доступом, блок регистров адреса и блок приоритета, регистры состояния записи и чтения. 2 з.п. ф-лы, 5 ил. с € (Л

w

Загтрос /

SanpocZ

36

8А

ВА

U1

L.

п

37

38

39

40

8x/g6/x1

фиг. г

J

n

j VUlJ

Составитель Л.Стернин Редактор О.Спесивых Техред А.Кравчук Корректор В.Романенко

Заказ 6507/49

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

BJr/36/xZ

т.

I

Фиг.5

Подписное

| Патент США № 4404651, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Насос | 1917 |

|

SU13A1 |

| Патент США № 4417320, кл; G 06 F 3/04, опублик | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1988-12-15—Публикация

1986-09-10—Подача