Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем.

Известно устройство, содержащее блок памяти, мультиплексор, триггер, шинный формирователь.

Недостатком известного устройства является ограниченные функциональные возможности, обусловленные отсутствием средств межпроцессорного обмена через общую память.

Известно устройство, содержащее блок памяти, мультиплексор, триггер, шинный формирователь.

Недостатком указанного аналога является ограниченные функциональные возможности, вызванные отсутствием средств двустороннего обмена информацией между

оперативной памятью и каждым из сопрягаемых с ней процессоров.

Наиболее близким к предлагаемому является устройство для сопряжения двух процессоров через общую память, содержащее блок опертивной памяти, мультиплексор адреса, первый шинный формирователь, три. - гер, второй шинный формирователь, мультиплексор управления оперативной памятью и элемент НЕ, причем первый л второй информационные входы мультиплексора адреса соединены с адресными выходами соответственно первого и второ го процессоров, информационный выход мультиплексора адреса соединен с адресным входом блока оперативной памяти, информационный вход-выход которого соединен с первым информационным входом-выходом первого шинного формирователя, второй информационный вход-выход

ш ы

которого соединен с входом-выходом данных первого процессора устройства, выход триггера соединен Ј управляющим входом мультиплексора адреса и с входом разрешения первого шинного формирователя, первый информационный вход-выход второго шинного формирователя соединен с инфор- мацио нным входом-выходом блока оперативной памяти, второй информационный вход-выход второго шинного формирователя соединен с входом-выходом данных второго процессора устройства, выход запроса которого соединен С инверсным входом сброса триггера, инверсный вход установки которого соединен с выходом запроса от первого процессора устройства, выход уп- рэвлеиия чтением-записью от первого процессора которого соединен с управляющим входом первого шинного формирователя и первым информационным входом первой группы мультиплексора управления оперативной памятью, второй информационный вход первой группы которого соединен с выходом управления объемом от первого процессора устройства, выход управления чтением - записью от второго процессора устройства соединен с управляющим входом второго шинного формирователя и первым информационным входом второй группы мультиплексора управления оперативной памятью, второй информационный вход второй группы которого соединен с выходом управления обменом от второго процессора устройства, первый информационный выход мультиплексора управления оперативной памятью соединен с входом управления чтением-записыо блока оперативной памяти, вход управления обменом которого соединен с вторым информационным выходом мультиплексора управления оперативной памятью, вход управления которого соединен с выходом триггера, входом подтверждения запроса от первого процессора устройства и входом элемента НЕ, выход которого соединен с

входом разрешения второго шинного формирователя и входом подтверждения запроса второму процессору устройства

Недостатком устройства - прототипа явлёйтся низкая оперативность обмена, которая обусловлена следующим. В устройстве - прототипе осуществляется двусторонний обмен информацией между общей памятью и каждым из сопрягаемых с ней процессоров. Первый (второй) процессор, выставив запрос на доступ и общей памяти и получив разрешение на обмен данными обеспечивает обмен массивом слой данных между общей памятью и своей . памятью. При этом второй (первый) процессор, выставив запрос на доступ к общей памяти, непроизводительно простаивает, ожидая окончания обмена данными между общей памятью и первым процессором. До5 ступ к общей памяти второй (первый) процессор получает только в момент обмена последним словом данных из массива передаваемой информации между первым (вторым) процессором, В этом случае снижается

0 оперативность обмена данными, т.к. время доступа процессора в общей памяти будет равно сумме времен передачи всех слов данных из массива передаваемой информации между другим процессором и общей па5 мятью. В устройстве - прототипе отсутствуют технические средства, позволяющие обеспечить поочередное обслуживание двух процессоров в режиме передачи одиночных слов данных между процессорами и

0 общей памятью. Невозможность быстрого доступа к общей памяти существенно понижает оперативность обмена данными в многопроцессорных вычислительных системах, В связи с этим целью изобретения является

5 повышение оперативности обмена данными предлагаемого устройства.

Поставленная цель Достигается тем. что в устройство для сопряжения двух процессоров через общую память, содержащее

0 блок оперативной памяти, первый и второй шинные формирователи, мультиплексор адреса, мультиплексор управления, первый триггер, элемент НЕ, причем первый и второй информационные входы мультиплбкси5 ра адреса соединены соответственно с адресными входами первого и второго процессоров, инфорационный вход мультиплексора адреса соединен с адресным входом блока оперативной памяти, инфор

0 мационный вход- выход которого соединен с первыми информационными входами - выходами первого и второго шинных формирователей, вторые информационные входы-выходы первого и второго шинных

5 формирователей соединены с входами - выходами данных соответственно первого и второго процессоров, входы управления чтением-записью которых соединены соответственно с первыми управляющими

0 входами первого и второго шинных формирователей и первыми информационными входами первой и второй групп входов мультиплексора управления, входы управления обменом первого и второго процессоров со5 единены соответственно со вторыми информационными входами первой и второй групп входов мультиплексора управления, первый и второй информационные выходы которого соединены соответственно со входами управления чтением-записью и управления обменом блока оперативной памяти, выход элемента НЕ соединен со вторым управляющим входом второго шинного формирователя и выходом разрешения доступа второго процессора, дополнительно введены второй, третий и четвертый триггеры, счетчик, первый и второй коммутаторы, пер- вый-шестой элементы И, первый-четвертый элементы ИЛИ, одновибратор, причем входы запроса доступа первого и второго процессоров соединены соответственно с первым и вторым входами первого коммутатора и с первыми входами соответственно первого и второго элементов ИЛИ, выходы которых соединены соответственно с единичным и нулевым входами первого триггера, выход первого триггера соединен с прямым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход третьего элемнета ИЛИ соединен с адресными входами мультиплексоров адреса и управления, со вторым управляющим входом первого шинного формирователя, выходом разрешения доступа первому процессору и входам элемента НЕ, вход срочного запроса доступа первого процессора соединен с третьим входом первого коммутатора, первым входом второго элемента И, прямым и инверсным входами соответственно третьего и четвертого элементов И, выходы которых соединены соответственно со вторыми входами первого и второго элементов ИЛИ, вход срочного запроса второго процессора соединен с четвертым входам первого коммутатора, с прямым и инверсным входами соответственно четвертого и третьего элементов И, с вторым входом второго элемента И, выход которого соединен с первым входом четвертого элемента И, с первым инверсным и первым прямым входами второго коммутатора, выход первого коммутатора соединен с единичным входом второго триггера, со вторым инверсным и вторым прямым входами второго коммутатора, выход которого соединен с нулевым входом третьего триггера, выход третьего триггера соединен с инверсным входом первого элемента И, первым входом пятого элемента И, входом одновибратора и нулевым входом второго триггера, выход которого соединен с первым входом шестого элемента И, выход которого соединен со счетным входом счетчика, выход одновибратора соединен с нулевым входом счетчика, выход которого соединен со вторым входом четвертого элемента ИЛИ, выход четвертого элемента ИЛИ соединен с единичным входом третьего триггера, вход синхронизации устройства соединен со вторым входом шестого

элемента И и вторым входом пятого элемента И, выход которого соединен со счетным входом четвертого триггера, выход четвертого триггера соединен со вторым входом 5 третьего элемента ИЛИ.

Сущность изобретения состоит в повышении оперативности обмена данными путем обеспечения возможности поочередного пословного обмена данными

10 между общей памятью и каждым из сопрягаемых с ней процессоров.

Обращение к общей памяти процессоры осуществляют в режимах одиночного и группового доступов. Причем режим груп15 нового доступа подразделяется на немедленного и отсрочанного группового доступа. Для обращения к общей памяти процессоры формируют сигналы запроса доступа по первым и вторым входам если

20 процессоры формируют сигналы запроса доступа по первым входам, то устройство обслуживает тот процессор, который первым выдал сТлгнал запроса доступа, в режиме одиночного доступа к общей памяти1.

25 После обмена всем массивам информации между одним процессором и общей памятью устройство обеспечивает обмен информацией между другим процессором и общей памятью, реализуя режим одиночко0 го доступа к оперативной памяти Кроме того, в данном режиме устройство может функционировать при формировании одним из процессоров сигнала запроса доступа к общей памяти по второму входу

5 Режим немедленного группового доступа к общей памяти обеспечивается одновре- менным формированием процессорами сигналов запроса доступа по вторым входам В данном случае устройство обеспечи0 вает обмен одним словом данных между общей памятью и одним из процессоров. После передачи одного слова данных между общей памятью и одним из процессоров устройство обеспечивает обмен одним сло5 вом данных между другим процессором и памятью Такой обмен данными происходит до момента окончания передачи всего массива информации.

Режим отсроченного группового досту0 па к общей памяти релаизуется, когда устройство обслуживает один из процессоров в режиме одиночного доступа, а другой процессор формирует сигнал запроса доступа по второму входу. После приема сигнала

5 запроса доступа по второму входу от второго процессора и истчечения допустимого времени ожидания вторым процессором доступа к общей памяти устройство начинает обслуживать поочередно два процессора. Досле обмена одним словом данных между

общей памятью и одним из процессоров устройство обеспечивает передачу одного слова данных между общей памятью и другим процессором.

Таким образом, процессору, формирующему сигнал запроса доступа по второму входу, общая память представляется не после окончания обмена всем массивом информации между другим процессором и общей памятью, а после окончания допустимого времени ожидания. Оставшийся массив данных, передаваемых между общей памятью и процессором, который устройство обслуживало до поступления сигнала запроса доступа по второму входу от другого процессора, будет передаваться на фоне обмена данными между общзй памятью и процессором, сформировавшим сигнал запроса доступа по второму входу.

Режим отсроченного группового доступа к общей памяти может также обеспечиваться в том случае, когда устройство обслуживает один из процессоров, сформировавшем сигнал запроса доступа по второму входу в режиме одиночного доступа к общей памяти, а второй процессор формирует сигнал запроса доступа по первому входу.

Таким образом, совмещенное обслуживание двух процессоров при доступе к общей памяти существенно повышает оперативность обмена данными.

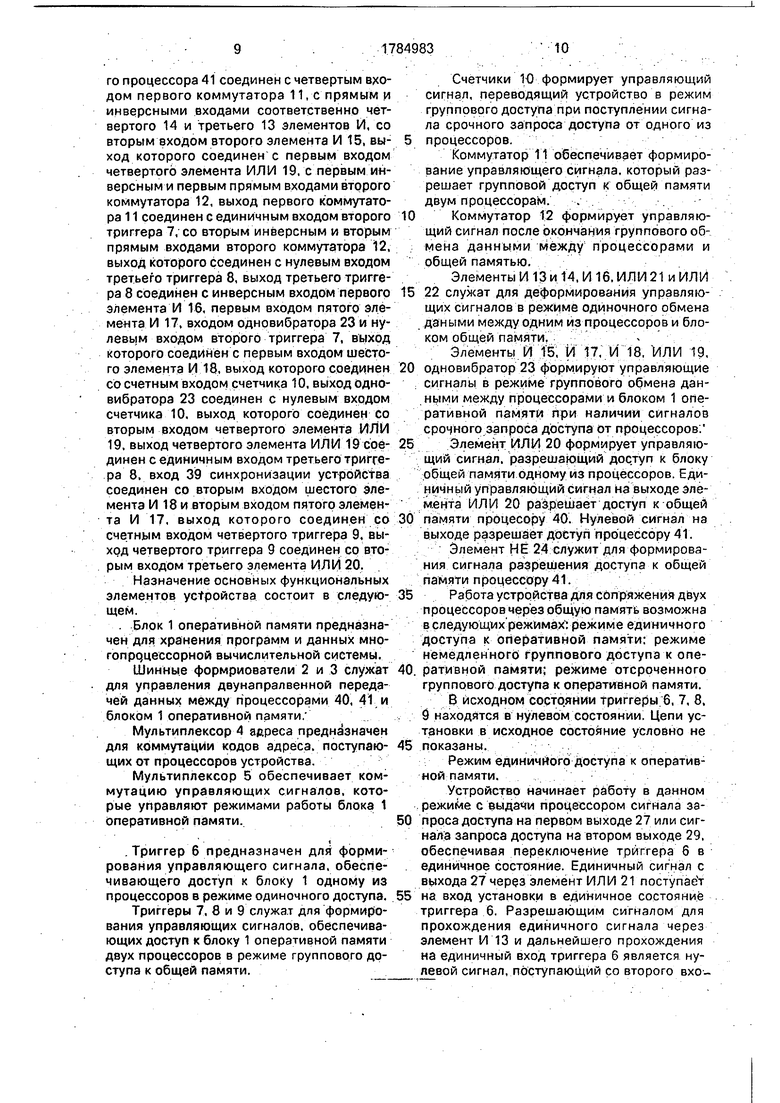

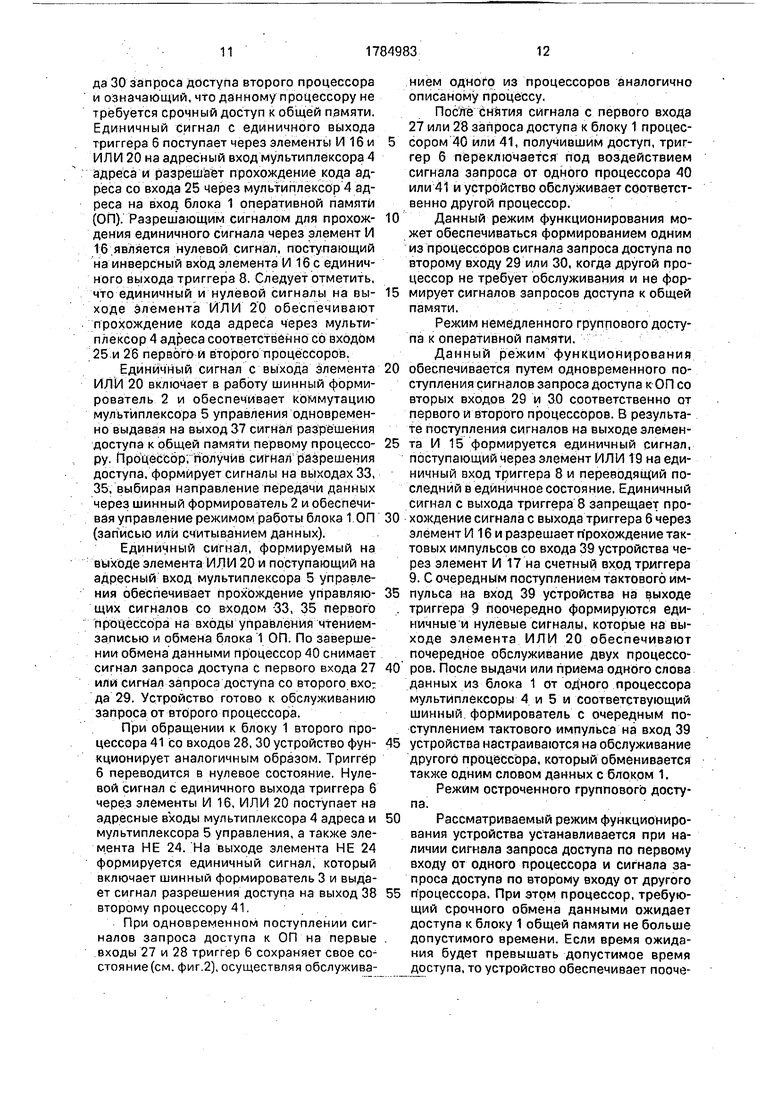

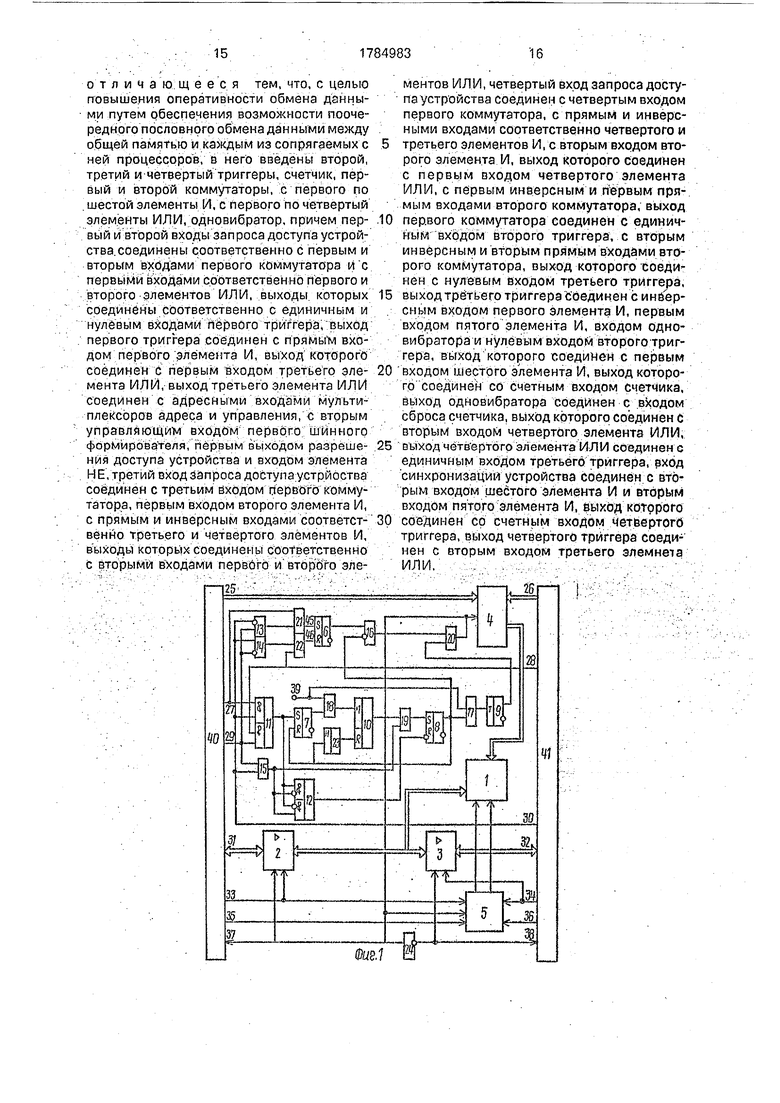

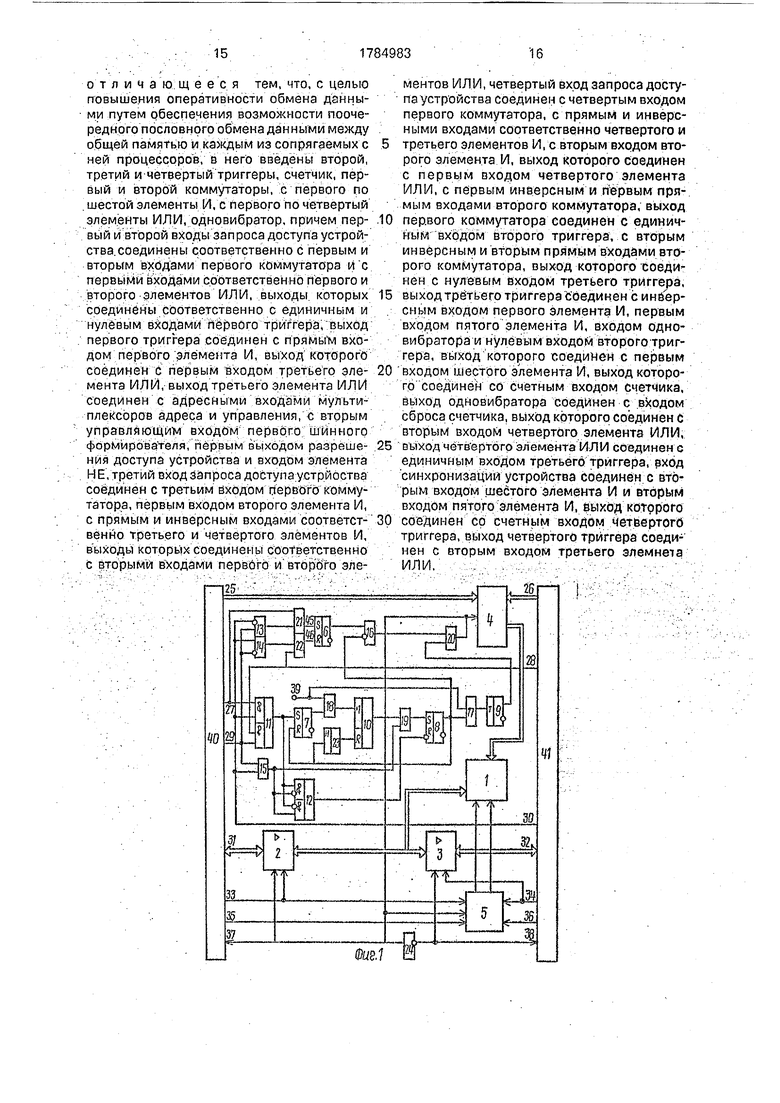

На фиг. 1 представлена фукнциональная схема устройства; на фиг,2 - функциональная схема триггера 6.

Устройство для сопряжения двух процессоров (фиг.1) содержит блок оперативной памяти 1, первый 2 и второй 3 шинные формирователи, мультиплексор адреса 4, мультиплексор управления 5, первый триггер 6, второй триггер 7, третий триггер 8, четвертый триггер 9, счетчик 10, первый 11 и второй 12 коммутаторы, третий 13, четвертый 14, второй 15. первый 16, пятый 17 и шестой 18элементы И, четвертый 19,третий 20, первый 21 и второй 22 элементы ИЛИ, одновибратор 23, элемент НЕ 24, адресные входы 25и 26, первый и второй входы запросов доступа 27 и 28, соответственно от пер- второго процессоров, третий и четвертый входы запросов доступа 29 и 30, соответственно первого и второго процессоров, входы-выходы данных 31 и 32, входы управления чтением - записью 33 и 34, входы упавления обменом 35 и 36, выходы разрешения доступа 37 и 38, вход 39 синхронизации устройства, первый 40 и второй 41 процессоры.

Триггер 6 (фиг.2) содержит триггер 42, первый 43, второй 44 элементы И.

Первый и второй информационные входы мультиплексора 4 адреса соединены соответственно с адресными входами 25, 26 первого 40 и второго 41 процессоров, информационный вход мультиплексора 4 адреса соединен с адресным входом блока 1 оперативной памяти, информационный вход-выход которого соединен с первыми информационными входами-выходами пер0 вого 2 и второго 3 шинных формирователей, вторые информационные входы-выходы первого 2 и второго 3 шинных формирователей соединены с входами-выходами данных 31,32, соответственно первого 40 и второго

5 41 процессоров, входы управления чтением-записью 33, 34 которых соединены соответственно с первыми управляющими входами первого 2 и второго 3 шинных формирователей и первыми информационными

0 входами первой и второй групп входов мультиплексора 5 управления, входы управления обменом 35, 36 первого 40 и второго 4 процессоров соединены соответственно со вторыми информационными входами пер5 вой и второй групп входов мультиплексора 5 управления, первый и второй информационные выходы которого соединены соответственно со входами управления чтением-записью и управления обменом

0 блока 1 оперативной памяти, выход элемента НЕ 24 соединен со вторым управляющим входом второго 3 шинного формирователя и выходом 38 разрешения доступа второго процессора, первые входы запроса доступа

5 27,28 первого 40 и второго 41 процессоров соединены соответственно с первым и вторым входами первого 11 коммутатора и с первыми входами соответственно первого 21 и второго 22 элементов ИЛИ, выходы

0 которых соединены соответственно с единичным и нулевым входами первого триггера б, выход первого триггера 6 соединен с прямым входом первого элемента И 16, выход которого соединен с первым входом

5 третьего элемента ИЛИ 20, выход третьего элемента ИЛИ 20 соединен с адресными входами мультиплексоров адреса 4 и управления 5, со вторым управляющим входом первого шинного формирователя 2, выхо0 дом 37 разрешения доступа первому процессору 40 и входом элемента НЕ 24, второй вход 29 запроса доступа первого процессора 40 соединен с третьим входом первого коммутатора 11, первым входом второго

5 Элемента И 15, с прямым и инверсным входами соответственно третьего 13 и четвертого 14 элементов И, выходы которых соединены соответственно со вторыми входами первого 21 и второго 22 элементов ИЛИ, второй вход 30 запроса доступа второго процессора 41 соединен с четвертым входом первого коммутатора 11, с прямым и инверсными входами соответственно четвертого 14 и третьего 13 элементов И, со вторым входом второго элемента И 15, выход которого соединен с первым входом четвертого элемента ИЛИ 19, с первым инверсным и первым прямым входами второго коммутатора 12, выход первого коммутатора 11 соединен с единичным входом второго триггера 7, со вторым инверсным и вторым прямым входами второго коммутатора 12, выход которого соединен с нулевым входом третьего триггера 8, выход третьего триггера 8 соединен с инверсным входом первого элемента И 16, первым входом пятого эле- мета И 17, входом одновибратора 23 и нулевым входом второго триггера 7, выход которого соединен с первым входом шестого элемента И 18, выход которого соединен со счетным входом счетчика 10, выход одно- вибратора 23 соединен с нулевым входом счетчика 10. выход которого соединен со вторым входом четвертого элемента ИЛИ 19, выход четвертого элемента ИЛИ 19 соединен с единичным входом третьего триггера 8, вход 39 синхронизации устройства соединен со вторым входом шестого элемента И 18 и вторым входом пятого элемента И 17, выход которого соединен со счетным входом четвертого триггера 9, выход четвертого триггера 9 соединен со вторым входом третьего элемента ИЛИ 20,

Назначение основных функциональных элементов устройства состоит в следующем.

Блок 1 оперативной памяти предназначен для хранения программ и данных многопроцессорной вычислительной системы.

Шинные формриователи 2 и 3 служат для управления двунапралвенной передачей данных между процессорами 40, 41 и блоком 1 оперативной памяти;

Мультиплексор 4 адреса предназначен для коммутации кодов адреса, поступающих от процессоров устройства.

Мультиплексор 5 обеспечивает коммутацию управляющих сигналов, которые управляют режимами работы блока 1 оперативной памяти.

Триггер 6 предназначен для формирования управляющего сигнала, обеспечивающего доступ к блоку 1 одному из процессоров в режиме одиночного доступа.

Триггеры 7, 8 и 9 служат для формирования управляющих сигналов, обеспечивающих доступ к блоку 1 оперативной памяти двух процессоров в режиме группового доступа к общей памяти.

Счетчики 10 формирует управляющий сигнал, переводящий устройство в режим группового доступа при поступлении сигнала срочного запроса доступа от одного из 5 процессоров.

Коммутатор 11 обеспечивает формирование управляющего сигнала, который разрешает групповой доступ к общей памяти двум процессорам.

0Коммутатор 12 формирует управляющий сигнал после окончания группового обмена данными между процессорами и общей памятью.

Элементы И 13 и 14, И 16, ИЛИ 21 и ИЛИ 5 22 служат для деформирования управляющих сигналов в режиме одиночного обмена даными между одним из процессоров и блоком общей памяти.

Элементы И 15, И 17, И 18, ИЛИ 19, 0 одновибратор 23 формируют управляющие сигналы в режиме группового обмена данными между процессорами и блоком 1 оперативной памяти при наличии сигналов срочного запроса доступа от процессоров. 5 Элемент ИЛИ 20 формирует управляющий сигнал, разрешающий доступ к блоку общей памяти одному из процессоров. Единичный управляющий сигнал на выходе элемента ИЛИ 20 разрешает доступ к общей 0 памяти процесору 40. Нулевой сигнал на выходе разрешает доступ процессору 41.

Элемент НЕ 24 служит для формирования сигнала разрешения доступа к общей памяти процессору 41.

5 Работа устройства для сопряжения двух процессоров через общую память возможна в следующих режимах1; режиме единичного доступа к оперативной памяти: режиме немедленного группового доступа к опе- 0. ративной памяти; режиме отсроченного группового доступа к оперативной памяти. В исходном состоянии триггеры 6, 7, 8, 9 находятся в нулевом состоянии. Цепи установки в исходное состояние условно не 5 показаны.

Режим единичного доступа к оперативной памяти.

Устройство начинает работу в данном режиме с выдачи процессором сигнала за- 0 проса доступа на первом выходе 27 или сигнала запроса доступа на втором выходе 29, обеспечивая переключение триггера б в единичное состояние. Единичный сигнал с выхода 27 через элемент ИЛИ 21 поступает 5 на вход установки в единичное состояние триггера 6. Разрешающим сигналом для прохождения единичного сигнала через элемент И 13 и дальнейшего прохождения на единичный вход триггера 6 является нулевой сигнал, поступающий со второго входа 30 запроса доступа второго процессора и означающий, что данному процессору не требуется срочный доступ к общей памяти. Единичный сигнал с единичного выхода триггера б поступает через элементы И 16 и ИЛИ 20 на адресный вход мультиплексора 4 адреса и разрешает прохождение кода адреса со входа 25 через мультиплексор 4 адреса на вход блока 1 оперативной памяти (ОП). Разрешающим сигналом для прохож- дения единичного сигнала через элемент И 16 является нулевой сигнал, поступающий на инверсный вход элемента И 16 с единичного выхода триггера 8. Следует отметить, что единичный и нулевой сигналы на вы- ходе элемента ИЛИ 20 обеспечивают прохождение кода адреса через мультиплексор 4 адреса соответственно со входом 25 и 26 первого и второго процессоров.

Единичный сигнал с выхода элемента ИЛИ 20 включает в работу шинный формирователь 2 и обеспечивает коммутацию мультиплексора 5 управления одновременно выдавая на выход 37 сигнал разрешения доступа к общей памяти первому процессе- ру Процессор, получив сигнал разрешения доступа, формирует сигналы на выходах 33, 35, выбирая направление передачи данных через шинный формирователь 2 и обеспечивая управление режимом работы блока 1 ОП (записью или считыванием данных).

Единичный сигнал, формируемый на выходе элемента ИЛИ 20 и поступающий на адресный вход мультиплексора 5 управления обеспечивает прохождение управляю- щих сигналов со входом 33, 35 первого процессора на входы управления чтением- записью и обмена блока 1 ОП. По завершении обмена данными процессор 40 снимает сигнал запроса доступа с первого входа 27 или сигнал запроса доступа со второго вхо: да 29. Устройство готово к обслуживанию запроса от второго процессора.

При обращении к блоку 1 второго процессора 41 со входов 28, 30 устройство фун- кционирует аналогичным образом. Триггер б переводится в нулевое состояние. Нулевой сигнал с единичного выхода триггера 6 через элементы И 16, ИЛИ 20 поступает на адресные входы мультиплексора 4 адреса и мультиплексора 5 управления, а также элемента НЕ 24. На выходе элемента НЕ 24 формируется единичный сигнал, который включает шинный формирователь 3 и выдает сигнал разрешения доступа на выход 38 второму процессору 41

При одновременном поступлении сигналов запроса доступа к ОП на первые входы 27 и 28 триггер 6 сохраняет свое состояние (см. фиг 2), осуществляя обслуживанием одного из процессоров аналогично описаному процессу.

После снятия сигнала с первого входа 27 или 28 запроса доступа к блоку 1 процессором 40 или 41, получившим доступ, триггер б переключается под воздействием сигнала запроса от одного процессора 40 или 41 и устройство обслуживает соответственно другой процессор.

Данный режим функционирования может обеспечиваться формированием одним из процессоров сигнала запроса доступа по второму входу 29 или 30, когда другой процессор не требует обслуживания и не формирует сигналов запросов доступа к общей памяти,

Режим немедленного группового доступа к оперативной памяти.

Данный режим функционирования обеспечивается путем одновременного поступления сигналов запроса доступа к ОП со вторых входов 29 и 30 соответственно от первого и второго процессоров. В результате поступления сигналов на выходе элемента И 15 формируется единичный сигнал, поступающий через элемент ИЛ И 19 на единичный вход триггера 8 и переводящий последний в единичное состояние. Единичный сигнал с выхода триггера 8 запрещает прохождение сигнала с выхода триггера 6 через элемент И 16 и разрешает прохождение тактовых импульсов со входа 39 устройства через элемент И 17 на счетный вход триггера 9. С очередным поступлением тактового импульса на вход 39 устройства на выходе триггера 9 поочередно формируются единичные и нулевые сигналы, которые на выходе элемента ИЛИ 20 обеспечивают почередное обслуживание двух процессоров. После выдачи или приема одного слова данных из блока 1 от одного процессора мультиплексоры 4 и 5 и Соответствующий шинный формирователь с очередным поступлением тактового импульса на вход 39 устройства настраиваются на обслуживание другого процессора, который обменивается также одним словом данных с блоком 1.

Режим встреченного группового доступа.

Рассматриваемый режим функционирования устройства устанавливается при наличии сигнала запроса доступа по первому входу от одного процессора и сигнала запроса доступа по второму входу от другого процессора. При этом процессор, требующий срочного обмена данными ожидает доступа к блоку 1 общей памяти не больше допустимого времени. Если время ожидания будет превышать допустимое время доступа, то устройство обеспечивает поочередное обслуживание процессоров. Время ожидания является одинаковым для процессоров и устанавливают счетчиком 10,

Рассмотрим работу устройства при выдаче на первый вход 27 сигнала запроса доступа к блоку 1 от первого процессора и поступлении сигнала запроса доступа со второго входа 30 от второго процессора. В результате поступления данных сигналов на выходе коммутатора 11 формируется единичный сигнал, поступающий на единичный вход триггера 7 и переводящий последний в единичное состояние. Единичный сигнал с единичного выхода триггера 7 разрешает прохождение тактовых импульсов со входа- ,ми 39 устройства через элемент И 18 на вход счетчика 10. Время ожидания доступа к общей памяти процессором, выдавшим сигнал запроса доступа по второму входу, определяется разрядностью счетчика 10. При переполнении-счетчика 10 на его выходе формируется единичный сигнала, проходящий через элемент ИЛИ 19 и переводящий триггер 8 в единичное состояние. Единичный сигнал с выхода триггера 8 разрешает прохождение тактовых импульсов через элемент И 17 и запрещает прохождение сигналов через элемент И 16, а также устанавливает триггер 7 и счетчик 10 в исходное (нулевое) состояние. Причем формирование сигнала установки в исходное состояние счетчика 10 обеспечивается одновибрато- ром 23 с задержкой.

С выхода элемента И 17 на счетный вход триггера 9 начинают поступать тактовые импульсы, которые изменяют его состояние, Единичное и нулевое состояние триггера 9 обеспечивает поочередное предоставление процессором общей памяти.

Следует отметить, что при поочередном обслуживании процессоров на выходе коммутатора 12 формируется единичный сигнал, поступающий на нулевой вход триггера 8, По окончании режима группового доступа к оперативной памяти на выходе коммутатора 12 снимается единичный сигнал, по заднему фронту которого триггер 8 устанавливается в исходное (нулевое) состояние.

При поступлении на первый вход 28 сигнала запроса доступа от второго прцоессо- ра и на второй вход 29 сигнала запроса доступа от первого процессора устройство функционирует аналогично описанному процессору.

После снятия одним из процессоров сигнала запроса доступа устройство переходит в режим одиночного доступа к оперативной памяти, обслуживая другой процессор.

Данный режим функцинирования мо- жет быть реализован, если устройство обслуживает один из процессоров, выдавшим сигнал запроса доступа по второму входу, и 5 в этот момент формируется сигнал запроса доступа по первому входу. Например, на первый вход 29 поступает сигнал запроса доступа от первого процессора 40, который через элементы И 13 и ИЛИ 21 устанавлива0 ет триггер 6 в единичное состояние. Единичное состояние триггера 6 обеспечивает обслуживание первого триггера 40, Если в этот момент приходит сигнал запроса доступа по первому входу 28 от второго процес5 сора 41, то на выходе коммутатора 11 будет формироваться единичный сигнал, устанавливающий триггер 7 в единичное состояние. Единичный сигнал с выхода триггера 7 разрешает прохождение тактовых импульсов

0 через элемент И 18 на счетный вход счетчика 10, обеспечивая отсроченный режим группового доступа к общей памяти. Формула изобретения Устройство для сопряжения двух про5 цессоров, содержащее блок оперативной памяти, первый и второй шинные формирователи, мультиплексор адреса, мультиплексор управления, первый триггер, элемент НЕ, причем первый и второй информацион0 ные входьгмультиплексора адреса являются соответственно первым и вторым адресными входами устройства, информационный выход мультиплексора адреса соединен с адресным входом блока оперативной памя5 ти, информзционный вход-выход которого соединен с первыми информационными входами-выходами первого и второго шинных формирователей, вторые информационные входы-выходы первого и второго

0- шинных формирователей соединены с первым и вторым входами-выходами данных устройства, первый и второй входы управления чтением-записью устройства соединены соответственно с первыми

5 управляющими входами первого и второго шинных формирователей и первыми информационными входами первой и второй групп входов мультиплексора управления, первый и второй входы управления обме0 ном устройства соединены соответственно с вторыми информационными входами первой и второй групп входов мультиплексора управления, первый и второй инфор- мационйые выходы которого соединены

5 соответственно с входами управления чтением-записью и управления обменом блока оперативной памяти, выход элемента Н Е соединен с вторым управляющим входом второго шинного формирователя и вторым входом разрешения доступа устройство,

отличающееся тем, что, с целью повышения оперативности обмена данными путем обеспечения возможности поочередного пословного обмена данными между общей памятью и каждым из сопрягаемых с ней процессоров, в него введены второй, третий и четвертый триггеры, счетчик, первый и второй коммутаторы, с первого по шестой элементы И, с первого по четвертый элементы ИЛИ, одновибратор, причем пер- вый и второй входы запроса доступа устройства соединены соответственно с первым и вторым входами первого коммутатора и с первыми входами соответственно первого и второго элементов ИЛИ, выходы которых соединены соответственно с единичным и нулевым входами первого триггера, выход первого триггера соединен с прямым входом первого элемента И, выход которого соединен с первым входом третьего эле- мента ИЛИ, выход третьего элемента ИЛИ соединен с адресными входами мультиплексоров адреса и управления, с вторым управляющим входом первого шинного формирователя, первым выходом разреше- ния доступа устройства и входом элемента НЕ, третий вход запроса доступа устрйоства соединен с третьим входом первого коммутатора, первым входом второго элемента И, с прямым и инверсным входами соответст- венно третьего и четвертого элементов И, выходы которых соединены соответственно с вторыми входами первого и второго элементов ИЛИ, четвертый вход запроса доступа устройства соединен с четвертым входом первого коммутатора, с прямым и инверсными входами соответственно четвертого и третьего элементов И, с вторым входом второго элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, с первым инверсным и первым прямым входами второго коммутатора, выход первого коммутатора соединен с единичным входом второго триггера, с вторым инверсным и вторым прямым входами второго коммутатора, выход которого соединен с нулевым входом третьего триггера, выход третьего триггера соединен с инбер- сным входом первого элемента И, первым входом пятого элемента И, входом одно- вибратора и нулевым входом второго триггера, выход которого соединен с первым входом шестого элемента И, выход которого соединен со счетным входом счетчика, выход одновибратора соединен с входом сброса счетчика, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход четвертого элемента ИЛИ соединен с единичным входом третьего триггера, вход синхронизации устройства соединен с вторым входом шестого элемента И и вторым входом пятого элемента И, выход которого соединен со счетным входом четвертого триггера, выход четвертого триггера соединен с вторым входом третьего элемнета ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух процессоров через общую память | 1990 |

|

SU1758647A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем. Цель изобретения - повышение оперативности обмена данными. Устройство содержит блок оперативной памяти, первый и второй шйтгные формирователи, мультиплексор адреса, мультиплексор управления, с первого по четвертый триггеры, счетчик, первый и второй коммутаторы, с первого по шестой элементы И, с первого п э четвертый элементы ИЛИ, одновибратор, элемент НЕ. 2 ил.

Ю о-

«Е.

т

Триггер

S

W

Фиг. 2

| Патент США NJ 4400801, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух процессоров через общую память | 1987 |

|

SU1515172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1992-12-30—Публикация

1991-02-18—Подача