первым входом элемента ИЛИ, второй вход и выход -которого являются соотнетственно входом синхроннза1ши и вторым управляющим выходом узла гене рации адресов, при этом узел синхронизации обмена содержит регистр сдвига, пять элементов И, элемент задержки и элемент НЕ, причем информационнь(й вход регистра сдвига соединен с информационным входом узл синхронизации обмена, вход сброса .через элемент задержки соединен с входом сброса узла, первый вход первого элемента И соединен через элемент НЕ с входом задания направления обмена узла и первыми входами второго и третьего элементов И, а вЬ1ход - с первым входом четвёртого элемента И, второй вход которого подключен к входу сброса узла, первый выход регистра сдвига соединен с вторым входом второго элемента И, второй выход .- с вторыми входами первого и тр атьего элементов И и инверсным выходом пятого элемента И, прямой вход которого соединен с третьим выходом регистра сдвига, четвертый регистр сдвига и выходы первого и второго элементов И образуют первую группу выходов узла, третий выход регистра сдвига и выходы третьего, четвертого и пятого элементов И образуют вторую группу выходов узл синхронизации обмена.

2.Устройство по п. I, отличающееся, тем, что узел захвата магУ1атрали содержит два триггера и элемент И, причем выход первого триггера соединен с инверсным входом элемента И и входом сброса второго триггера, синхровход которого является входом пуска узла, а выход подключен к информационному нхОду первого тр: ггера, вход сброса и сишсровход которого соединены соответственно с управляющим входом узла и прямым входом элемента И, выходы первого и второго триггеров

и выход и прямой вход элемента И образуют информационный вход-выход узла.

3.Устройство по п, 1, о т л и чающееся тем, что распределитель сигналов управления циклом содержит счетчик, дешифратор и триггер, причем тактовый вход счетчика

и первая группа входов дешифратора образуют группу входов распределителя, группа выходов счетчика соединен с второй группой входов дешифратора, первый и второй выходы которого соединены соответственно с установочным входом и входом сброса триггера, а группа выходов образует второй, тре тий и шестой выходы распределителя, второй выход дешифратора и выход триггера являются соответственно первым и пятым выходами распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

1. МУЛЬТИПЛЕКСНОЕ УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ, содержащее узел прерывания, узел захвата магистрали и регистр управляющего слова, информационные входы - выходы которых образуют управляющий входвыход устройства, узел формирования адреса, выход которого является первьш адресным выходом устройства, регистр информации, первый и второй информационные входы-выходы которого являются соответственно первым и вторым информационными входами - выходами устройства, и распределитель сигналов управления циклом, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющим входам узла захвата магистрали, узла формирования адреса, регистра управляющего слова и регистра информащи, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены узел генераций адресов, узел синхронизации обмена и коммутатор констант, причем информационный вход и вход сброса узла синхронизации обмена соединены соответственно с информационными входами-выходами узла захвата магистрали и узла прерывания,, первая группа вьпсодов является группой выходов синхронизации устройства, а вход задания направления обмена подключен к пятому выходу распределителя сигналов управления циклом, группа входов которого .соединена с второй группой выходов узла синхронизации обмена , с управляющим выходом регистра управляющего слова и первым управляющим выходом узла генерации адресов, второй управляющий выход которого соединен с входом пуска узла захвата магистрали, вход синхронизации является входом синхронизации устройства, а информационный выход соединен с вторым адресным выходом устройства и информационным входом коммутатора констант, первый и второй управляю(Л щие входы которого подключены соотс: ветственно к шестому выходу распределителя сигналов управления циклом и синхронизирующим выходом узла прерывания, вход синхронизации которого соединен с информационнь м входом регистра управляющего слова и выходом ел узла формирования адреса, информаци онный вход которого является адресным входом устройства, выход коммуел татора констант соединен с управляю4 щим входом-выходом устройства, прио: чем узел генерации адресов.содержит задающий генератор, злемент Ни злемент ИЛИ, причем счетный вход счетчика соединен с выходом задающего генератора, группа выходов образует информационный выход узла, выходы первого и последнего разряде счетчика Соединены соответственно с первым и BTopbw входами элемента И, выход которого является первы управляющим выходом узла и соединен с

1

Изобретение относится к вычислительной технике и предназначено для сопряжения магистрали системы обработки данных с магистралью периферийных устройств, например магистралью адаптеров каналов связи.

Цель изобретения - сокращение аппаратурных затрат.

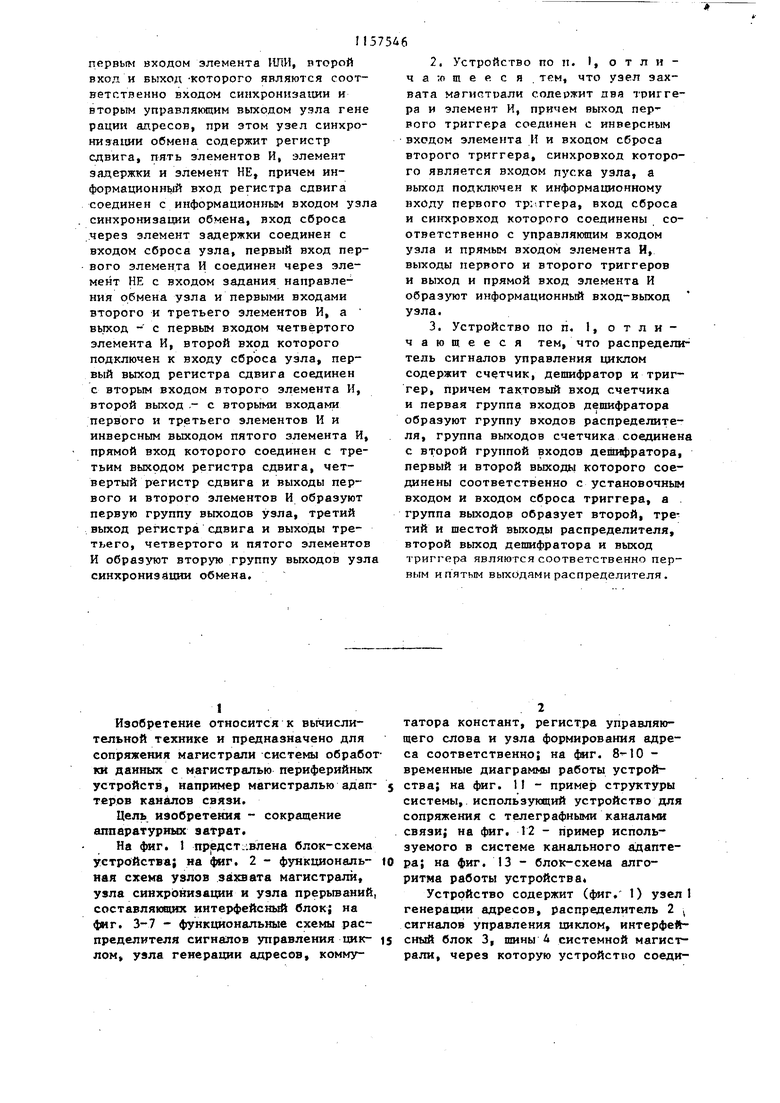

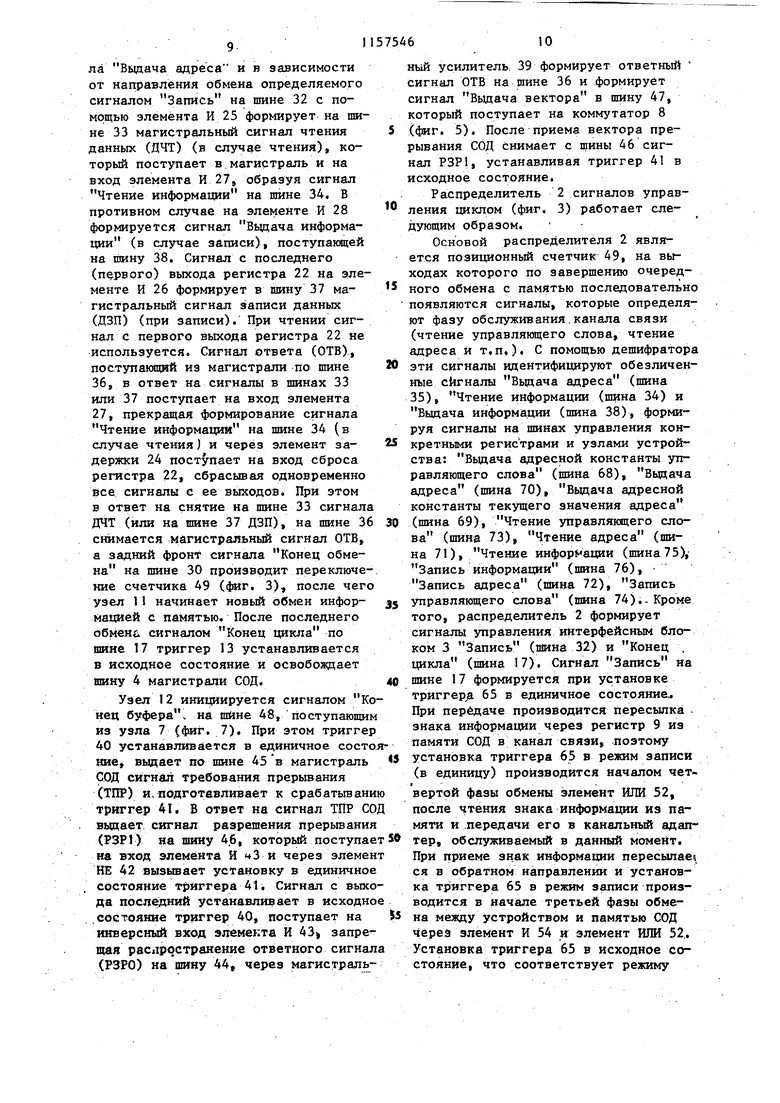

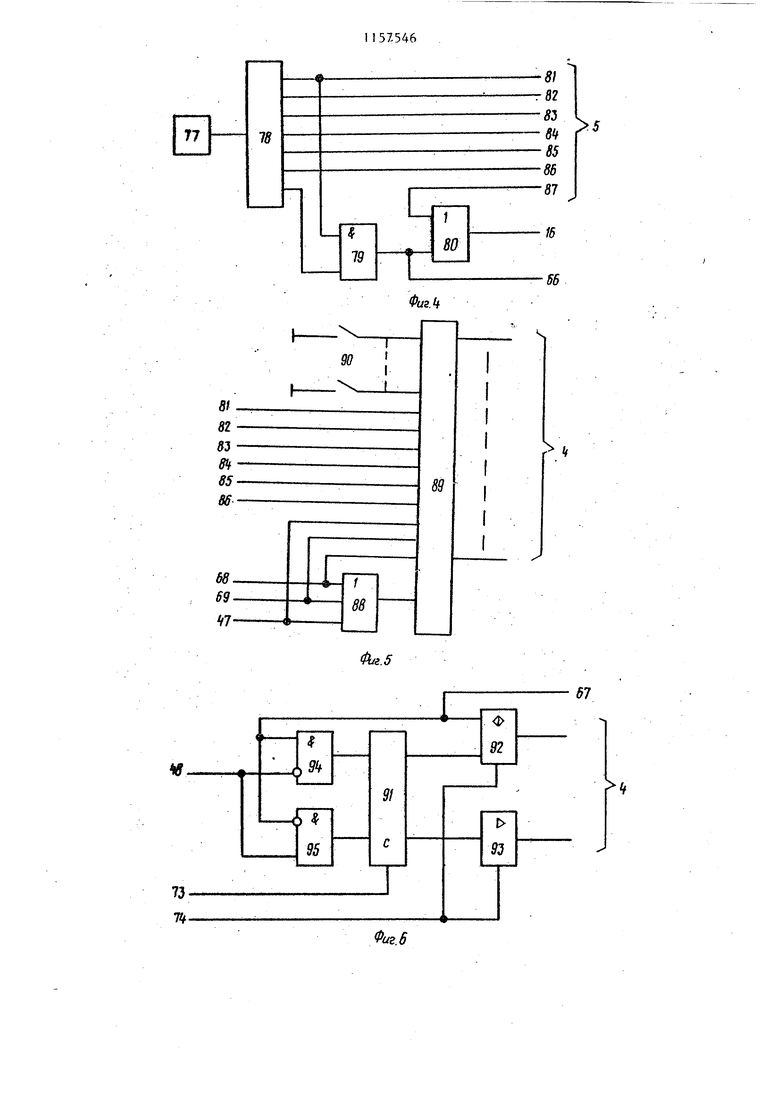

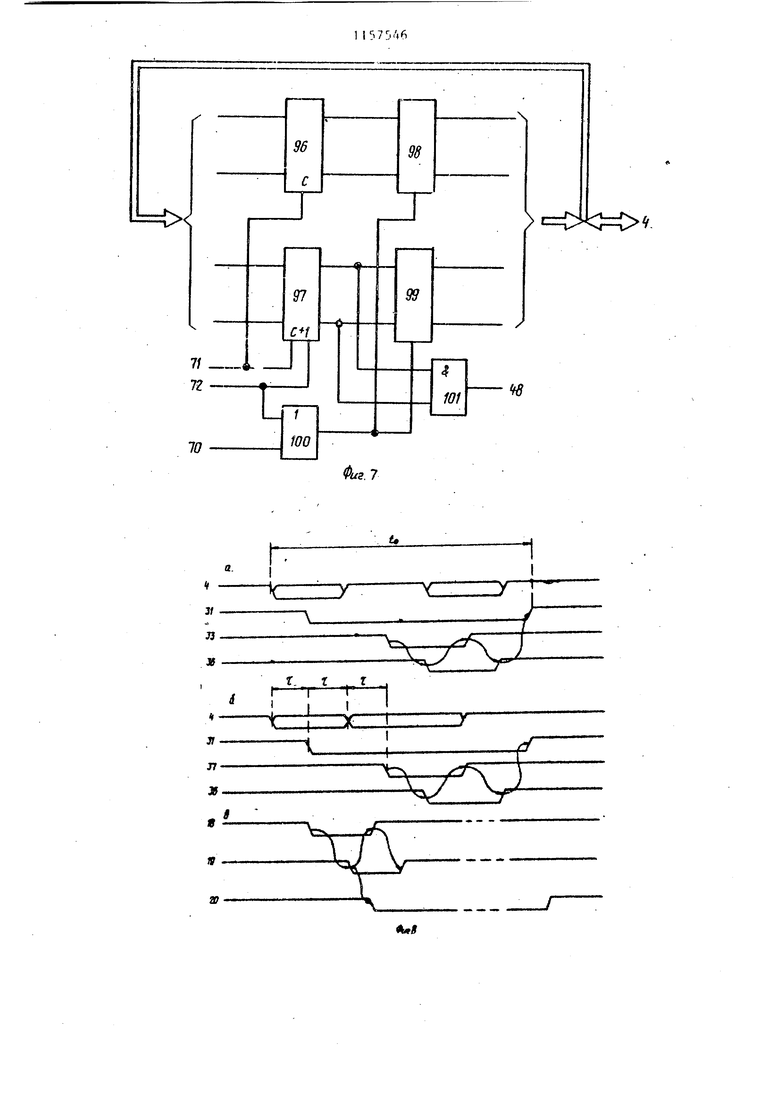

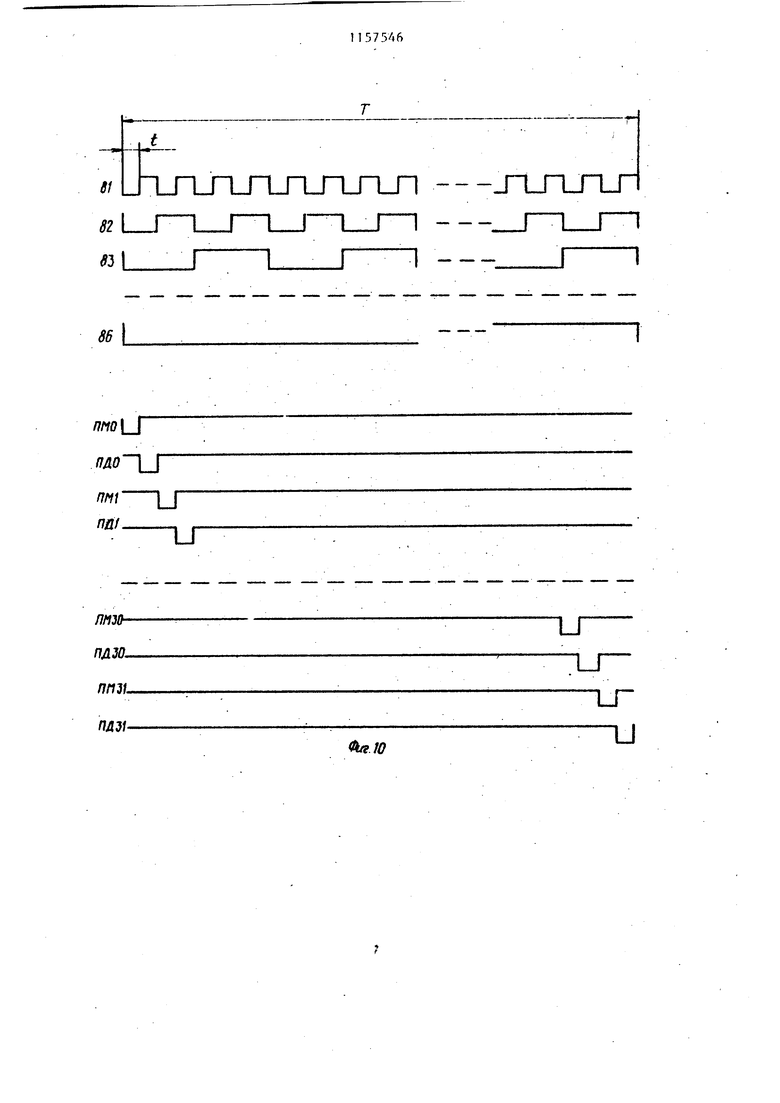

На фиг. 1 предст.1влена блок-схема устройства; на фиг. 2 - фуякциональиая схема узлов захвата магистрали, узла синхройизации и узла прерываний, составляющих интерфейсный блок; на фиг. 3-7 - функциональные схемы распределителя сигналов управления циклом, узла генерации адресов, коммутатора констант, регистра управляющего слова и узла формирования адреса соответственно на фиг. временные диаграммы работы устройства; на фиг. И - пример структуры системы, использующий устройство для сопряжения с телеграфными каналами связи; на фиг. 12 - пример используемого в системе канального адаптера; на фиг. 13 - блок-схема алгоритма работы устройства

Устройство содержит (фиг. 1) узел генерации адресов, распределитель 2 сигналов управления циклом, интерфейсный блок 3, шины Д системной магистрали, через которую устройство соеди3:1

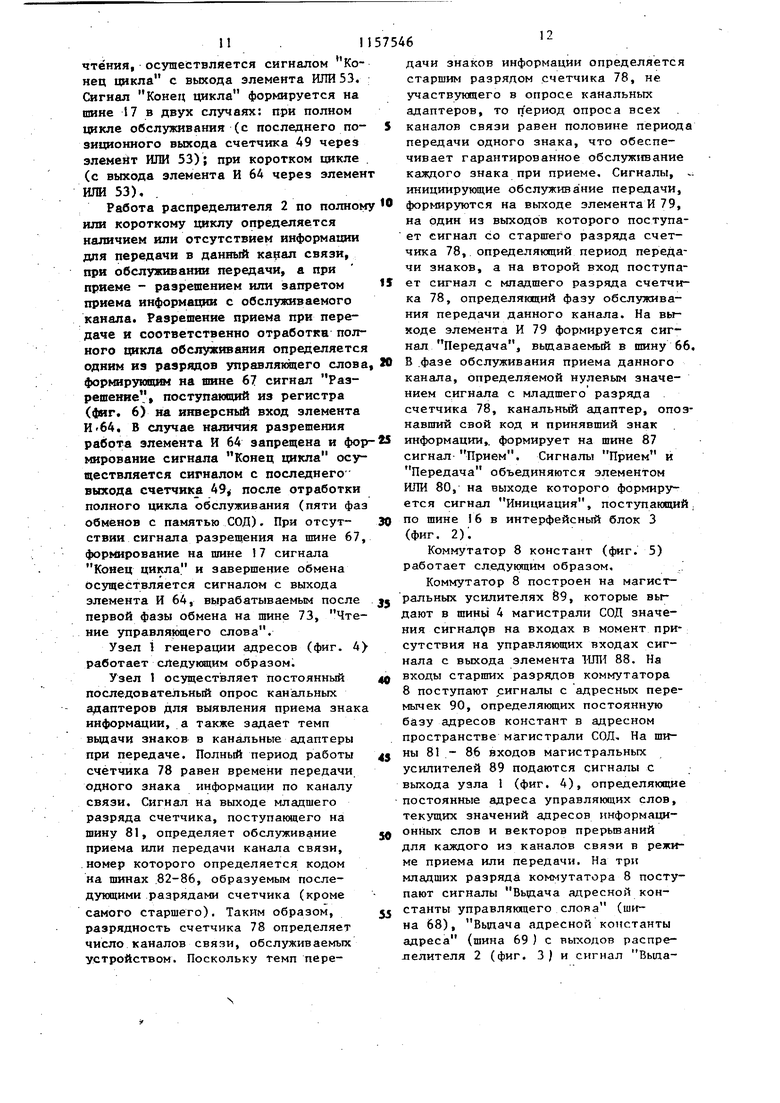

няется с управляющей ЭВМ (не показана) и шины 5 магистрали периферийных устройств, к которой подключены периферийные устройства, например, адаптеры телеграфных каналов связи, регистр 6 управляющего слова, узел 7 формирования адреса, коммутатор 8 констант, регистр 9 информации. Интерфейсный блок 3 состоит из узла 10 захвата магистрали, узла 11 синхронизации обмена и узла 12 прерываний, I Узел 10 захвата магистрали (г. 2) содержит триггеры 13 и 14, элемент И 15, шину 16 входа пуска, шину 17 управлякяцего входа и шины 1.8 - 21 информационного входа-выхода узла ip. Узел 11 синхронизации обмена (фяг. 2) содержит регистр 22 сдвига, элемент НЕ 23, элемент 24 задержки, первый 25, второй 26, четвертый 27, третий 28 и пятый 29 элементы И, шины 30 и 31 третьего и четвертого выходов регистра 22, шину 32 входа задания направления обмена узла 11, шины 3335 выходов элементов И 25, 27 и 29, шину 36 входа сброса узла 11, шины 37 и 38 выходов элементов И 26 и 28. Ш1ЯЫ 31, 33 и 37 образуют первую группу выходов, а шины 30, 34, 35 и 38 - вторую группу выходов узла 11. Узел 12 прерываний (фиг. 2) содержит магистральный усилитель 39, триггеры 40 и 41, элемент НЕ 42, элемент И 43, шины 44 - 46 информационного входа-выхода и шины 47 и 48 выхода и входа синхронизации узла 11.

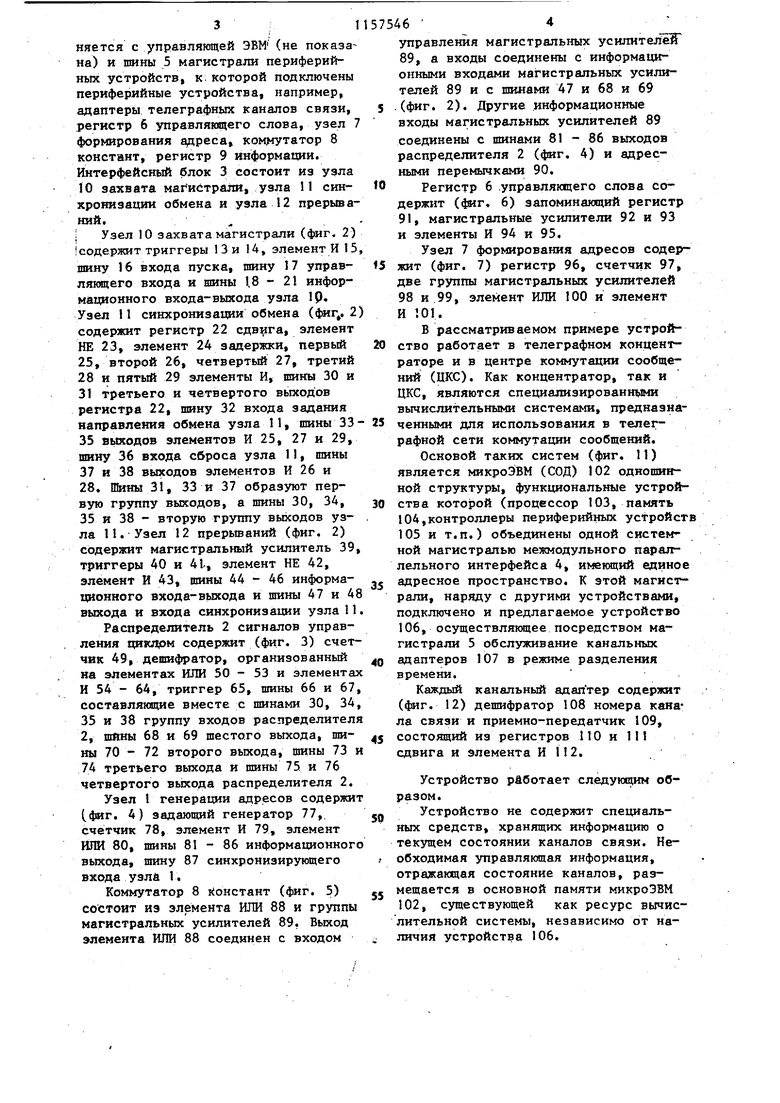

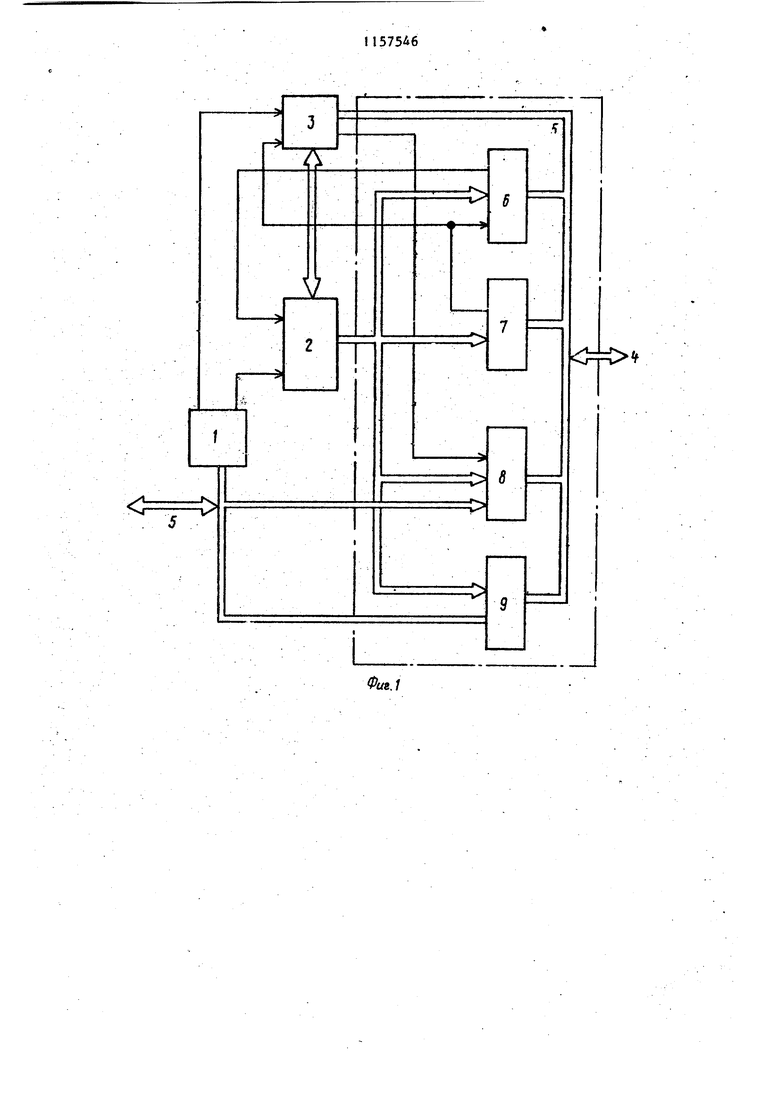

Распределитель 2 сигналов управления 1ЩКЛРМ содержит (фиг. 3) счетчик 49, девшфратор, организованный на элементах ИЛИ 50 - 53 и элементах И 54 - 64, триггер 65, шины 66 и 67, составляющие вместе с шинами 30, 34, 35 и 38 группу входов распределителя 2, шины 68 и 69 шестого выхода, шины 70 - 72 второго выхода, шины 73 и 74 третьего выхода и шины 75 и 76 четвертого выхода распределителя 2.

Узел 1 генерации адресов содержит (фиг. 4) задающий генератор 77, счетчик 78, элемент И 79, элемент ИЛИ 80, шины 81-86 информационного выхода, шину 87 синхронизирующего входа узлд 1.

Коммутатор 8 Констант (фиг. 5) состоит из элемента ИЛИ 88 и группы магистральных усилителей 89. Выход элемеита ИЛИ 88 соединен с входом

57546 4J

управления магистральных усилителе 89, а входы соединены с информационными входами магистральных усилителей 89 и с шинами 47 и 68 и 69 5 .(фиг. 2). Другие информационные входы магистральных усилителей 89 соединены с шинами 81-86 выходов распределителя 2 (фиг. 4) и адресными перемычками 90.

О Регистр 6 .управляющего слова содержит (фиг, 6) запоминающий регистр 91, магистральные усилители 92 и 93 и элементы И 94 и 95.

Узел 7 формирования адресов содер 5 жит (фиг. 7) регистр 96, счетчик 97, две группы магистральных усилителей 98 и 99, элемент ИЛИ 100 и элемент И 101.

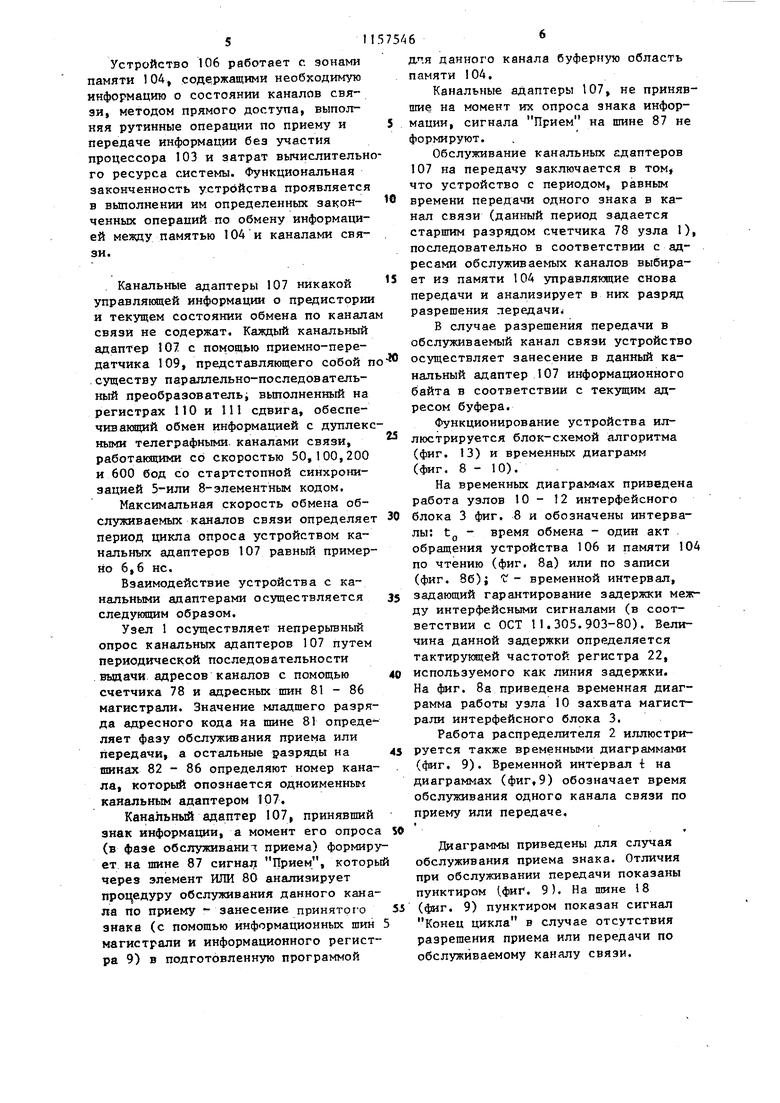

В рассматриваемом примере устройство работает в телеграфном концентраторе и в центре коммутации сообщений (ЦКС). Как концентратор, так и ЦКС, являются специализированными вычислительными системами, предназначенными для использования в телеграфной сети коммутации сообщений. Основой таких систем (фиг. 11) является микроэвм (СОД) 102 одношинной структуры, функциональные устройства которой (процессор 103, память 104,контроллеры периферийных устройств 105 и т.п.) объединены одной системной магистралью межмодульного параллельного интерфейса 4, имеющий единое

5 адресное пространство. К этой магистрали, наряду с другими устройствами, подключено и предлагаемое устройство 106, осуществляющее посредством магистрали 5 обслуживание канальных

0 адаптеров 107 в режиме разделения времени.

Каждый канальный адаптер содержит (фиг. 12) дешифратор 108 номера канала связи и приемно-передатчик 109,

5 состоящий из регистров ПО и III сдвига и элемента И 112.

Устройство работает следующим образом.

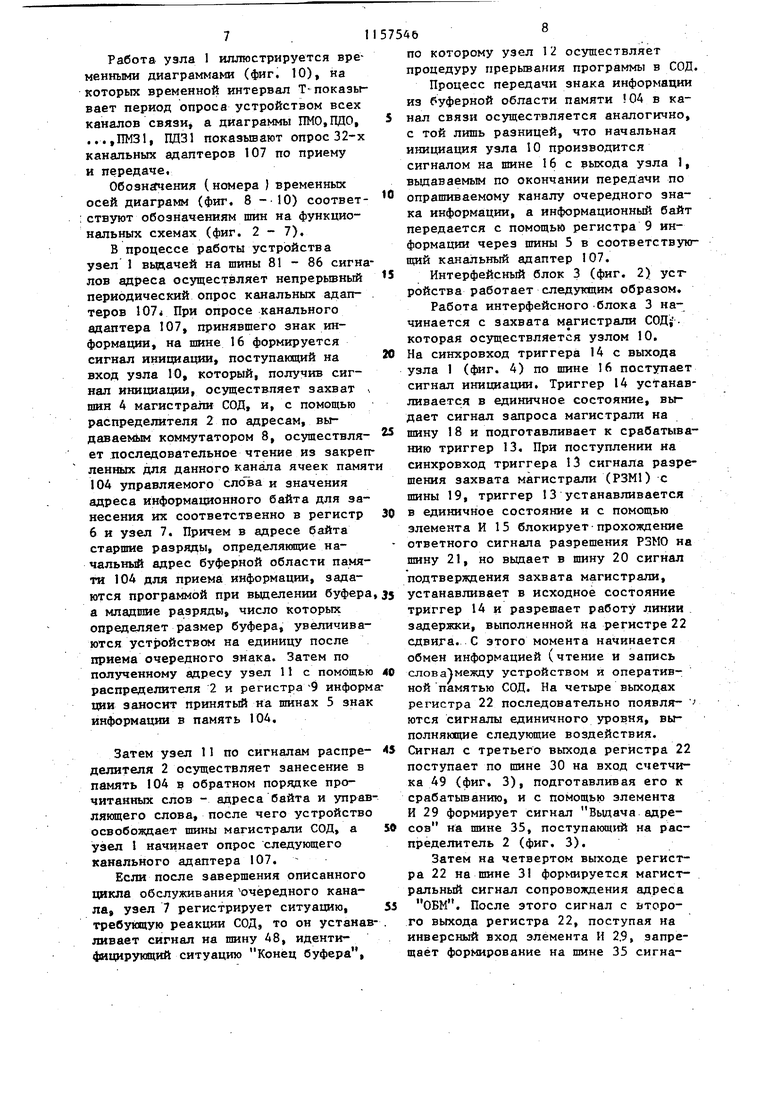

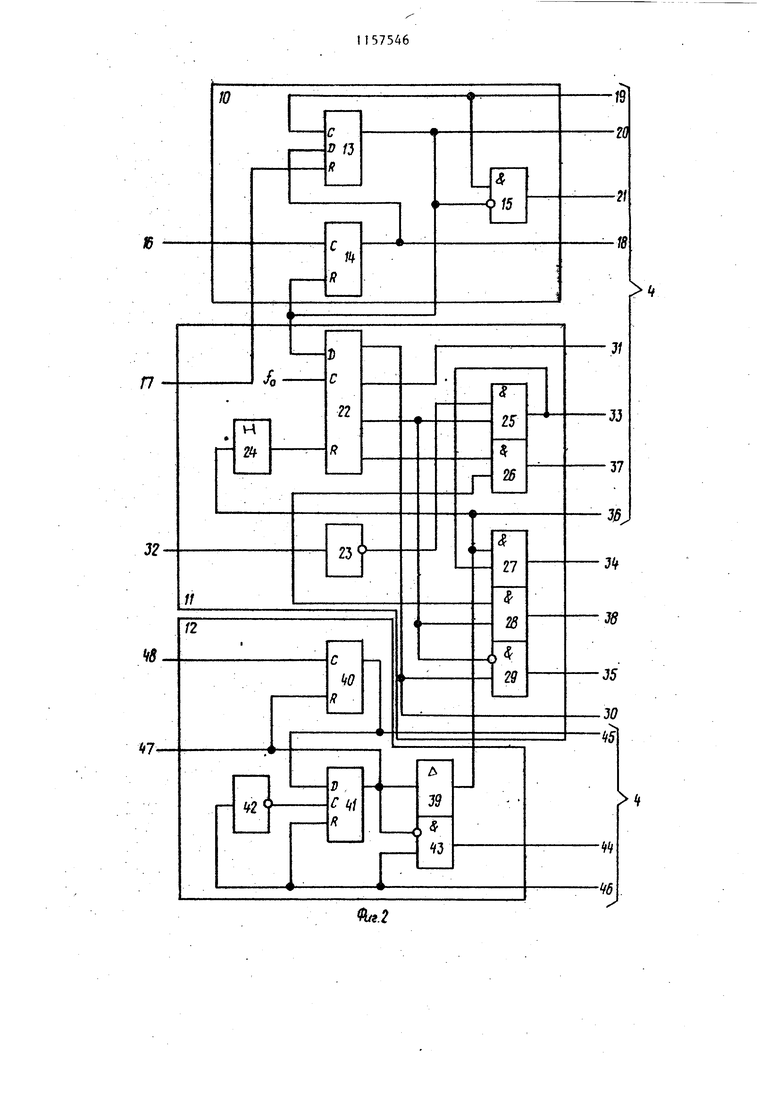

Устройство не содержит специальных средств, хранящих информацию о текзпдем состоянии каналов связи. Необходимая управляющая информация, отражающая состояние каналов, размещается в основной памяти микроЭВМ 102, существующей как ресурс вычислительной системы, независимо от наличия устройства 106. Устройство 106 работает с зонами памяти 104, содержащими необходимую информацию о состоянии каналов свяэи, методом прямого доступа, выполняя рутинные операции по приему и передаче информации без участия процессора 103 и затрат вычислительн го ресурса системы. Функциональная законченность устройства проявляется в выполнении им определенных законченных операпий по обмену информацией между памятью 104 и каналами связи. Канальные адаптеры 107 никакой управляющей информации о предистории и текущем состоянии обмена по канала связи не содержат. Каждый канальный адаптер 107 с помощью приемно-передатчика 109, представляющего собой п .существу параллельно-последовательный преобразователь вьтолненный на регистрах ПО и 111 сдвига, обеспечивающий обмен информацией с дуплек ными телеграфными, каналами связи, работающими со скоростью 50,100,200 и 600 бод со стартстопной синхронизацией 5-или 8-элементным кодом. Максимальная скорость обмена обслуживаемых каналов связи определяе период цикла опроса устройством канальных адаптеров 107 равный примерно 6,6 НС. Взаимодействие устройства с канальными адаптерами осуществляется следующим образом. Узел 1 осуществляет непрерьгоный опрос канальных адаптеров 107 путем периодической последовательности вьдачи адресов каналов с помощью счетчика 78 и адресных шин 81-86 магистрали. Значение младшего разря да адресного кода на шине 81 опреде ляет фазу обслуживания приема или передачи, а остальные разряды на шинах 82 - 86 определяют номер кана ла, который опознается одноименным канальным адаптером 107, Канальный адаптер 107, принявший знак информации, а момент его опрос (в фаде обслуживание приема) формир ет на шине 87 сигнал Прием, котор через элемент ИЛИ 80 анализирует прО1 едуру обслуживания данного кана ла по приему - занесение принятого знака (с помощью информационных шин магистрали и информационного регист ра 9) в подготовленную программой 1 д.я данного канала буферную область памяти 104. Канальные адаптеры 107, не принявшие на момент их опроса знака информации, сигнала Прием на шине 87 не формируют. Обслуживание канальных адаптеров 107 на передачу заключается в том что устройство с периодом, равным времени передачи одного знака в канал связи (данный период задается старшим разрядом счетчика 78 узла I), последовательно в соответствии с адресами обслуживаемых каналов выбирает из памяти 104 управляющие снова передачи и анализирует в них разряд разрешения передачи В случае разрешения передачи в обслуживаемый канал связи устройство осуществляет занесение в данный канальный адаптер 107 информационного байта в соответствии с текущим адресом буфера. Функционирование устройства иллюстрируется блок-схемой алгоритма (фиг. 13) и временных диаграмм (фиг. 8-10). На временных диаграммах приведена работа узлов 10 - 12 интерфейсного блока 3 фиг. 8 и обозначены интервалы: tg - время обмена - один акт обращения устройства 106 и памяти 104 по чтению (фиг. 8а) или по записи (фиг. 8б); f - временной интервал, задающий гарантирование задержки между интерфейсными сигналами (в соответствии с ОСТ 11.305.903-80). Величина данной задержки определяется тактируклцей частотой регистра 22, используемого как линия задержки. На фиг. 8а приведена временная диаграмма работы узла 10 захвата магистрали интерфейсного блока 3. Работа распределителя 2 иллюстрируется также временными диаграммами (фиг. 9). Временной интервал i на диаграммах (фиг,9) обозначает время обслуживания одного канала связи по приему или передаче. Диаграммы приведены для случая обслуживания приема знака. Отличия при обслуживании передачи показаны пунктиром (фиг. 9). На шине 18 (фиг. 9) пунктиром показан сигнал Конец цикла в случае отсутствия разрешения приема или передачи по обслуживаемому каналу связи. Работа уэла 1 иллюстрируется временными диаграммами (фиг. 10), на которых временной интервал Т показы вает период опроса устройством всех каналов связи а диаграммы ПМО,ПДО, ... ,11М31, ПД31 показьюают опрос 32-х канальных адаптеров 107 по приему и передаче. Обозначения (номера ) временных осей диаграмм (фиг. 8 --10) соответ ;ствуют обозначениям шин на функциональных схемах (фиг. 2-7). В процессе работы устройств а узел 1 вьдачей на шины 81-86 сигн лов адреса осуществляет непрерывный периодический опрос канальных адаптеров 107i При опросе канального адаптера 107, принявшего знак информации, на шине 16 формируется сигнал инициации, поступающий на вход узла 10, который, получив сигнал инициации, осуществляет захват шин 4 магистрали СОД, и, с помощью распределителя 2 по адресам, выдаваемым коммутатором 8, осуществляет последовательное чтение из закреп ленных для данного канала ячеек памя 104 управляемого слова и значения адреса информационного байта для занесения их соответственно в регистр 6 и узел 7. Причем в адресе байта старшие разряды, определяющие начальный адрес буферной области памяти 104 для лриема информации, задаются программой при выделении буфера а младшие ра.зряды, число которых определяет размер буфера, увеличиваются устройством на единицу после приема очередного знака. Затем по полученному адресу узел 11 с помощью распределителя 2 и регистра 9 информ ции заиосит принятый на шинах 5 знак информации в память 104. Затем узел 11 по сигналам распределителя 2 осуществляет занесение в память 104 в обратном порядке прочитанных слов - адреса байта и управ ляющего слова, после чего устройство освобождает шины магистрали СОД, а узел 1 начинает опрос следующего канального адаптера 107. Если после завершения описанного цикла обслуживания очередного канала, узел 7 регистрирует ситуацию, требующую реакции СОД, то он устанав ливает сигнал на шину 48, идентифицирующий ситуацию Конец буфера. 46 по которому узел 12 осуществляет процедуру прерьшания программы в СОД. Процесс передачи знака информации из буферной области памяти 04 в канал связи осуществляется аналогично, с той лишь разницей, что начальная инициация узла 10 производится сигналом на шине 16 с выхода узла 1, выдаваемым по окончании передачи по опрашиваемому каналу очередного знака информации, а информационный байт передается с помощь регистра 9 информации через шины 5 в соответствующий канальный адаптер 107. Интерфейсный блок 3 (фиг. 2) устройства работает следукщим образом. Работа интерфейсного блока 3 начинается с захвата магистрали СОД}которая осуществляется узлом 10. На синхровход триггера 14 с выхода узла 1 (фиг. 4) по шине 16 поступает сигнал инициации. Триггер 14 устанавливается в единичное состояние, выдает сигнал запроса магистрали на шину 18 и подготавливает к срабатыванию триггер 13. При поступлении на синхровход триггера 13 сигнала разрешения захвата магистрали (РЗМ1) с шины 19, триггер 13 устанавливается в единичное состояние и с помощью злемента И 15 блокирует прохождение ответного сигнала разрешения РЗМО на щину 21, но вьщает в щину 20 сигнал подтверждения захвата магистрали, устанавливает в исходное состояние триггер 14 и разрешает работу линии задержки, выполненной на регистре 22 сдвига. С этого момента начинается обмен информацией (чтение и запись слова межцу устройством и оперативной памятью СОД. На четыре выходах регистра 22 последовательно появля- ются сигналы единичного уровня, выполняющие следующие воздействия. Сигнал с третьего выхода регистра 22 поступает по шине 30 на вход счетчика 49 (фиг, 3), подготавливая его к срабатьшанию, и с помощью злемента И 29 формирует сигнал Выдача адресов на шине 35, поступающий на распределитель 2 (фиг. 3). Затем на четвертом выходе регистра 22 на шине 31 фop шpyeтcя магистральный сигнал сопровождения адреса ОБМ. После этого сигнал с второго выхода регистра 22, поступая на нверсный вход элемента И 2.9, запреает формирование на шине 35 сигнала Выдача адреса и в зависимости от направления обмена определяемого сигналом Запись на шине 32 с помощью элемента И 25 формирует на шине 33 магистральный сигнал чтения данных (ДЧТ) (н случае чтения), который поступает в магистраль и на вход элемента И 27, образуя сигнал Чтение информации на шине 34, В противном случае на элементе И 28 формируется сигнал Вьщача информации (в случае записи), поступакяцей на шину 38. Сигнал с последнего (первого) выхода регистра 22 на элементе И 26 формирует в шину 37 магистральный сигнал записи данных (ДЗП) (при записи). При чтении сигнал с первого выхода регистра 22 не используется. Сигнал ответа (ОТВ), поступающий из магистрали по шине 36, в ответ на сигналы в шинах 33 или 37 поступает на вход элемента 27, прекращая формирование сигнала Чтение информации на шине 34 (в случае чтения) и через элемент задержки 24 поступает на вход сброса регистра 22, сбрасывая одновременно все сигналы с ее выходов. При этом в ответ на снятие на шине 33 сигнала ДЧТ (или на шине 37 ДЗП), на шине 36 снимается мйгистральный сигнал ОТВ, а задний фронт сигнала Конец обмена на шине 30 производит переключение счетчика 49 (фиг, 3), после чего узел 1J начинает новый обмен информацией с памятью. После последнего обмень сигналом Конец цикла по шине 17 триггер 13 устанавливается в исходное состояние и освобождает шину 4 магистрали СОД. Узел 12 инихщируется сигналом Ко нец буфера, на Шине 48, поступающи из узла 7 (фиг, 7), При этом триггер 40 устанавливается в единичное состо ние, вьздает по шине 45в магистраль СОД сигнал требования прерывания СТЕИ) и, подготавливает к срабатьшани триггер 41, В стает на сигнал ТИР СО выдает сигнал разрешения прерывани (P3PJ) на шину 4,6, который поступа на вход элемента И чЗ и через элемен НЕ 42 вызывает установку в единичное состояние триггера 41. Сигнал с выхо да последний устанавливает в исходно состояние триггер 40, поступает на инверсный вход элемента И 43 запрещая рас11ространение ответного сигнал (РЗРО) на шину 44, через магистрапьный усилитель. 39 формирует ответный сигнал ОТВ на шине 36 и формирует сигнал Вьщача вектора в шину 47, который поступает на коммутатор 8 (фиг. 5), После приема вектора прерывания СОД снимает с шины 46 сигнал РЗР1, устанавливая триггер 4 в исходное состояние. Распределитель 2 сигналов управления циклом (фиг. 3) работает следующим образом. Основой распределителя 2 является позиционный счетчик 49, на выходах которого по завершению очередного обмена с памятью последовательно появляются сигналы, которые определяют фазу обслуживания.канала связи (чтение управляющего слова, чтение адреса и т,п). С помощью дешифратора эти сигналы идентифицируют обезличенные сигналы Выдача адреса (шина 35), Чтение информации (шина 34) и Выдача информа.ции (шина 38), формируя сигналы на шинах управления конкретными регистрами и узлами устройства: Выдача адресной константы управляющего слова (шина 68), Выдача адреса (шина 70), Вьщача адресной константы текущего значения адреса (шина 69), Чтение управляющего слова (шина 73), Чтение адреса (шина 71), Чтение информации (шина 75), Запись информации (шина 76), Запись адреса (шина 72), Запись управляющего слова (шина 74),. Кроме того, распределитель 2 формирует сигналы управления интерфейсным блоком 3 Запись (шина 32) и Конец цикла (шина 17). Сигнал Запись на шине 17 формируется при установке триггеру 65 в единичное состояние.. При передаче производится пересылка знака информации через регистр 9 из памяти СОД в канал связи, поэтому установка триггера 65 в режим записи (в единицу) производится началом четвертой фазы обмены элемент ИЛИ 52, после чтения знака информации из памяти и передачи его в канальный адаптер, обслуживаемый в данный момент, Прй приеме знак информации пересылаем ся в обратном направлении и установка триггера 65 в режим записи производится в начале третьей фазы обмена между устройством и памятью СОД через элемент И 54 и элемент ИЛИ 52., Установка триггера 65 в исходное состояние, что соответствует режиму чтения, осуществляется сигналом нец цикла с выхода элемента ИЛИ 53, Сигнал Конец цикла формируется на шине 17 в двух случаях: при полном цикле обслуживания (с последнего позиционного выхода счетчика 49 через элемейт ИЛИ 53); при коротком цикле (с выхода элемента И 64 через элемен ИЛИ 53), . Работа распределителя 2 по полном или короткому циклу определяется наличием или отсутствием информации для передачи в данный связи, при обслуживании передачи, а при приеме - разрешением или запретом приема информации с обслуживаемого канала. Разрешение приема при передаче и соответственно отработки полного цикла обслуживания определяется одним иэ разрядов управляющего слов формирующим иа втне 67 сигнал Разрешеияе поступакнций из регистра (фиг. 6) иа инверсный вход элемента И64. В случае наличия разрешения работа элемента И 64 запрещена и фор мирование сигнала Конец цикла осуществляется сигналом с последнего выхода счетчика 49 после отработки полного цикла обслуживания (пяти фаз обменов с памятью СОД). При отсутствии сигнала разрещения на шине 67 формирование на шине 17 сигнала Конец цикла и завершение обмена Осуществляется сигналом с выхода элемента И 64, вырабатываемым после первой фазы обмена на шине 73, Чтение управляющего слова . Узел 1 генерации адресов (фиг. 4 работает сЛедукяцим образом. Узел 1 осуществляет постоянный последовательный опрос канальных адаптеров для выявления приема знака информации, а также задает темп вьщачи знаков в канальные адаптеры при передаче. Полный период работы счётчика 78 равен времени передачи одного знака информации по каналу связи. Сигнал на выходе младшего разряда счетчика, поступающего на шину 81, определяет обслуживание приема или передачи канала связи, номер которого определяется кодом на шинах .82-86, образуемым последующими разрядами счетчика (кроме самого старшего). Таким образом, разрядность счетчика 78 определяет число каналов связи, обслуживаемых устройством. Поскольку темп передачи знаков информации определяется старшиь) разрядом счетчика 78, не участвующего в опросе канальных адаптеров, то период опроса всех каналов связи равен половине периода передачи одного знака, что обеспечивает гарантированное обслуж1шание каждого знака при приеме. Сигналы, . иннциирующие обслуживание передачи, формируются на выходе элемента И 79, на один нз выходов которого поступает сигнал со старпгего разряда счетчнка 78,. определяющий период передачи знаков, а на второй вход поступает сигнал с младшего разряда счетчика 78, определяющий фазу обслуживания передачи данного канала. На выходе элемента И 79 формируется сигнал Передача, вьщаваемый в щину 66. В .фазе обслуживания приема данного канала, определяемой нулевым значением сигнала с младшего разрада счетчика 78, канальньй адаптер, опознавший свой код и принявший знак информации,, формирует на шине 87 сигнал Прием. Сигналы Прием и Передача объединяются элементом ИЛИ 80, на выходе которого формируется сигнал Инициация, поступающий, по шине 16 в интерфейсный блок 3 (фиг. 2). Коммутатор 8 констант (фиг. 5) работает следующим образом. Коммутатор 8 построен на магистральных усилителях 89, которые выдают в шины 4 магистрали СОД значения сигналов на входах в момент присутствия на управляющих входах сигнала с выхода элемента 1ШИ 88. На входы старших разрядов коммутатора 8 поступают сигналы с адресных перемычек 90, определяющих постоянную базу адресов констант в адресном пространстве магистрали СОД, На шины 81 .- 86 входов магистральных усилителей 89 подаются сигналы с выхода узла 1 (фиг. 4), определяющие постоянные адреса управляющих слов, текущих значений адресов информационНых слов и векторов прерьшаний для каждого из каналов связи в режиме приема или передачи. На три младших разряда коммутатора 8 поступают сигналы Вьдача а/дресной константы управляющего слова ( на 68), Выдача адресной константы адреса (шина 69 ) с выходов распределителя 2 (фиг. 3) н сигнал Выаа131ча вектора прерывания (шина А7, поступающий из узла 12. Данные сигналы модифицируют значение адресных констант обслуживаемого канала, а также поступают на вход элемента ИЛИ 88, осуществляющий стррбирование магистральных усилителей 89. Регистр 6 управляющего слова (фиг. 6) работает сле1,дующим образом. , Регистр 6 содержит два разряда,один иэ которых формирует нашине 67 сигнал разрешения приема или передачи по обслуживаемому каналу связи, доступный по записи к чтению со стороны магист рали СОД, а второй разряд образуется сигналом Конец буфера (шина 48) и доступен со стороны магистрали только по чтению. При окончании передачи или приема очередного блока (буфера) Информации на шине 48 формируется сигнал Конец буфера, который через элемент И 95 заносится в запоминающий регистр 91 и через элемент И 94 обнуляет -разряд разрешения приема или передачи. При программной записи разрешения приема или передачи сигfналом с выхода двунаправленного ма. гистрального усилителя 92 производится установка в единицу разряда разрешения (через элемент И 94) и обнуление разряда Конец буфера через элемент И 95. Занесение и вьщача информации в (из) регистра 6 осуществляется соответственно сигналами Чтение, управляющего слова { шина 73) и запись управляющего слова (шина 74), поступающими из распределителя .2 (фиг. 3). Узел 7 формирования адреса (4иг. 7)дф ствами

работает следующим образом..

так. 6 Узел 7 состоит из двух частей постоянной (базовой и модифицируемой. Основой постоянной части узла 7 является регистр 96, а модифицируемой - двоичный счетчик .97 с параллельным занесением информации. Выдача содержимого регистра 96 в магистраль СОД осуществляется с помощью двух групп магистральных усилителей 98 и 99. Число разрядов модифицируемой части определяет объем блока информации (буфера )| принимаемьШ или передаваемый устройством методом прямого доступа. Занесение текущего значения адреса информационного байта в регистр 96 осуществляется сигналом Чтение адреса, ввдаваемым по шине 71 из распределителя 2 (фиг. 3). Выдача содержимого регистра 96 при чтении или записи байта информации осущеЬтвляется сигналом Вьщача адреса, поступавдим. по шине 70, а при записи в фиксированную ячейку памяти для хранения - с помощью сигна ла Запись адреса, поступающим по шине 72. Одновременно этим же сигналом производится модификация (увеличение на единицу) текущего значения адреса для приема (или передачи) следующего информационного байта, принятого (или передаваемого) по данному каналу связи в (из) очередную ячейку информационного блока (буфера) в память СОД. Таким образом, предлагаемое устройство обеспечивает обмен информацией между ЭВМ и периферийными устройпри меньших аппаратурных затраЮ

Со /3

в

Pf

19 -2Q

-21 -18

/о

Г7

2

32

2L

12

W

i

«7

Л

25

-JJ

Т 2 -37

-.

т JV

27

Т 2

38

Т

J5

гд

.30 -f5

S,

с ifi

w9 R

-ftf

-46

66

-J2

5

52

0 /

53

f7

35

3if38

577J 7/

75 75

72 7V

.J

96 С

97

71 „. 72

1 100

10

1

у

33

X .кf- t Г

99

/

. 101

W

ц:7

ю го

30

JJ

LJ LJ

IJ и Tu LT LT- LJ-

U

и

и

и

и

L J

и

и

и

и

0us.ff JajnjnjnjTjnj-i n - jnjTJTji

т

«у

Afti т

lot

J

КйИЛ/1Ы tSujU

gt f

П

W

I

rfl

J

йот tttya ЛлП

| Патент США № 4156796, | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-23—Публикация

1983-05-16—Подача