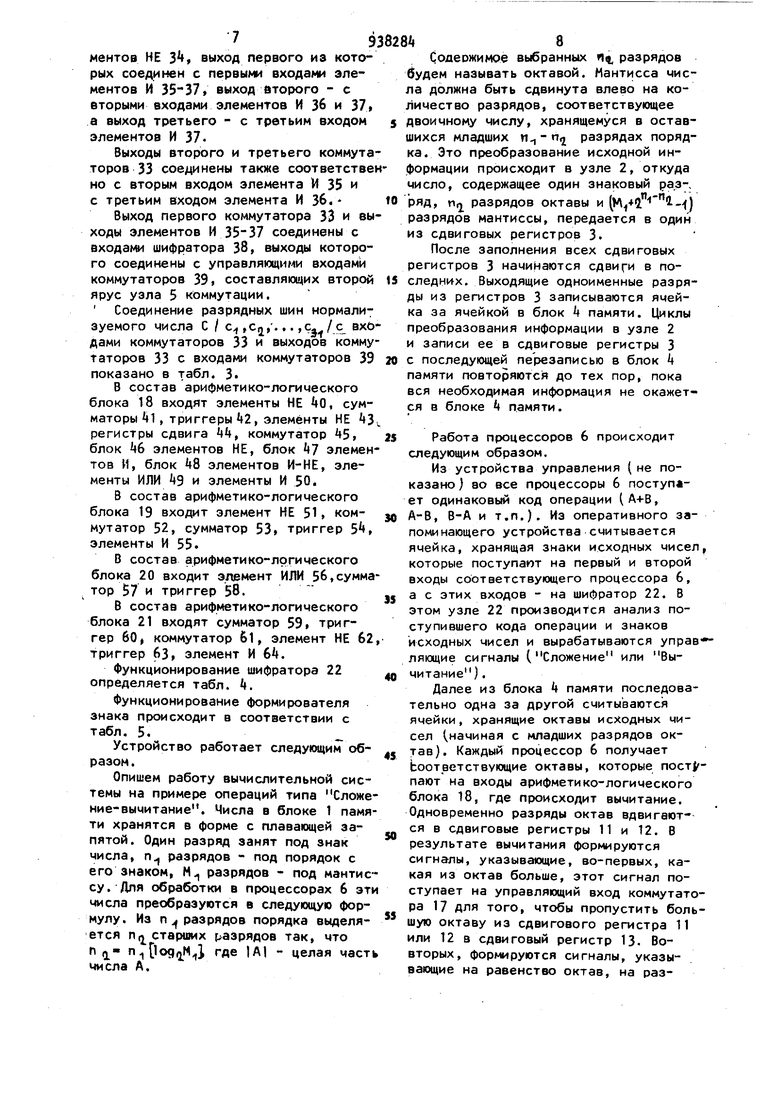

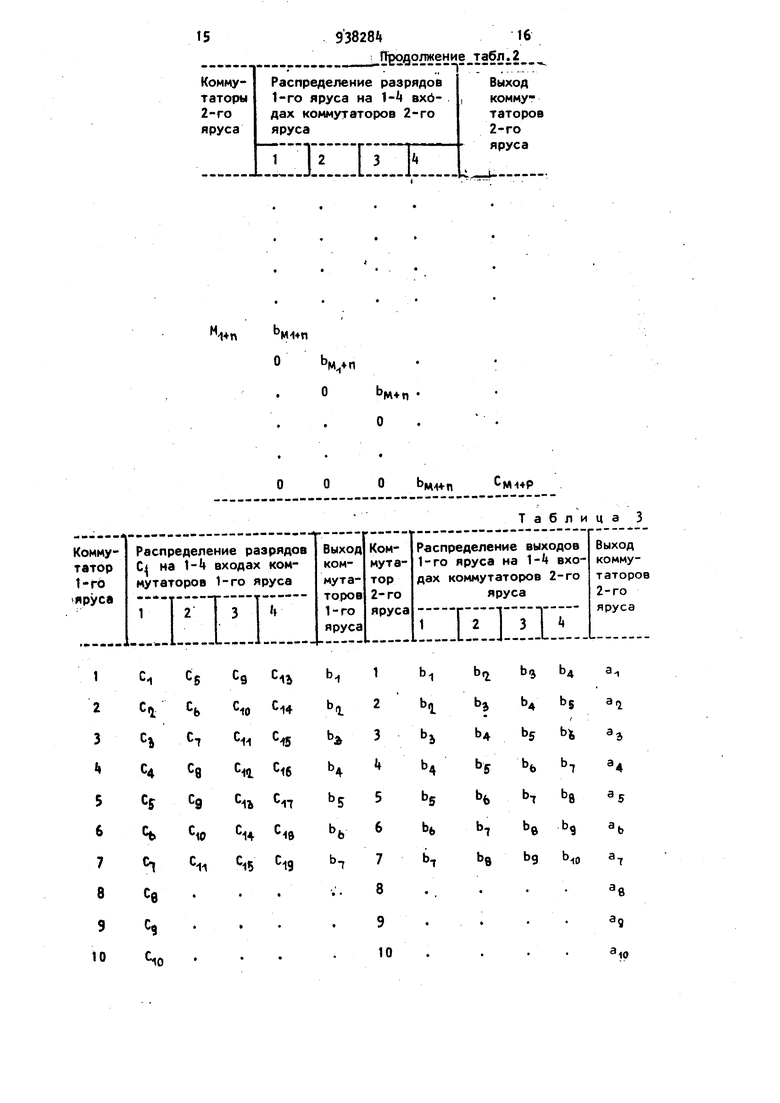

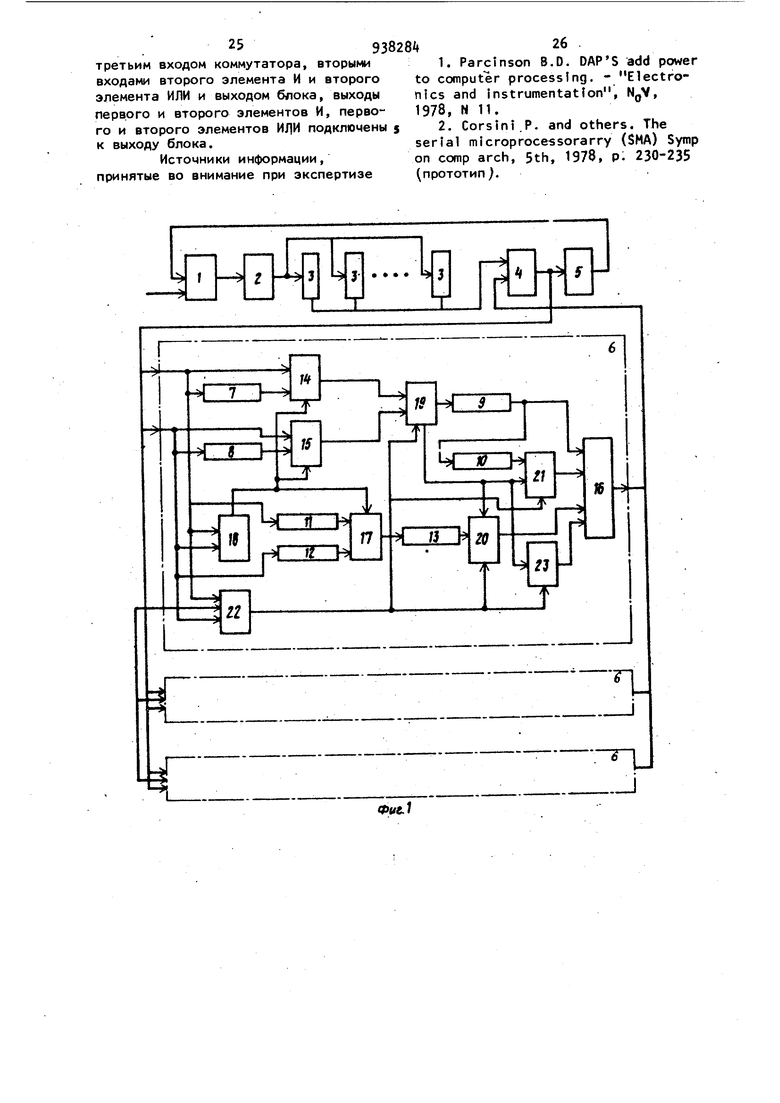

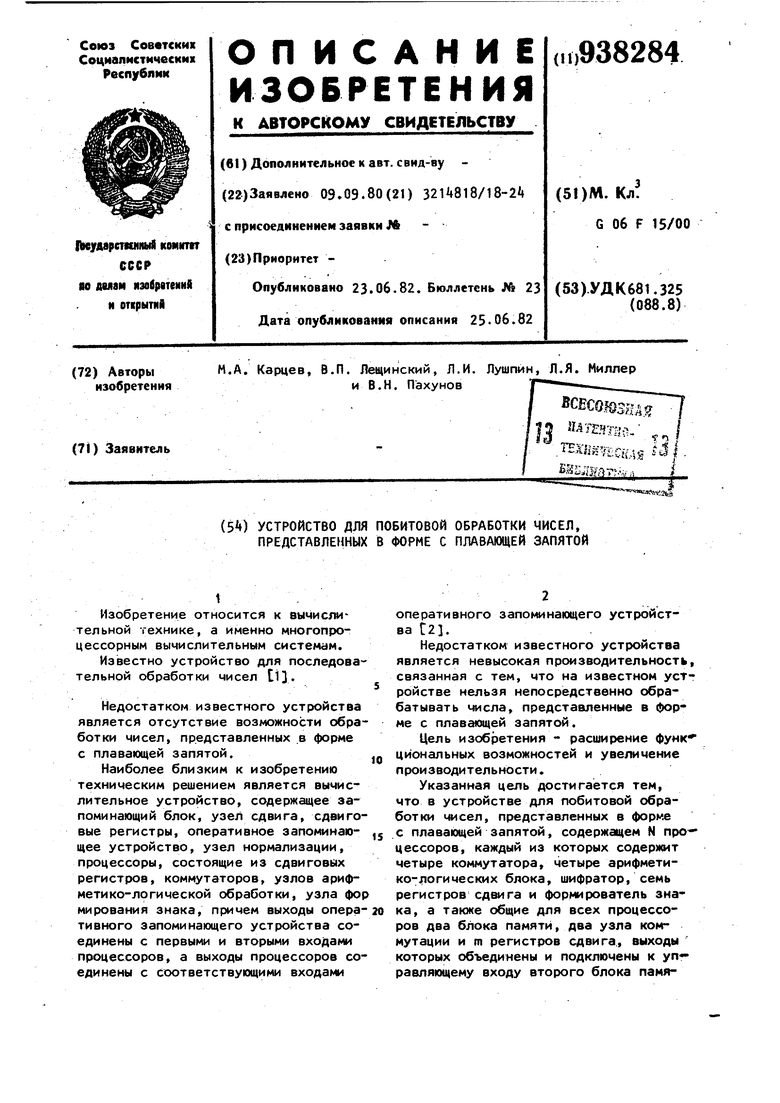

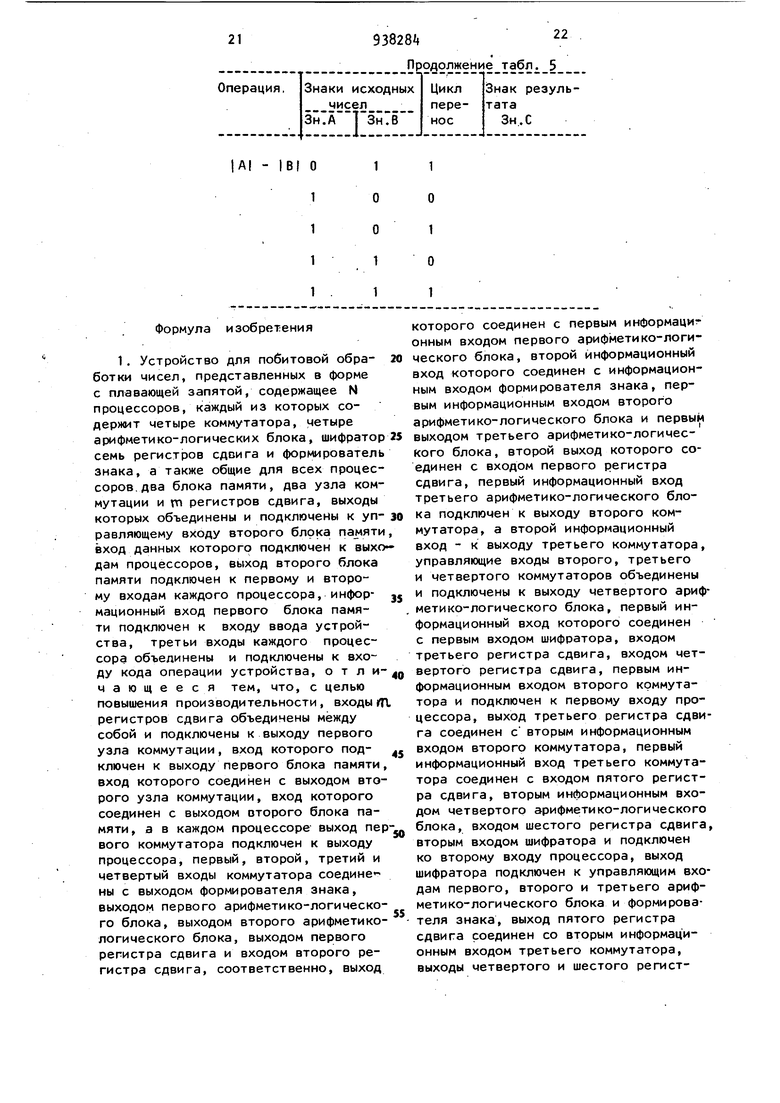

Изобретение относится к вычислительной технике, а именно многопроцессорным вычислительным системам. Известно устройство для последова тельной обработки чисел t1. Недостатком известного устройства является отсутствие возможности обра ботки чисел, представленных .в форме с плавающей запятой. Наиболее близким к изобретению техническим решением является вычислительное устройство, содержащее запоминающий блок, узел сдвига, сдвиго вые регистры, оперативное запоминающее устройство, узел нормализации, процессоры, состоящие из сдвиговых регистров, коммутаторов, узлов арифметико-логической обработки, узла фо мирования знака, причем выходы опера тивного запоминающего устройства соединены с первыми и вторыми входами процессоров, а выходы процессоров со единены с соответствующими входами оперативного запоминающего устройства t2. Недостатком известного устройства является невысокая производительность, связанная с тем, что на известном устройстве нельзя непосредственно обрабатывать числа, представленные в форме с плавающей запятой. Цель изобретения - расширение функ цйональных возможностей и увеличение производительности. Указанная цель достигается тем, что в устройстве для побитовой обработки чисел, представленных в форме с плавающей запятой, содержащем N про-цессоров, каждый из которых содержит четыре коммутатора, четыре арифметикo-Jпoгичecкиx блока, шифратор, семь регистров сдвига и формирователь знака, а также общие для всех процессоров два блока памяти, два узла коммутации и т регистров сдвига, выходы которых объединены и подключены к управляющему входу второго блока памяти, вход данных которого подключен к выходам процессоров, выход второго блока памяти подключен к первому и второму входам каждого процессора, информационный вход первого блока памяти подключен к входу ввода устройства, третьи входы каждого процессора объединены и подключены к вх ду кода операции устройства, входы m регистров Сдвига объединены между собой и подключены к выходу узла ком мутации, вход которого подключен к выходу первого блока памяти, вход ко торого соединен с выходом второго уз ла коммутации, вход которого соедине с выходом второго блока памяти, а в каждом процессоре выход первого коммутатора подключен к выходу процеесора, первый, второй, третий и четвертый входы коммутатора соединены с выходом формирователя знака, выходом первого арифметического блока, выходом второго арифметического блока, выходом первого регистра сдвига и входом второго регистра сдвига соответственно, выход которого соединен с первым информационным входом первого арифметико-логического блока, второй информационный вход которого соединен с информационным входом формирователя знака, первым информационным входом второго арифмети ко-логического блока и первьм выходо третьего арифметико-логического блока, второй выход которого соединен с входом первого регистра сдвига, пе вый информационный вход третьего арифметико-логического блока подключен к выходу второго коммутатора, а второй информационный вход - к выхрду третьего коммутатора, управляющие входы второго, третьего и четвертого коммутаторов объединены и подключены к выходу четвертого арифметико-логического блока, первый информационный вход которого соединен с первым входом шифратора, входом третьего регистра сдвига, входом четвертого регистра сдвига, первым информационным входом второго коммутатора и подключен к первому входу процессора, выхо третьего регистра сдвига соединен с вторым информационным входом второго коммутатора, первый информационный вход третьего коммутатора соединен с входом пятого регистра сдвига, вторы информационным входом четвертого регистра сдвига, вторым входом, шифрато ра и подключен к второму входу процессора, выход шифратора подключен к управляющим входам первого, второго и третьего арифметико-логического блока и формирователя знака, выход пятого регистра сдвига соединен с вторым -: информационным входом третьего коммутатора, выходы четвертого и шестого регистров сдвига соединены с первым и вторым информационными входами четвертого коммутатора соответственно, выход которого соединен с входом седьмого регистра сдвига, выход ко- торого соединен с вторым информацион ным входом второго арифметико-логического блока. Первый арифметико-логический блок содержит элемент И, сумматор, два триггера, элемент НЕ и коммутатор, выход которого соединен с выходом блока,.первый информационный вход коммутатора соединен с входом элeмeнt та НЕ и информационным выходом сумматора, выход переноса которого соединен с входом переноса сумматора, первый информационный вход которого соединен с первым информационным входом блока, второй информационный и управляющий входы блока соединены с первым и вторым входами элемента И соответственно, выход которого соединен с вторым информационным входом сумматора и входом.второго триггера, выход которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом элемента НЕ. Второй арифметико-логический блок содержит элемент ИЛИ, сумматор и триггер, выход которого соединен с входом переноса сумматора, первый информационный вход которого соединен с выходом элемента ИЛИ, первый информационный , второй информационный и управляющий входы блока подключены к первому и второму входам элемента ИЛИ и второму информационному входу сумматора соответственно, выход переноса сумматора соединен с входом триггера, выход суммы сумматора соединен с выходом блока. Третий арифметико-логический блок содержит элемент НЕ, коммутатор, сумматор, триггер, первый и второй элементы И, выходы которых подключены к первому и второму входу блока соответственно, первый информационный вход блока подключен к первому информационному входу коммутатора и входу элемента НЕ, выход которого соединен С вторым информационным входом коммутатора, управляющий вход которого соединен с вторым информационным вхо дом блока и первыми входами первого и второго элементов И соответственно вторые входы которых объединены и подключены к выходу триггера и входу переноса сумматора, выход которого соединен с входом триггера, первый информационный вход сумматора соединен с выходом коммутатора, а второй информационный вход сумматора - с уп равляющим входом блока. Четвертый арифметико-логический блок содержит четыре элемента НЕ, дв .сумматора, два триггера, два регист.ра сдвига, коммутатор, два элемента ИЛИ, два элемента И, блок элементов НЕ, блок элементов И и блок элементов И-НЕ, выход которого соединен с первыми входами первого и второго элементов И, второй вход первого эле мента И соединен с первым входом первого элемента ИЛИ и выходом первого элемента НЕ, выход которого соединен с выходом первого триггера и входом переноса первого сумматора, выход переноса которого соединен с Входом триггера, а информационный выход - с входом первого регистра сдвига, выход которого соединен с ,, первым входом коммутатора, второй вход которого соединен с выходом второго регистра сдвига, вход которого соединен с информационным выходом второго сумматора, выход переноса которого соединен с входом второго триггера, выход которого соединен с входом второго элемента НЕ и входом переноса второго сумматора, первый информационный вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с первым информационным входом блока И, Первым информационным входом первого сумматора, второй информационный вхо которого соединен с выходом четверто го элемента НЕ, вход которого соединен с вторым информационным входом блока и вторым информационным входом второго сумматора, выход коммутатора подключен к входу блока элементов НЕ, выход которого соединен с входом блока элементов И-НЕ и входом блока элементов И, выход которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход второго элемента НЕ соединен с третьим входом коммутатора, вторыми входами второго элемента И и второго элемента ИЛИ и выходом блока, выходы первого и второго элементов И подключены к выходу блока. На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - схема узла 2 коммутации; на фиг. 3 - схема узла 3 коммутации; на фиг. 4 - схема арифметико-логического блока 18; на фиг. 5 - схема арифметико-логического блока 19; на фиг 6 - схема арифметико-логического блока 20; на фиг. 7 - схема арифметико-логического блока 21. Устройство для побитовой обработки чисел, представленных в форме с плавающей запятой, содержит блок 1 памяти, узел 2 коммутации, предназначенный для управления сдвигом, сдвиговые регистры 3 блок памяти, узел 5 коммутации, предназначенный для нормализации, и процессоры 6, каждый из которых состоит из сдвиговых регистров 7-13, коммутаторов арифметико-логических блоков 18-21, шифратора 22, формирователя знака 23Узел 2 коммутации содержит коммутаторы 2Ц, образующие первый ярус, и коммутаторы 25, образующие второй ярус. Соединение разрядных шин сдвигаемого чилаА(а апаа. .,) с входами коммутаторов 2k и выходов коммутаторов 2 с входами коммутаторов 25 показано в табл. 1 и 2. Узел коммутации 5 содержит элементы НЕ 26, входы которых соединены с двенадцатью старшими разрядами нормализуемого числа, а выходы элементов НЕ 26 соединены с входами элементов И 27, выходы которых соединены с входами элементов НЕ 28. Выход первого элемента И 27, кроме того, соединен с первыми входами элементов И 29-31- Выход второго элемента И 27 соединен также с вторыми входами элементов И 30 и 31, а выход третьего элемента И 27 соединен также с третьим входом элемента И 31 Выходы второго и третьего элементов НЕ 28 соединены с вторым и третьим входами соответственно элементов И 29 и 30. Выходы первого элемента НЕ 28 и выходы элементов И 29-31 соединены с входами шифратора 32, выходы которого соединены с управляющими входами коммутаторов 33, составляющих первый ярус узла 5 коммутации. Выходы первых трех коммутаторов 33 первого яруса соединены с входами элеч93ментов НЕ З, выход первого из которых соединен с первыми входами элементов И , выход второго - с вторыми входами элементов И Зб и 37 а выход третьего - с третьим входом элементов И 37. Выходы второго и третьего коммутаторов 33 соединены также соответствен но с вторым входом элемента И 35 и с третьим входом элемента И 36,Выход первого коммутатора 33 и выходы элементов И соединены с входам шифратора 33, выходы которого соединены с управляющими входами коммутаторов 39, составляющих второй ярус узла 5 коммутации. Соединение разрядных шин нормализуемого числа С / с ,с,,... ,с- / с входами коммутаторов 33 и выходов коммутаторов 33 с входами коммутаторов 39 показано в табл. 3« В состав арифметико-логического блока 18 входят элементы НЕ 40, сумматоры «I , триггеры , элементы НЕ 43 регистры сдвига kk, коммутатор , блок А6 элементов НЕ, блок «7 элемен тов И, блок элементов И-НЕ, элементы ИЛИ k3 и элементы И 50. В состав арифметико-логического блока 19 входит элемент НЕ 51, коммутатор 52, сумматор 53 триггер 5, элементы И 55. В состав арифметико-логического блока 20 входит элемент ИЛИ 56,сумма тор 57 и триггер 5В. В состав арифметико-логического блока 21 входят сумматор 59, триггер 60, коммутатор 61, элемент НЕ 62 триггер 63, элемент И 64. Функционирование шифратора 22 определяется табл. k. Функционирование формирователя знака происходит в соответствии с табл. 5. Устройство работает следующим образом. Опишем работу вычислительной системы на примере операций типа Сложе ние-вычитание. Числа в блоке 1 памя ти хранятся в форме с плавающей запятой. Один разряд занят под знак числа, п разрядов - под порядок с его знаком, М разрядов - под мантис су. Для обработки в процессорах 6 эт числа преобразуются в следующую формулу. Из п разрядов порядка выделяется Г(( старших разрядов так, что fi 0. ( где |А| - целая част числа А. 1 Содержимое выбранных ч, разрядов будем называть октавой. Мантисса числа должна быть сдвинута влево на количество разрядов, соответствующее двоичному числу, хранящемуся в оставшихся младших « - п, разрядах порядка. Это преобразование исходной информации происходит в узле 2, откуда число, содержащее один знаковый раз-ряд, n,j разрядов октавы и .) разрядов мантиссы, передается в один из сдвиговых регистров 3. После заполнения всех сдвиговых регистров 3 начинаются сдвиги в последних. Выходящие одноименные разряды из регистров 3 записываются ячейка за ячейкой в блок k памяти. Циклы преобразования информации в узле 2 и записи ее в сдвиговые регистры 3 с последующей перезаписью в блок k памяти повторяются до тех пор, пока вся необходимая информация не окажется в блоке k памяти. Работа процессоров 6 происходит следующим образом. Из устройства управления ( не показано ) во все процессоры 6 поступает одинаковый код операции ( А+В, А-В, В-А и т.п.). Из оперативного запоминающего устрюйства считывается ячейка, хранящая знаки исходных чисел, которые поступают на первый и второй входы соответствующего процессора 6, а с этих входов - на шифратор 22. В этом узле 22 производится анализ поступившего кода операции и знаков исходных чисел и вырабатываются управляющие сигналы С Сложение или Вычитание) . Далее из блока k памяти последовательно одна за другой считываются ячейки, хранящие октавы исходных чисел (начиная с младших разрядов октав). Каждый процессор 6 получает Ьоответствующие октавы, которые nocTj пают на входы арифметико-логического блока 18, где происходит вычитание. Одновременно разряды октав вдвигаются в сдвиговые регистры 11 и 12. В результате вычитания формируются сигналы, указывающие, во-первых, какая из октав больше, этот сигнал поступает на управляющий вход коммутатора 17 для того, чтобы пропустить большую октаву из сдвигового регистра 11 или 12 в сдвиговый регистр 13. Вовторых, формируются сигналы, указывающие на равенство октав, на разность октав, равную единице и больШую единицы..

Из этих сигналов в том же блоке, 18 вырабатываются управляющие сигналы для коммутаторов 1Л и 15 одновременно.

После того, как из блока памяти последний (старший разряд октав поступил в каждом процессоре 6 на блок 18, где произошла описанная обработка, начинается чтение мантисс (тоже с младших разрядовj из блока 4 Мантиссы поступают на входы процессоров б и далее втaлкивaюtcя в сдвиговые регистры 7 и 8, имеющие 2 разрядов. После заполнения сдвиговых регистров 7 и 8 чтение мантисс из блока k продолжается, но теперь начинают работать коммутаторы 1 и 15.

В случае равенства октав через коммутаторы 1 и 15 проходит инфор- , мация из сдвиговых регистров 7 и 8. Если разность октав равна единице, мантисса, соответствующая большей октаве, проходит через коммутаторы И или 15 из сдвигового регистра 7 или, соответственно, 8, а другая мантисса проходит через коммутатор 15 или Ik по входу, связанному с входом процессора 6. Таким образом осуществляется сдвиг мантисс на раз рядов. Если разность октав больше единицы, через один из коммутаторов Н или 15 проходит мантисса, соответствующая большей октаве, в то время как другой коммутатор 15 или И закрыт.

Информация с выходов коммутаторов lit и 15 поступает на входы арифметико-логического блока 19, где ггаддействием управляющих сигналов из шиф ратора 22 происходит сложение или вычитание. В последнем случае обратный код одного из операндов формируется тоже в блоке 19. Результирующее число поступает в сдвиговый регистр 9, а после его заполнения вталкивается JU сдвиговый регистр 10. После обработки последних (старших) разрядов мантисс в арифметико-логическом блоКе 19 формируются сигналы, указывающие на то, было ли при сложении переполнение или нет, а при вычитании - на то, в каком коде (прямом или обратном )получился результат. Кроме того, срабатывает схема (не показана), которая выявляет нулевую информацию в сдвиговом регистре 9.

Сигнал переполнения из блока 19 поступает в формирователь 23 знака.

в котором на основе анализа знаков исходных чисел и кода операции ( поступают из шифратора 22) производится формирование знака результата и последующая его передача через коммутатор 16 для записи в блок k памяти.

Этот же сигнал переполнения поступает в арифметико-логический блок 20. Если в данном процессоре 6 выполняется операция сложения, в случае равенства единице сигнала переполнения в блоке 20 производится прибавление единицы к большей октаве, поступающей в блок 20 из сдвигового р егистра 13. Результирующая октава из блока 20 через коммутатор 16 передается для записи, в блок 4 памяти. Если же в результате сложения мантисс в сдвиговом регистре 9 получится нулевая информация, сработает указанная схема по обнаружению этого факта (не показана) и по её сигналу в блоке 20 произойдет вычитание единицы из октавы, поступающей из сдвигового регистра 13 В остальных случаях, (т.е. при сложении без переполнения, при вычитании, октава из сдвигового регистра 13 проходит без изменения через арифметикологический блок 20.

После окончания пересылки результирующей октавы через коммутатор 16 на чинается обработка числа, хранящегося в сдвиговых регистрах 9 и 10. Если при сложении мантисс сигнал переполнения, выработанный в арифметико-логическом блоке 19, равен нулю, результирующая мантисса из сдвиговых регистров 9 и 10 передается последовательно разряд за разрядом без изменения через блок 21 и далее через коммутатор 16 в блок k памяти. Если же этот сигнал переполнения равен единице, часть мантиссы из сдвигового регистра 9 передается в блок k памяти непосредственна через коммутатор 16, минуя блок 21. Таким образом, осуществляется нормализация мантиссы в вправо на 2 1 1-разрядов с предварительным прибавлением единицы к октаве данного результата. Сдвиговый регистр 9 имеет 2 Ц1азрядов и после того, как содержимое этого регистра 9 передано через коммутатор 16, в старшие разряды результирующей мантиссы записываются нули. Это достигается блокировкой коммутатора 1б под действием сигнала переполнения и сигнала сложения (не показано. в случае 1вычитания мантисс сигнал переполнения из блока 19 является циклическим переносом. Этот сигнал поступает в арифметико-логический блок 21, где осуществляется его сложение с мантиссой, поступающей из сдвиговых регистров 10 и 9. Этот же сигнал циклического переноса определяет в каком коде (прямом или обратном) выдается результат из блока 21 в коммутатор 16. Вычисления в процессорах 6 организованы по конвейерному принципу. Очередная пара исходных чисел начинает поступать в процессор 6 сразу же%1$ как только в него поступит последний бит предыдущих исходных чисел. Точно так же на выходе процессора 6 формируется один результат обработки за другим. Синхронизация работы составных частей процессоров 6 осуществляется общими временными строба ми от устройства управления и тригге рами задержки, входящими в узлы каждого процессора не показаны). При выполнении логических операци над исходными числами информация из блока памяти поступает на входы сдвиговых регистров 7 и 8. Далее она передается через коммутаторы I и 15 на арифметико-логический блок, где и производится необходимая логическая обработка. Результирующее чисхго через сдвиговые регистры 9 и 10 и блок 21 передается на коммутатор 16 и через него далее на выход процессора 6. Из описанного примера работы вычи лительной системы видно, каким образом достигается экономия времени при

(ич-); - (: 12 обработке информации. Преобразование чисел, представленных в форме с плавающей запятой, проведенное в узле 2 и на сдвиговых регистрах 3 позволяет упростить вычислительный процесс над числами, а именно, изъять две очень сложные процедуры выравнивания порядков ::( и связанного с этим сдвига одной из мантисс и нормализации результата с коррекцией результирующего порядка. Трудность этих процедур связана помимо аппаратурных затрат с различной временной протяженностью их выполнения в различных процессорах 6 из-за различного количества сдвигов, что затрудняет пгюцесс синхронизации вычислений во всех процессорах 6. Форма представления чисел, принятая в предложенной вычислительной системе, позволяет не только ускорить вычисления, но и упростить алгоритмы выполнения операций так, что все микрооперации в любой момент времени одинаковы для всех процессоров 6. Тем самым создается возможность убрать местное управление в процессорах 6 и управлять от общего для всех устройства управления (не показано). Следует также отметить, что обмен информацией между блоком 1 памяти и блоком памяти не требует дополнительного времени и может происходить одновременно с работой оперативного запоминающего устройства k с процессорами 6. Пока одни области блока памяти t заняты работой с процессорами 6, другие области этого блока j могут обмениваться информацией с блоком 1 памяти. Таблица1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для нормализации чисел | 1980 |

|

SU862139A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Процессор | 1984 |

|

SU1247884A1 |

о о

1 2

«1

вг

1

о о

2 о . о

13

п

nfl anti а

Ml

Ml

1 2

b V - 93828А1

продолжение табл. 1

О О О а

О О а

Таблица

Ц С«

О О О О

j.n,-tVi-1

Таблица

19

93828ti20

Прсдолжение табл. ЛТаблица 5 Формула изобретения 1. Устройство для побитовой обработки чисел, представленных в форме с плавающей запятой, содержащее N процессоров, каждый из которых содержит четыре коммутатора, четыре арифметико-логических блока, шифратор семь регистров сдвига и формирователь знака, а также общие для всех процессоров, два блока памяти, два узла коммутации и т регистров сдвига, выходы которых объединены и подключены к управляющему входу второго блока памяти вход данных которого подключен к выхо дам процессоров, выход второго блока памяти подключен к первому и второму входам каждого процессора, информационный вход первого блока памяти подключен к входу ввода устройства, третьи входы каждого процессора объединены и подключены к входу кода операции устройства, отличающееся тем, что, с целью повышения производительности, входыiT регистров сдвига объединены между собой и подключены к выходу первого узла коммутации, вход которого подключен к выходу первого блока памяти вход которого соединен с выходом второго узла коммутации, вход которого соединен с выходом второго блока памяти, а в каждом процессоре выход пер вого коммутатора подключен к выходу процессора, первый, второй, третий и четвертый входы коммутатора соедине ны с выходом формирователя знака, выходом первого арифметико-логического блока, выходом второго арифметикологического блока, выходом первого регистра сдвига и входом второго регистра сдвига, соответственно, выход которого соединен с первым информации онным входом первого арифметико-логического блока, второй информационный вход которого соединен с информационным входом формирователя знака, первым информационным входом второго арифметико-логического блока и первым выходом третьего арифметико-логического блока, второй выход которого соединен с входом первого регистра сдвига, первый информационный вход третьего арифметико-логического блока подключен к выходу второго коммутатора, а второй информационный вход - к выходу третьего коммутатора, управляющие входы второго, третьего и четвертого коммутаторов объединены и подключены к выходу четвертого арифметико-логического блока, первый информационный вход которого соединен с первым входом шифратора, входом третьего регистра сдвига, входом четвертого регистра сдвига, первым информационным входом второго коммутатора и подключен к первому входу процессора, выход третьего регистра сдвига соединен с вторым информационным входом второго коммутатора, первый информационный вход третьего коммутатора соединен с входом пятого регистра сдвига, вторым информационным входом четвертого арифметико-логического блока, входом шестого регистра сдвига, вторым входом шифратора и подключен ко второму входу процессора, выход шифратора подключен к управляющим входам первого, второго и третьего арифметико-логического блока и формирователя знака, выход пятого регистра сдвига соединен со вторым информационным входом третьего коммутатора, выходы четвертого и шестого регистров сдвига соединены с первым и вторым информационными входами четвертого коммутатора, соответственно, выход которого соединен с входом седьмого регистра сдвига, выход которого соединен с вторым информационным вхо дом второго арифметико-логического блока,

метико-логический блок содержит элемент И, сумматор, два Т1жггера, элемент НЕ и коммутатор, выход которого соединен с выходом блока, первый информационный вход коммутатора соединен со входом элемента НЕ и информационным выходом сумматора, выход переноса которого соединен с выходом первого триггера, выход которого соединен с входом переноса сумматора, первый информационный вход которого соединен с первым информационным вхо дом блока, второй у(нформационный и управляющий входы блока соединены с первым и вторым входа элемента И, соответственно, выход которого соединен с вторым информационным входом сумматора и входом второго триггера, выход которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом элемента НЕ.

ный, второй информационный и управляющий входы блока подключены к первому и второму входу элемен та ИЛИ и второму информационному входу сумматора, соответственно, выход переноса сумматора соединен со входом триггера, выход суммы сумматора соединен с выходом блока. . Устройство по п. 1, о т л и чающееся тем, что третий арифметико-логический блок содержит элемент НЕ, коммутатор, сумматор, триггер и первый и второй элементы И выходы которых подключены к первому и второму блока, соответствен-., но, первый информационный вход блока подключен к первому информационному входу коммутатора и входу элемента НЕ, выход которого соединен со вторым информационным входом коммутатора, управляющий вход которого соединен со вторым информационным входом блока и первыми входами первого и второго элементов И, соответственно, вторые входы которых объединены и подключены к выходу триггера и входу переноса сумматора, выход которого соединен со входом триггера, первый информационный

мутатора, а второй информационный вход сумматора - с управляющим входом блока.

«

«

ё 5J

сг

«41

OS

И

-

oS.

to

-

«

-

4

Е

Л

I

5f

/v/v

r

Т

Is

Т

4

ft

Я

Цикл ntftfMC

LA

f9

Mi

59

f

ISO

L4

61

-- 5Z J

Фиг.7

Авторы

Даты

1982-06-23—Публикация

1980-09-09—Подача