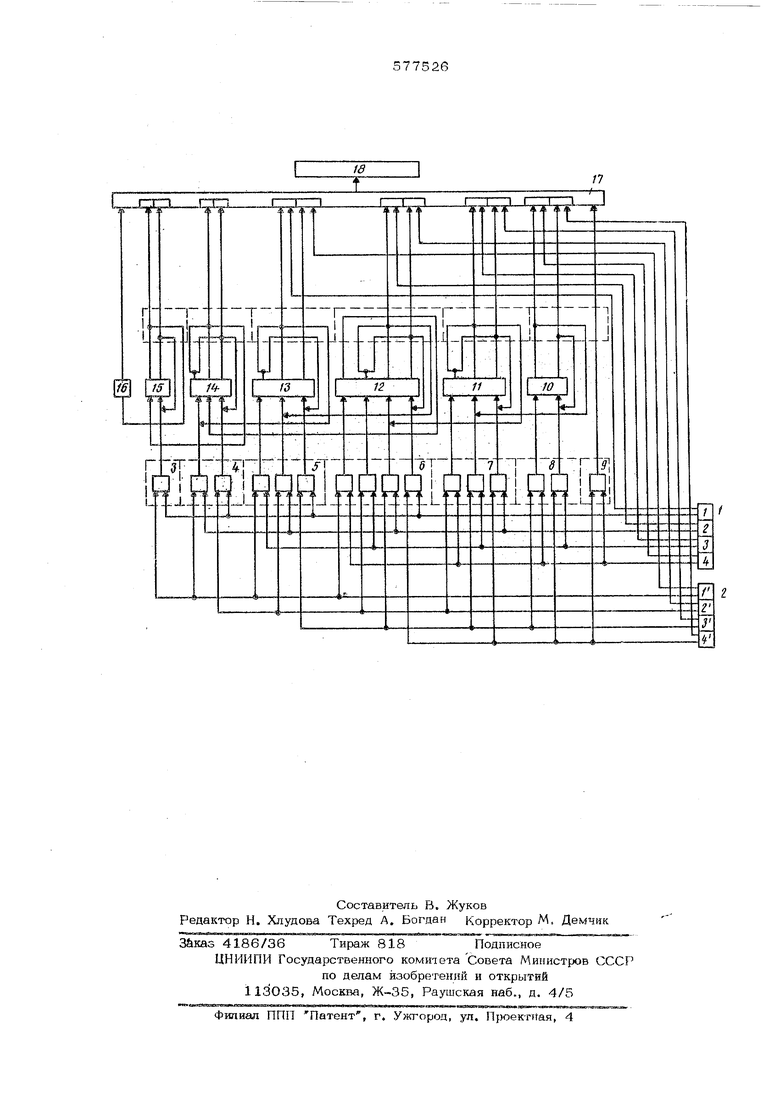

Изобретение относится к области вычислительной техники и может быть применено в арифметических устройствах ускоренного выполнения арифметических операций, в устройствах адресации, многокаиаль ной оперативной памяти, в устройствах сжатия информации, в устройствах коммутации сообщений, в устройствах микропрограммног управления. Известно арифметическое устрайсгво, ре- ализуемое на многокаскадных суммирующих схемйх для ускореннрго умножения. Оно содержит регистры множимого и множителя, выходной сумматор со сквозным переносом, блок формирования частных произведений, суммирующих схем, состоящих из нескольких параллельно последовательных каскадов трех входовых одноразрядных сумматоров, на которых частные произведения преобразовываются ь один или два слагаемых. Недостатком этого устройства является то, что при увеличении числа разрядов в сомножителях существенно возрастает число параллельно последовательных одноразрядны сумматоров, а это приводит к сниженшо быстродействия вьшолнения операций умножения, к увеличению сложности и громоздкости аппаратуры, к увеличению стоимости. Наиболее близким техническим решением к предлагаемому является уст1Х1Йство, содержащее два Vi; -{эазрядных регистра ontjрандов, порзазрядные выходы которых подкличены к первым и вторым поразрядным входам сумматора, поразрядные выходы которого подключены к поразрядным входам выходного регистра. Недостатком этого устройства является большой объем оборудования на единицу производительности и существенности задержки в сумматорах, которые приводят . к снижению быстродействия. Целью изобретения является повьпионне быстродействия выполнения арифметичогки5с операций. Это достигаетгся тем, что в устройство введены (2д-1) шифраторов (2 П -2) групп элементов И, при этом гил тазряцные выходы регистров операндов подключены к входам соответств тоших (2 ft -1) групп элементов И, выходы которь Х подключены К входам (2n-l)i шифраторов, причем вы ход элемента И младшей группы подключен к младшему; разряду сумматора, а выходы каждого t -го шифратора подключены соответственно к обш.им Ш1шам выходов t -г шифратора, где (2 П -1), при этом первая общая Ш1ша выходов каждого i -го шифратора подключена к первому поразрядному входу сумматора и к одному из входов 4 -го шифратора, вторая общая шина выходов -го шифратора подключена ко второму поразрядному входу сумматора и к одному из входов ( i -1) шифратора, третья и пт-я общие.шины выходов f -го шифратора подключены соответственно у входам (j -2))J шифраторов. . На чертеже представлена схема устройс ва, где регистры операвдов-1,25Группы элементов , шифра1Х)ры - 10-16, сумматор - 17, выходной регистр -18. Работает устройство следующим образом. Входные регистры предназначены дпя приемадвух опараидов -и передачи их в сум матор и на входы (2 Н .i) групп элементов И. В сумматор операнды перёдаюгсй при выполнении операций сложения и вьгчитанзет. На входы () групп элементов И оперзанды передаются при выполнении опе раций : умножения.,л Группа элементов И содерлсит П двухвходовых элементов И, Каждая из групп предназначена для ({юрмирования соответств ющего столбца частных произведений. , .В состав средйей группы элементов И : входит наибольшее число двухвходовых элементов И, Она равна числу разрядов одного сомножителя.На средней группе элементов И формиру , ется средний столбец частных сомножителей. Каждая последующая группа элементов ; И влево и вправо от средней формирует пос .йедующие столбцы (влево и вправо от среднего столбца) частных произведений. При этюм каждая последующая-группа элементов И влево и вправо от средней имеет на один ; элемент И меньше кажцози: предыд ей. Сумматор выполйяет операции сложения И вычитания- над двумя операндами и двух1разрядными столбцами, поступающими с вхо Ных регистров и общих шин выходов:шифрато ров, ,; .- : .. . . Вызсодной регистр служит для приема ре зультатов кодов операций из сумматора. фифраторы предназначены для преобразо вания входных единиц част1 ых произведений в двоичные коды (новые столбцы)экви валентные порядковым номерам выходов и параллельных сдвигов их на од1Ш разряд по отношению друг к другу. Арифметическое устройство содержит () шифраторов. В каждом шифраторе число входов равно числу выходов. Наибольшее число входов у среднего шифратора. Оно равно числу разрядов входного регистра. Выходам каждого шифратора присвоены порядковые номера, причем каждому из них соответствует определенное количество входных единиц. Так, например, на вход шифратора поступипо три единицы (независимо на каких шинах они находятся) - в шифраторе включается третий выход, на вход шифратора поступило две единицы - в шифраторе включится второй выход. Номера выходам калсдрго шифратора присваиваются по порядку 1,2,3.. . И . Наибольший порядковой НОМ0Р. у среднего шифратора. Он равен-Числу разрядов входного регистра. .; : С каждого выхода шифраторов на общие шины выходов считывается порядковый номер в двоичном коде. На соответствующие . общие шины выходов считываются -только едй Н1ЩЫ этих кодов, при этом значение их на общих шинах сохраняется. Число общих шин выходов каждого шифратора равно числу двоичных разрядов у наибольшего порядкового номера выхода шифратора.. По коду операции умножения с выходных {регистров 1, 2 на входы. (2 ff -1) групп элементой И 3,4,5, 6,7,8,9 одновременно рчитывается два операнда. На выходах каждой группы элементов И формируется соответствующий столбец частных произведений. Сформированные столбцы -частаых произвеДенМ одновремеййо..пеЕ№ак)Тся на входы (2tf й|::йшфратрр йй Ш г ii ., 14,15.: .../,/,,V/.... При этом мЛадшйй,Эряд элемента И крайней Правой группь передается непосредственно в младший разряд сумматора. По входным единицам столбцов частных произведений в .шифраторе арифметического устройства включается тот выход, порядковый номер jcoTOppro,соответствует количеству входных единрщ. . С включенного выхода каждого шифратора на общие шины выходов считывается порядковый номер выхода-в: Двоичном коде (первичное свертывание разрядов столбцов частных произведений). При появлении на общих шинах выходов порядковых номеров , выходов, равных трем и меньше, даль11ейшее свертывание разрядов столбцов не производится, а эти числа с общих шин выходов шифраторов снитываются непосредственно в сумматор. При поя лении на общих шинах выходов порядковых номеров выходов (двоичный код), бЬпьше трех автоматически включается процесс вто ричного свертывания количества разрядов в каждом столбце частных произведений. В процессе вторичного свертывания с общих шин выходов всех шифраторов на входы соответствующих шифраторов считываются порядковые номера включенных выходов. При атом единица младшего разряда двоичного кода с первой общей шины выходов -го шифратора считывается из входов i -го шифратора. | Единица со второй общей шины выходов i -го шифратора считывается на один из входов ( i -1) шифратора. Единица с третьей обшей шины выходов . (/ что шифратора считывается на один из входов (j -2) шифратора.и т.д. После в7орйчяо№ свертывания на общих шинах, выходов .появятся другие порядк вые номера В1ЙхоД€ Е: значительно меньше пе вых. ЕСЭТИ после Bt.QiMiHHprQ свертывания на общих шинах BkxojGiOBripHBUinJQb порядковые номера равные .трём и Меньше, то они считываются в пер;вые. и вторые порязрядные входы сумматора. Если после вторичного свертыеания на общих шинах выходов шифраторов прявились порядковые номера выходов больше трех, то автоматически выполняется третий процесс свертывания. Третий процесс свертывания выполняется аналогично первым двум Появившиеся на общих шинах выходов стблбцы (порядковые номера выходов три и меньше) из двух разрядов.считываются в сумматор. При выполнении операций сложения или вычитания оба операнда с входных регистров одновременно сч:.тываются на первые и вторые цоразряиные входы сумматора. В сумматоре выполняются соответствующие операции, результаты onejpauHfi пересылаются в выходной регистр. Таким образом, предлагаемое устреЛство, в сравнении с известным , за счет введения шифраторов и групп элементов И а также за счет организации связей в iycrp oficiee. имеет повышенное быстродействие. Формула изобретения Арифметическое устройство, содержащее два и -разрядных регистра операадов, поразрядные выходы которых подключены к первым и вторым поразрядным вхоаам сумматора, поразряавдле выходы которого поакпючены к пораз1:ядным входам ; г выходного регистра, отличающееся тем, что, с целью повышения быстродействие, в него введены (2п-1) шнф{ аторов в (2 П -1) групп элементов И, при этом поразрядные выходы регистров операндов подключены к входам соответствующих 2 И -1) групп элементов Невыходы подключены к вхоаам (2tt-2) ш)рвторов, причем выход элемента И мдадщей группы пооключен к младшему реораду сумматора, а выходы каждого I : -го й1ифратрра аодЕПючены соответcTBeHHQ кобщэ швгааи выходов j -го шиф. раторе,: где :14 4-4 (2м-1), при этом первая общая uitfflu выходов каждого { -го шифратора подключена к первому поразрядному, входу сумматора н к одному из входов I/ -fO швефратора, вторая общая шиНа выходов 4 -го шифратора подключена ко второму поразрядному входу и к одному из входов { { -1) шифратора, третья н И1 -я общие шины выходов i -го шифратора подкшочены соответственно к вхсщам ( -2 р-{Ш-Ш шифраторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1571574A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Авторы

Даты

1977-10-25—Публикация

1975-05-04—Подача